Боковой транзистор металл-оксид-полупроводник со сверхнизким удельным сопротивлением в открытом состоянии с улучшенным двойным затвором и частичным скрытым P-слоем

Аннотация

Сверхнизкое удельное сопротивление при открытии ( R on, sp ) латеральный транзистор металл-оксид-полупроводник с двойным диффузором (LDMOS) с улучшенным двойным затвором и частичным P-заглубленным слоем предлагается и исследуется в данной статье. Аналитическая модель сопротивления в открытом состоянии для предложенного LDMOS построена, чтобы обеспечить более глубокое понимание взаимосвязи между сопротивлением области дрейфа и сопротивлением области канала. Заглубленный слой N вводится под P-образным каналом, чтобы обеспечить путь проводимости с низким сопротивлением и значительно снизить сопротивление области канала. Усовершенствованная структура с двумя затворами образована слоем с N-заглублением, что позволяет избежать вертикального сквозного пробоя в выключенном состоянии. Частичный заглубленный слой P с оптимизированной длиной принят под областью N-дрейфа, чтобы расширить область вертикального истощения и ослабить пик электрического поля в закрытом состоянии, что увеличивает напряжение пробоя (BV) с низким сопротивлением области дрейфа. Для LDMOS с улучшенным двойным затвором и частичным P-заглубленным слоем результат показывает, что R on, sp составляет 8,5 мОм · мм 2 а BV - 43 В.

Фон

С увеличением спроса на более сложные и быстрые логические функции в аналоговых ИС питания, важно улучшить характеристики латерального двойного диффузионного металл-оксид-полупроводникового транзистора (LDMOS), особенно минимизируя удельное сопротивление в открытом состоянии ( R on, sp ) и максимизации напряжения пробоя в закрытом состоянии (BV) [1,2,3,4,5,6,7,8,9]. Большинство разработанных технологий сосредоточены на оптимизации области дрейфа, чтобы улучшить компромисс R on, sp по сравнению с BV для устройств LDMOS [10,11,12,13,14,15,16,17,18,19,20]. В нашей предыдущей работе был предложен LDMOS со сверхмелкой траншейной изоляцией (USTI) [21]. Глубина и угол поворота USTI были оптимизированы для достижения лучших в своем классе характеристик. Однако для низковольтного LDMOS область дрейфа теряет доминирование в R on, sp и нельзя игнорировать вклад региона канала.

Метод

В этой работе исследуется новый LDMOS со сверхнизким удельным сопротивлением в открытом состоянии с улучшенным двойным затвором и частично скрытым P-слоем. В численном моделировании используются физические модели IMPACT.I, BGN, CONMOB, FLDMOB, SRH и SRFMOB. Предлагается аналитическая модель сопротивления во включенном состоянии, чтобы обеспечить более глубокое понимание взаимосвязи между сопротивлением области дрейфа и сопротивлением области канала. На основе модели N-заглубленный слой и частично заглубленный P-слой оптимизированы для достижения низкого R on, sp и высокий BV.

Результаты и обсуждение

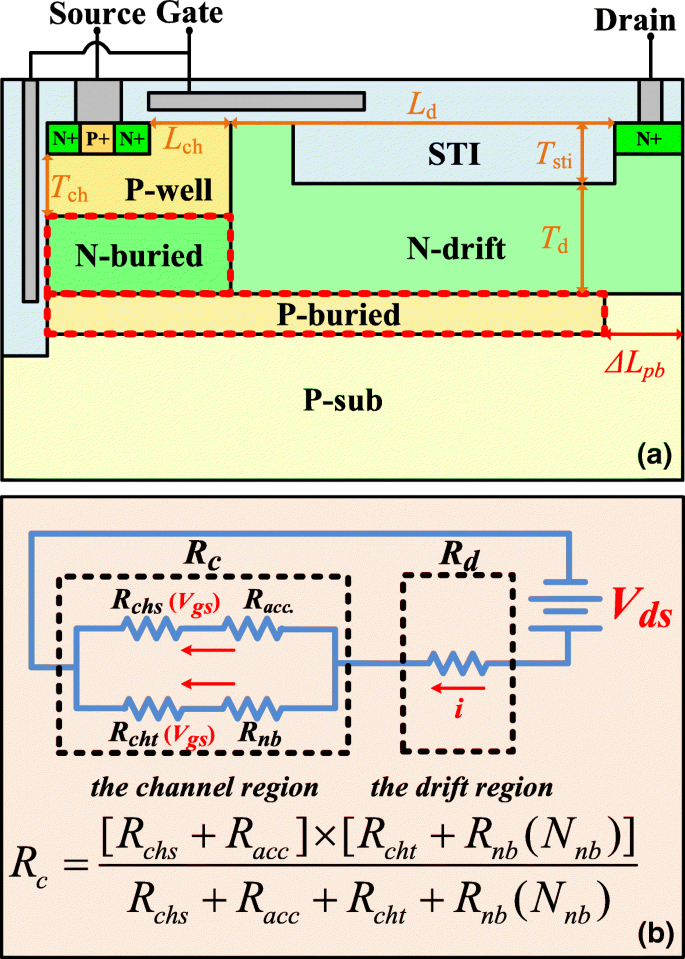

На рисунке 1а показано схематическое поперечное сечение LDMOS со сверхнизким удельным сопротивлением в открытом состоянии с улучшенным двойным затвором и частично скрытым P-слоем. LDMOS имеет двойной затвор с N-заглубленным слоем и частичный P-заглубленный слой, который способствует уменьшению R on, sp и увеличивают BV соответственно. В области канала улучшенный двойной затвор образован канавочным затвором и сильно легированным заглубленным слоем азота. По сравнению с традиционной структурой с двумя затворами, скрытый слой N значительно снижает сопротивление области канала, обеспечивая путь проводимости с низким сопротивлением в открытом состоянии под P-колодцем в открытом состоянии. В области дрейфа частично скрытый слой P с высокой концентрацией легирования вводится под областью N-дрейфа для увеличения BV при сохранении низкого R on, sp . Частично скрытый слой P помогает уменьшить вертикальное электрическое поле в выключенном состоянии без нарушения баланса заряда в области дрейфа. Размер ключа нового устройства указан в таблице 1.

а Схематический вид в разрезе LDMOS со сверхнизким удельным сопротивлением в открытом состоянии с улучшенным двойным затвором и частично скрытым P-слоем. б Схематический эквивалент открытого сопротивления для предлагаемого LDMOS

На рисунке 1b показана схематическая эквивалентная модель сопротивления в открытом состоянии для предложенного LDMOS. Общее сопротивление в открытом состоянии рассматривается как сопротивление области дрейфа ( R d ) и сопротивление области канала ( R c ) последовательно. В области канала путь проводимости поверхностного канала параллелен пути проводимости канала траншеи. Таким образом, R c равно ( R chs + R acc ) // ( R cht + R nb ), где R chs , R acc , R cht , и R nb - сопротивления канала с поверхностным затвором, области накопления, канала затвора траншеи и заглубленного слоя N соответственно. На основе предложенной модели сопротивления при включении уменьшение R c будет достигнуто за счет уменьшения R nb не влияя на другие характеристики, поскольку другие сопротивления в основном определяются технологическим процессом, рабочим напряжением и пороговым напряжением. R d был уменьшен за счет введения P-скрытого слоя под N-дрейфовой областью для усиления эффекта уменьшения поверхностного поля (RESURF) в нашей предыдущей работе. В этой работе частичный заглубленный P слой принят для улучшения BV при сохранении низкого R d .

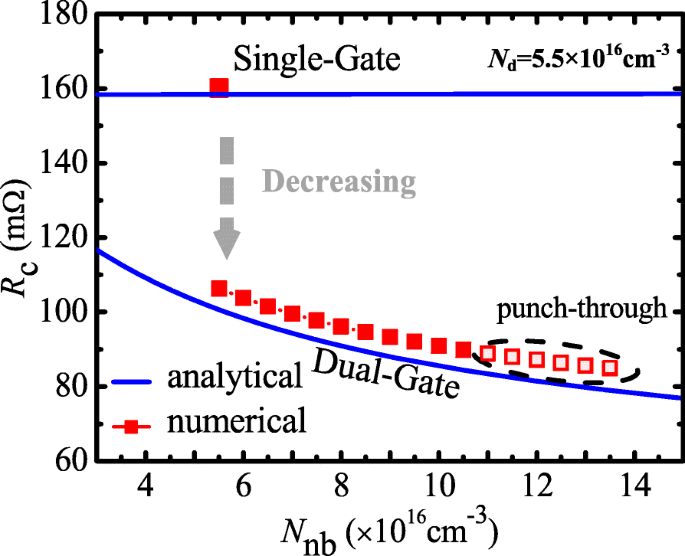

Стремясь снизить R c , N-заглубленный слой с высокой концентрацией легирования вводится под P-лунку. На рисунке 2 показаны числовые и аналитические R . c как функции концентрации легирования в скрытом N-слое ( N nb ) с одностворчатым и двойным затвором. Указывается, что двойная вентильная структура помогает уменьшить R c по сравнению с одностворчатым. Когда N nb = N d =5,5 × 10 16 см −3 , R c составляет 110 мОм. Согласно модели сопротивления при включении, R nb является основным участником R c . А затем R nb желательно уменьшить с целью уменьшения R c . Как показано на рис. 2a, R c сокращается на N nb увеличивается. Когда N nb =1,35 × 10 17 см −3 , R c снижается до 85 мОм. Однако на рис. 2 также показано, что N nb будет ограничено пробивкой насквозь. Из-за добавления траншейных ворот R c уменьшается сначала на 34% с N nb = N d =5,5 × 10 16 см −3 . Как N nb увеличивается, R c непрерывно уменьшается. С оптимизированным N nb =1,05 × 10 17 см −3 , R c уменьшился наконец на 45%. Когда N nb > 1,05 × 10 17 см −3 , пробой произойдет в P-колодце. Аналитический результат R on, sp Показанная на рис. 2 показывает, что предложенная модель хорошо согласуется с результатами численного моделирования. Следовательно, модель является правдоподобной для руководства при разработке оптимизации.

Числовой и аналитический R c как функция от N nb с одинарным и двойным вентилем ( Z =1 см). N d - концентрация легирования в области N-дрейфа

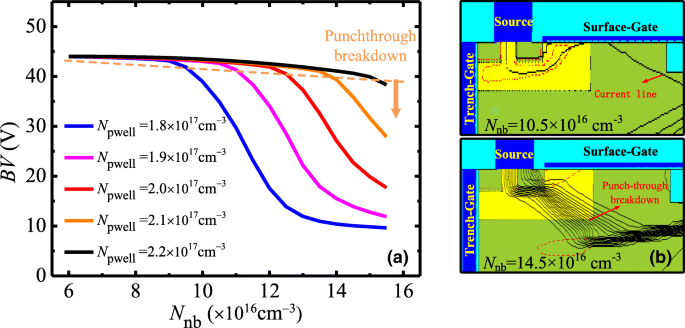

На рисунке 3a показано числовое значение BV как функция от N . nb с разной концентрацией легирования P-well ( N pwell ). N nb влияет не только на R c , но и BV. Для заданного N pwell , BV остается без изменений при малых N nb , а затем уменьшается на N nb увеличивается. Когда N nb увеличивается до 1,2 × 10 17 см −3 , BV начинает падать с N pwell =2 × 10 17 см −3 . Падение BV приписывается пробою в области P-лунки, как показано на рис. 3b. По мере увеличения напряжения стока область истощения в P-колодце расширяется до истока. Когда область истощения атакует соединение N + / P-скважины, происходит пробой сквозного пробоя. Для большого N pwell , обеднение в основном распространяется на область дрейфа, и пробой пробоя избегают без ухудшения BV. Хотя P-колодец с высокой концентрацией легирования позволяет избежать сквозного пробоя, он может повысить пороговое напряжение. Таким образом, N pwell из 2 × 10 17 см −3 выбирается с учетом порогового напряжения и компромисса между BV и R on, sp .

а Числовой BV как функция от N nb с разными N pwell . б Профиль плотности тока для N nb =10,5 × 10 16 см −3 и 14,5 × 10 16 см −3 пока N pwell =2 × 10 17 см −3 при поломке

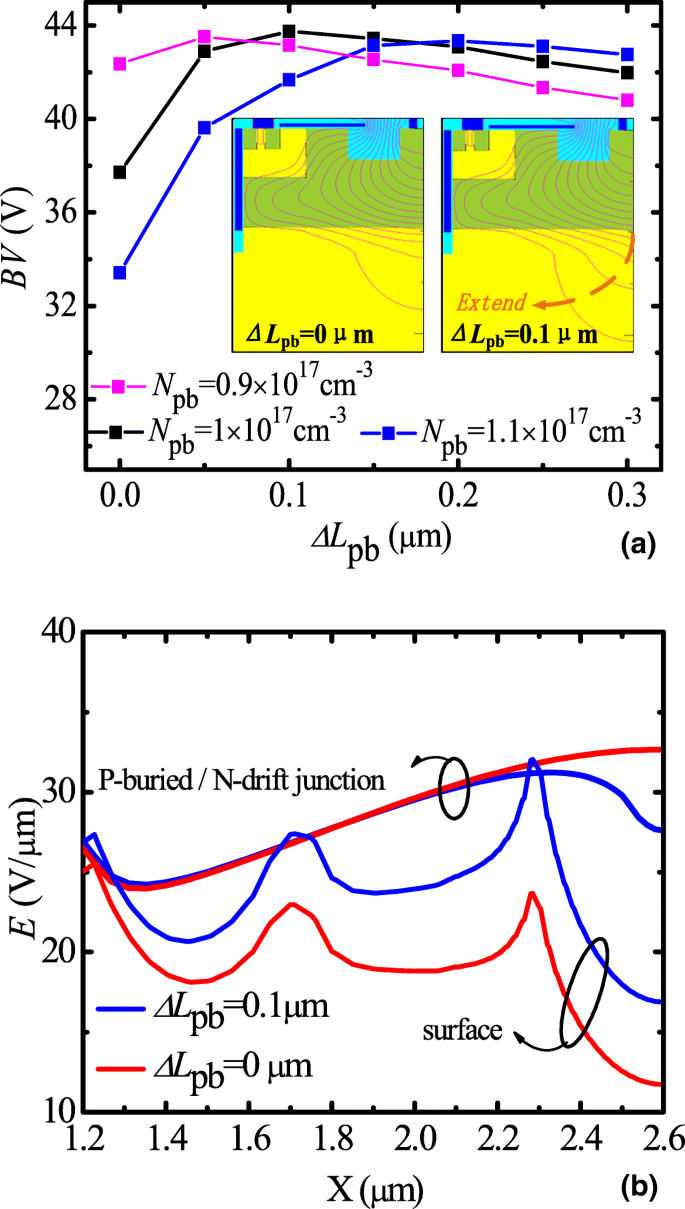

Для достижения низкого R d и с высоким BV, частичный заглубленный слой P вводится под областью N-дрейфа. На рисунке 4а показана зависимость BV от Δ L . pb с разными N pb . Для заданного N pb , как Δ L pb увеличивается, BV увеличивается, а затем немного уменьшается. Когда Δ L pb =0,1 мкм, N pb =1 × 10 17 см −3 , BV достигает максимального значения 43 В. На вставке показан профиль эквипотенциального контура с N pb =1 × 10 17 см −3 . Показано, что эквипотенциальный контур в структуре частичного заглубленного P-слоя простирается больше на подложку по сравнению с полным P-заглубленным слоем. На рис. 4b показано распределение электрического поля на поверхности и на границе раздела P-заглубленный / N-дрейфовый. Для оптимизированного обычного LDMOS пробой обычно происходит на границе раздела N-дрейф / P-заглубленный. Для предлагаемого LDMOS соединение N-дрейф / P-sub заменяет соединение N-дрейф / P-заглубленный, чтобы ослабить вертикальное электрическое поле и расширить область истощения, что приводит к более высокому BV при сохранении низкого R d .

а BV как функция от ΔL pb с разными N pb . Вставка представляет собой профиль эквипотенциального контура с N pb =1 × 10 17 см −3 . б Распределение электрического поля на поверхности и на границе раздела P-заглубленный / N-дрейфовый

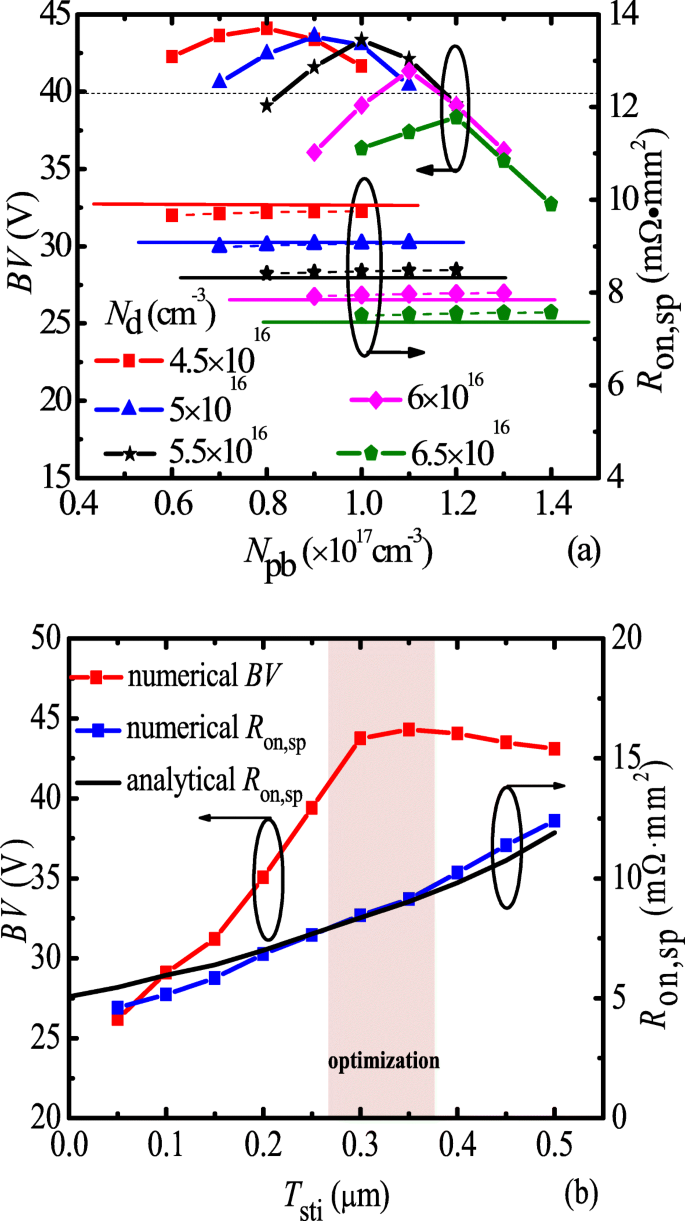

Для достижения высокого BV требуется баланс заряда между N-дрейфом и частичным заглубленным P-слоем. На рисунке 5a показано, что числовые и аналитические BV и R on, sp в зависимости от концентрации допирования в скрытом фосфоре ( N pb ) для разных N d . Для заданного N d , BV имеет максимальное значение при различных N pb , и максимум BV увеличивается с уменьшением N d . Однако R on, sp можно увеличить как N d уменьшается. Благодаря BV требуется более 40 В, N d =5,5 × 10 16 см −3 и N pb =1 × 10 17 см −3 выбраны. На рисунке 5b показаны числовые и аналитические BV и R . on, sp как функции толщины слоя STI ( T sti ). Т sti оказывает сильное влияние на BV и R on, sp , и он должен быть тщательно спроектирован и оптимизирован, как и наша предыдущая работа [21]. Для T sti <0,3 мкм в месте пробоя под краем полнопольной пластинки наблюдается высокий пик электрического поля. Как T sti увеличивается, пик электрического поля релаксирует, а затем BV увеличивается. Для T sti =0,3 мкм, получается BV 43 В. Для T sti ≥ 0,3 мкм, пик электрического поля под краем полуполевой пластины достаточно низкий, в результате точка пробоя переходит на P / N переход под стороной стока. Как T sti увеличивается, BV увеличивается, а затем насыщается.

а Числовые (пунктирная линия) и аналитические (сплошная линия) BV и R on, sp как функции от N pb для разных N d . б Числовые (пунктирная линия) и аналитические (сплошная линия) BV и R on, sp как функции от T sti

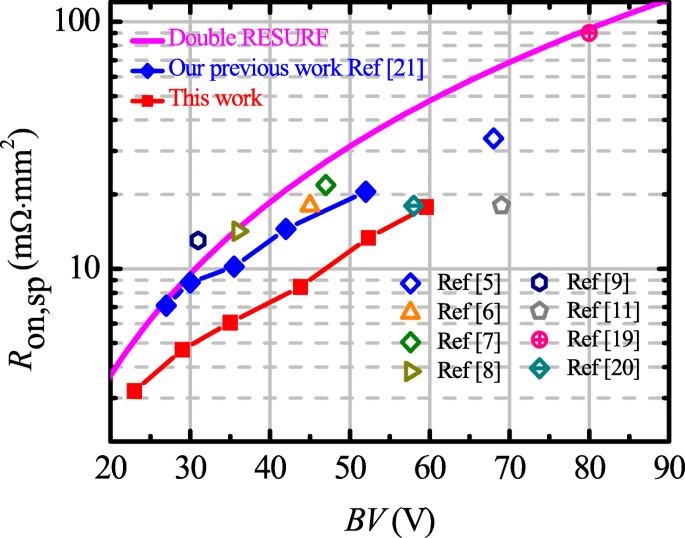

На рисунке 6 показан тест существующих технологий биполярного CMOS-DMOS (BCD) и предлагаемого LDMOS. Очевидно, технологический процесс для предлагаемого LDMOS совместим с разработанной нами технологией BCD, которая обеспечивает лучшую в своем классе производительность LDMOS. В процессе изготовления предлагаемого LDMOS слой с N-заглублением может иметь ту же маску, что и P-well. Для предлагаемого LDMOS, R on, sp составляет 8,5 мОм · мм 2 а BV =43 В, что примерно на 37% меньше, чем в нашей предыдущей работе.

Тест существующих технологий BCD и предлагаемого LDMOS

Заключение

Новый LDMOS со сверхнизким удельным сопротивлением в открытом состоянии с улучшенным двойным затвором и частичным заглубленным слоем P предлагается и исследуется с помощью численного моделирования в этой статье. Скрытый N-слой с высокой концентрацией легирования используется для достижения улучшенного двойного затвора с уменьшением R c . Частично скрытый слой P вводится под областью N-дрейфа для увеличения BV с сохранением начисленного баланса. Процесс изготовления LDMOS в этой работе совместим с существующей технологией BCD, описанной в нашей предыдущей работе. Результат показывает, что R on, sp предлагаемого LDMOS уменьшается на 37% при BV 43 В по сравнению с предыдущими работами. Поскольку технология обработки полупроводников выходит на нанометровый уровень, R on, sp может еще больше уменьшиться с уменьшением длины канала.

Сокращения

- BCD:

-

Биполярный-CMOS-DMOS

- BV:

-

Напряжение пробоя

- LDMOS:

-

Боковой двухдиффузионный транзистор металл-оксид-полупроводник

- RESURF:

-

Уменьшить поверхностное поле

- R on, sp :

-

Удельное сопротивление при включении

- USTI:

-

Изоляция сверхмалых траншей

Наноматериалы

- Нановолокна и нити для улучшенной доставки лекарств

- Межфазные, электрические характеристики и характеристики совмещения полос стопок HfO2 / Ge с прослойкой SiO2, сфор…

- Новый фотокатализатор на гетеропереходе Bi4Ti3O12 / Ag3PO4 с улучшенными фотокаталитическими характеристиками

- Влияние повышенной термической стабильности опорного слоя из оксида алюминия на рост вертикально ориентиро…

- Влияние наночастиц Ag разного размера и концентрации, внедренных в компактный слой TiO2, на эффективность преоб…

- Антипролиферативный и запускающий апоптоз потенциал целевых липидных наночастиц на основе паклитаксела с у…

- Всенаправленный поглотитель за счет эффекта плазмона пустоты в видимой области со значительно усиленным лок…

- Полевой транзистор SnSe2 с высоким коэффициентом включения / выключения и переключаемой полярностью фотопрово…

- Наномембраны TiO2, изготовленные осаждением атомного слоя для электрода суперконденсатора с увеличенной емко…

- Пористые нанолисты ZnO с частичной модификацией поверхности для улучшенного разделения зарядов и высокой фот…