Об улучшении характеристик (BFOM) Baliga нового GaN-наностолбика с вертикальным полевым транзистором (FET) с каналом 2DEG и Узорчатый субстрат

Аннотация

Новый вертикальный полевой GaN-транзистор (FET) с улучшенным режимом работы и 2DEG для уменьшения сопротивления в открытом состоянии ( R ВКЛ ) и рисунок подложки (SP) для повышения напряжения пробоя (BV) предлагается в данной работе. Сознательно разработав ширину и высоту SP, можно разделить сильное концентрированное электрическое поле (E-field) под крышкой p-GaN без значительного воздействия на R ВКЛ , создавая улучшенный образец достоинств Балиги (BFOM, BV 2 / R ВКЛ ). Проверенное экспериментально откалиброванным моделированием ATLAS, предлагаемое устройство с SP длиной 700 нм и шириной 4,6 мкм имеет в шесть раз более высокую BFOM по сравнению с полевым транзистором без узорчатой подложки. Кроме того, предлагаемое опорное устройство и SP внутри занимают лишь наноразмерную область, что позволяет интегрировать такие устройства с высокой плотностью, что обеспечивает их высокий потенциал в будущих энергетических приложениях.

Фон

В настоящее время полупроводники с широкой запрещенной зоной, такие как ZnO, In 2 О 3 , SiC и нитрид галлия (GaN) привлекли внимание [1,2,3,4,5]. Принимая во внимание, что, учитывая электронные свойства, боковой транзистор с высокой подвижностью электронов (HEMT) AlGaN / GaN широко рассматривается как потенциальный кандидат для замены устройства на основе Si в силовых или частотных приложениях из-за более высокого напряжения пробоя (BV), а также более сильная термическая стабильность. Много усилий, таких как крышка p-типа [6, 7], имплантация ионов фтора [8, 9], тонкий барьер [10, 11], двойной канал [5, 12] и полевой затвор [13] , были сделаны на реализации HEMT улучшенного типа, который желательно упростить схему драйвера.

Однако эти технологии сталкиваются с множеством серьезных проблем, таких как низкая однородность порогового напряжения, нерациональное использование вертикальной площади микросхемы, падение тока, ограниченный показатель достоинств Балиги (BFOM) и т. Д. В частности, противоречие между длиной дрейфа и BV отрицательно влияет на масштабирование устройства [14, 15]. Другими словами, меньшее устройство приводит к более низкому BV, при котором сложнее использовать соединительные клеммы, которые способствуют BFOM, оптимизируя распределение электрического поля. С этой целью были предложены задний барьер [16], скрытый переход [17], полевая пластина с квантовыми ямами [18] и другие структуры, которые вставляются в боковой HEMT и демонстрируют особенность пластинки электрического поля для увеличения BV за счет использования вертикальная область чипа.

С другой стороны, в силу превосходной природы GaN, объемный GaN-транзистор с вертикальным полевым эффектом (VFET) привлекает все больше и больше внимания из-за более простой реализации функций улучшенного типа и полного использования вертикальной области [19 , 20,21,22]. Многие новые конструкции представлены в экспериментах или моделировании для наклона BV и одновременного снижения сопротивления в открытом состоянии ( R ВКЛ ) [23,24,25]. Однако, не говоря уже о трудностях изготовления суперперехода (SJ) в GaN, отсутствие высокоподвижного двумерного электронного газа (2DEG) приводит к более высокому R ВКЛ [26], что затрудняет оптимизацию BFOM в таких устройствах.

В этой работе описан новый вертикальный полевой транзистор на основе GaN с 2DEG для уменьшения R ВКЛ и предлагается шаблон подложки (SP) для улучшения BV, в котором комбинация канала 2DEG и SP эффективно уравновешивает противоречие между низким сопротивлением в открытом состоянии и высоким BV. Кроме того, предлагаемая опора устройства и SP внутри занимают лишь наноразмерную область, что позволяет интегрировать такие устройства с высокой плотностью. Проверенное численным моделированием в ATLAS, предлагаемое устройство имеет более высокий BFOM по сравнению с тем же полевым транзистором (FET) без узорчатой подложки, что обеспечивает его высокий потенциал в будущих приложениях питания.

Метод

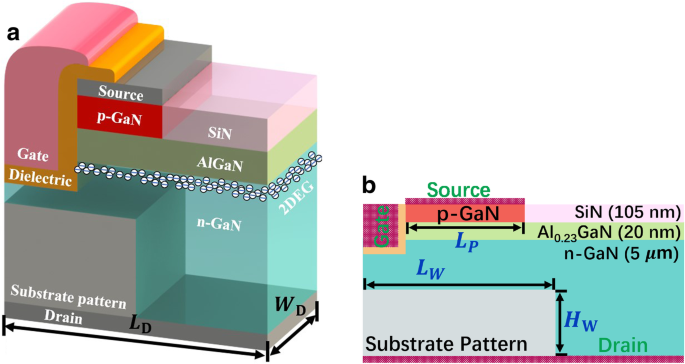

Предлагаемое устройство генерируется в нормальном Al 0,23 Пластина GaN / GaN с высококонцентрированной подложкой n-типа, действующей как электрод стока, как показано на рис. 1а, где толщина слоя нитрида кремния (SiN), AlGaN и GaN составляет 105 нм, 20 нм и 5 мкм. , соответственно. GaN n-типа с 2 × 10 16 см −3 допинг n D и колпачок из GaN p-типа с 2 × 10 17 см −3 допинг n A устанавливается как буферный и составной канал соответственно [27, 28]. Другой компонент канала рядом с затвором - тонкий слой AlGaN, который вводят для индукции 2DEG, как показано на рис. 1b. СП, изготовленный из оксида алюминия (Al 2 О 3 ), например, в этой статье, выращивается на субстрате.

Схема а 3D опорная конструкция и b поперечное сечение с обозначенными геометрическими параметрами предлагаемого SP-VFET

Таким образом, все устройство может быть изготовлено стандартным процессом последовательно:(1) эпитаксиальным осаждением проводящей подложки и интегрированного SP-слоя, (2) частичным травлением SP-рисунка, (3) нанесением и полировкой n- Буфер GaN, (4) нанесение барьера из AlGaN и крышки p-GaN, и (5) изготовление электродов и пассивация.

Имплантированный имитатор ATLAS откалиброван по экспериментальным данным HEMT улучшенного типа с p-GaN cap [29, 30]. Калиброванные и другие характеристики устройства приведены в таблице 1. Другие конфигурации можно найти в нашей предыдущей работе [31]. Тип и плотность интерфейсной ловушки, расположенной на границе раздела SP / GaN, относятся к экспериментальным измерениям на основе емкости [32,33,34]. Поляризационный заряд на поверхности AlGaN / GaN подтверждается согласно соответствующему простому квадратному уравнению подгонки [35].

Физический механизм

Во включенном состоянии, по сравнению с устройством без канала 2-DEG и SP, предлагаемый вертикальный полевой транзистор с рисунком подложки (SP-VFET) имеет высокопроводящий путь благодаря 2-DEG и более узкому вертикальному каналу тока. это уменьшает проводимость, как показано на рис. 2. В частности, благодаря 2DEG высокой плотности, сконцентрированному на границе раздела AlGaN / GaN, боковой путь прохождения тока может поддерживаться, что частично компенсирует проводимость всего устройства. Напротив, на текущие транспортные возможности устройства SP-VFET без канала 2DEG это сильно повлияет.

Схематическое изображение прямого течения тока в a устройство без SP, b предлагаемый SP-VFET с коротким SP, и c длинный SP

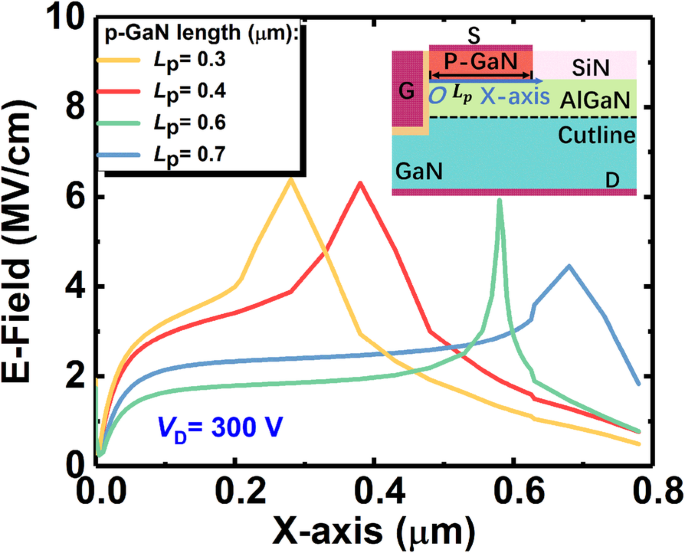

Длина крышки p-GaN не будет сильно влиять на концентрацию электрического поля (E-field) до тех пор, пока длина не станет больше 700 нм, на которую p-GaN почти не покроет всю поверхность устройства. Как показано на рис. 3, распределение E-поля вдоль границы раздела AlGaN / GaN имеет пик в правом углу p-GaN. Положение пика смещается вместе с изменяющейся длиной p-GaN, но остается на том же уровне. Небольшую разницу в пиковом значении можно увидеть на рис. 3, когда колпачок p-GaN длиннее 600 нм, потому что длинный колпачок p-GaN сглаживает все E-поле в устройстве и тем самым увеличивает сопротивление устройства из-за к истощению 2DEG.

Распределение электрического поля устройства без ПП вдоль гетероперехода AlGaN / GaN при разной длине p-GaN

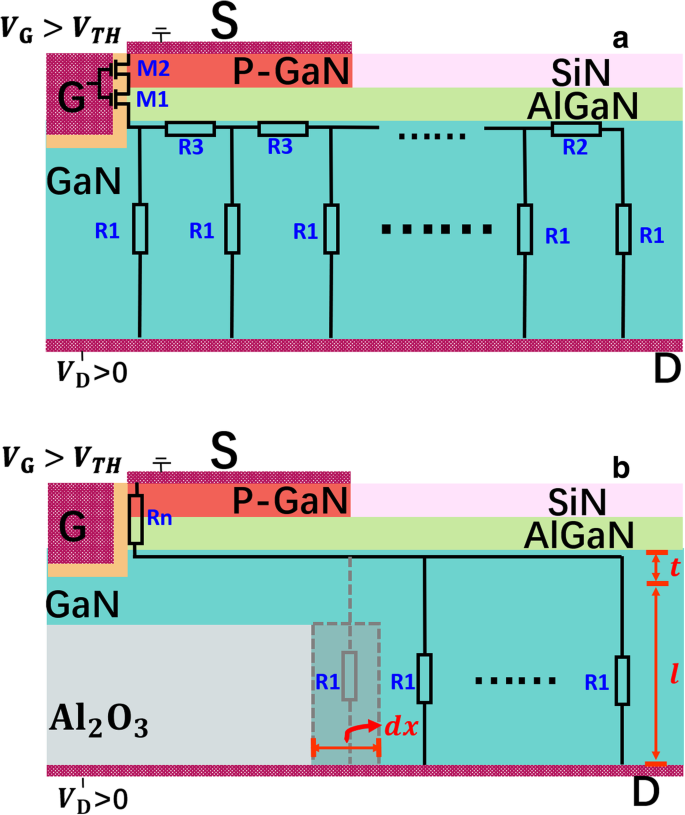

Чтобы проиллюстрировать влияние одновременно введенных p-GaN, 2-DEG и SP, можно построить модель проводимости в открытом состоянии, как схематично показано на рис. 4a. M 1 и M 2 представляют собой МДП-подобные транзисторы с проводящим каналом, сформированным в p-GaN и AlGaN соответственно. R 1 представляет собой бесконечно малую часть вертикального сопротивления в массивном GaN. R 2 и R 3 представляют собой бесконечно малые части сопротивления 2-градусного канала с частичным истощением и без него, соответственно. Согласно закону сопротивления, R 1 , R 2 , и R 3 можно получить как

$$ {R} _1 =\ frac {1} {n_1 q \ mu} \ bullet \ frac {l} {dx \ bullet {W} _D} $$$$ {R} _2 =\ frac {1} {n_2 q \ mu} \ bullet \ frac {dx} {t \ bullet {W} _D} $$$$ {R} _3 =\ frac {1} {n_3 q \ mu} \ bullet \ frac {dx} {t \ пуля {W} _D} $$где n 1 , n 2 , и n 3 представляют собой электрическую концентрацию в GaN, обедненном 2-DEG и обедненном 2-DEG соответственно; q - заряд электрона и μ - подвижность электрона в GaN; l - длина вертикального токопроводящего пути и dx бесконечно малая длина в горизонте; Вт Д ширина устройства; и t это толщина 2-ГРАДУСОВ. Для удобства t устанавливается равным 10 нм [7]. Концентрация обедненного 2-DEG в p-GaN n 3 равняется невыполненной концентрации n 1 минус общий отрицательный заряд в обедненном p-GaN [31], который читается как

$$ {n} _3 ={n} _2- {n} _A {x} _D $$

Схема а предложенная государственная модель без SP b модель сети сопротивления в открытом состоянии с SP

Ограничение p-GaN можно рассматривать как полностью истощенное, поэтому x Д равна 105 нм, толщина p-GaN. По сравнению с R 1 , R 2 и R 3 намного ниже, чем R 1 , из-за более высокой концентрации электронов и более короткого проводящего пути. Следовательно, сопротивлением в канале 2 ГРАДУСКА можно пренебречь. Кроме того, когда напряжение на стоке небольшое и МДП-подобные транзисторы M 1 и M 2 работают в ненасыщенной модели, сопротивление в открытом состоянии M 1 и M 2 можно рассматривать как игнорируемое постоянное сопротивление R n . Чтобы упростить расчет, аналитическая форма проводимости вертикального пути тока G v вертикального пути тока можно получить как

$$ {G} _v ={\ int} _0 ^ {L_D} \ frac {1} {R_1} ={\ int} _0 ^ {L_D} {n} _1 q \ mu \ bullet \ frac {dx \ bullet { W} _D} {l} $$где L D длина устройства.

Следовательно, сопротивление в открытом состоянии R на можно получить, что гласит

$$ {R} _ {on} =\ frac {1} {G_v} + {R} _n =\ frac {1} {n_1 q \ mu} \ bullet \ frac {l} {L_D \ bullet {W} _D } + {R} _n $$Когда SP существует, как показано на рис. 4b, вертикальный токопроводящий путь частично заблокирован. Таким образом, проводимость вертикального пути тока можно выразить как

$$ {G} _v ={\ int} _ {L_W} ^ {L _ {\ mathrm {D}}} \ frac {1} {R_1} ={\ int} _ {L_W} ^ {L_D} {n} _1 q \ mu \ bullet \ frac {dx \ bullet {W} _D} {l} $$где L Вт длина SP.

Следовательно, соответствующий R на можно выразить как

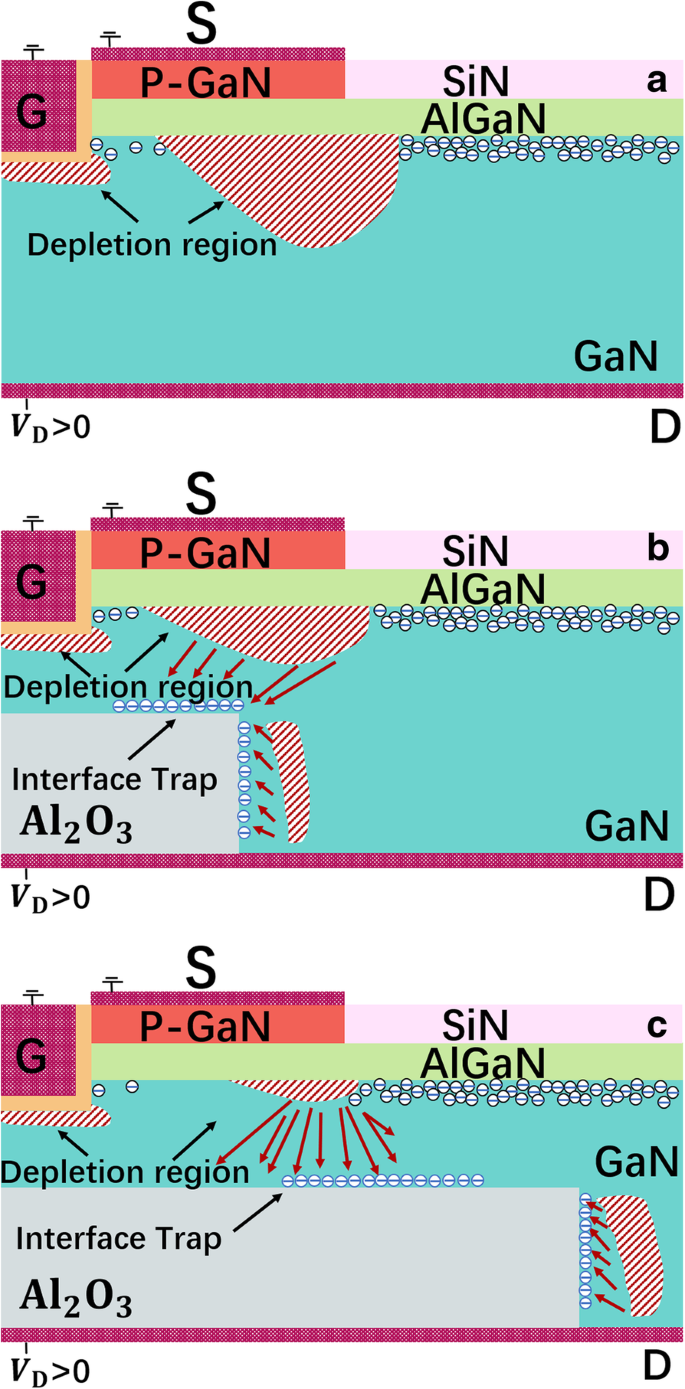

$$ {R} _ {on} =\ frac {1} {G_v} + {R} _n =\ frac {1} {n_1 q \ mu} \ bullet \ frac {l} {\ left ({L} _D - {L} _W \ right) \ bullet {W} _D} + {R} _n $$В выключенном состоянии, из-за функциональности конденсатора и отрицательно заряженной граничной ловушки, SP будет эффективно перераспределять электрическое поле под крышкой p-GaN, создавая концентрацию поля вокруг SP, которая имеет более широкую запрещенную зону, как показано на Рис. 5. Такое перераспределение электрического поля сжимает область истощения, которая появляется вокруг p-GaN и затвора, и тем самым снимает высокую концентрацию поля вокруг крышки p-GaN и затвора, что увеличивает BV SP-VFET. замечательно. С другой стороны, как упоминалось выше, SP будет влиять на проводимость устройства, так что отрицательный заряд, вносимый SP, приводит к увеличению потенциальной энергии около затвора, что составляет уменьшение 2-DEG около затвора. В результате может быть достигнута непостоянная BFOM с изменением длины и высоты SP.

Схематическое распределение электрического поля и обедненной области в а устройство без SP, b предлагаемый SP-VFET с коротким SP, и c предлагаемый SP-VFET с длинным SP

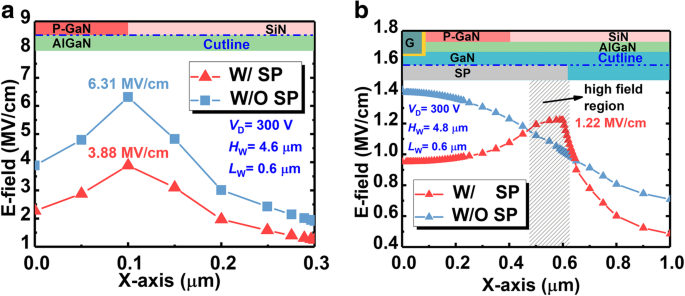

Другими словами, SP может уменьшить пик E-поля вокруг угла p-GaN и одновременно привлечь E-поле, концентрирующееся через SP, как показано на рис. 6a, b. Однако благодаря более высокому критическому E-полю SP, такая концентрация E-поля не сломает устройство, в результате чего SP-VFET будет демонстрировать гораздо более высокий BV.

Распределение электрического поля предлагаемого SP-VFET вдоль границы раздела a p-GaN / AlGaN и b GaN / SP

Результат и обсуждение

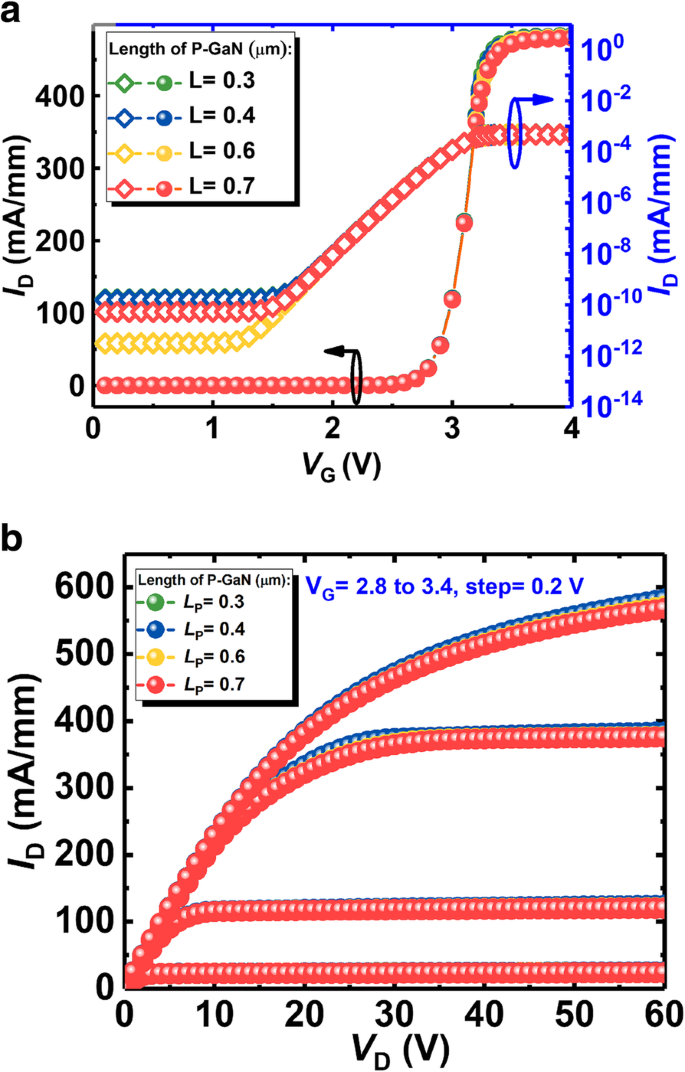

На рис. 7а, б показаны соответственно передаточная и выходная кривые предлагаемого устройства без ИП. При разной длине крышки p-GaN эти кривые накладываются друг на друга как в подпороговом режиме, так и в режиме включения, предполагая, что длина крышки p-GaN не влияет на проводимость устройства без SP. Другими словами, хотя колпачок p-GaN будет частично истощать 2-градусный канал и тем самым влиять на сопротивление канала 2-градуса, оставшийся 2-градусный канал все еще имеет большую концентрацию n 3 что приблизительно соответствует невыполненной концентрации n 2 , который реализуется за счет оптимизации концентрации p-типа в p-GaN cap. Кроме того, как было проанализировано ранее, сопротивление канала 2-DEG довольно мало по сравнению с сопротивлением n-GaN на вертикальном пути. Следовательно, на рис. 7а, б кривые переноса накладываются друг на друга. Однако, чтобы защитить затвор от высококонцентрированного электрического поля, такое скопление не должно примыкать к затвору, что означает, что длина p-GaN не может быть слишком короткой. Таким образом, минимальная длина p-GaN в нашей работе составляет 400 нм, если не указано иное.

а Передаточные кривые и b выходные кривые устройства без ИП при разной длине колпачка из p-GaN

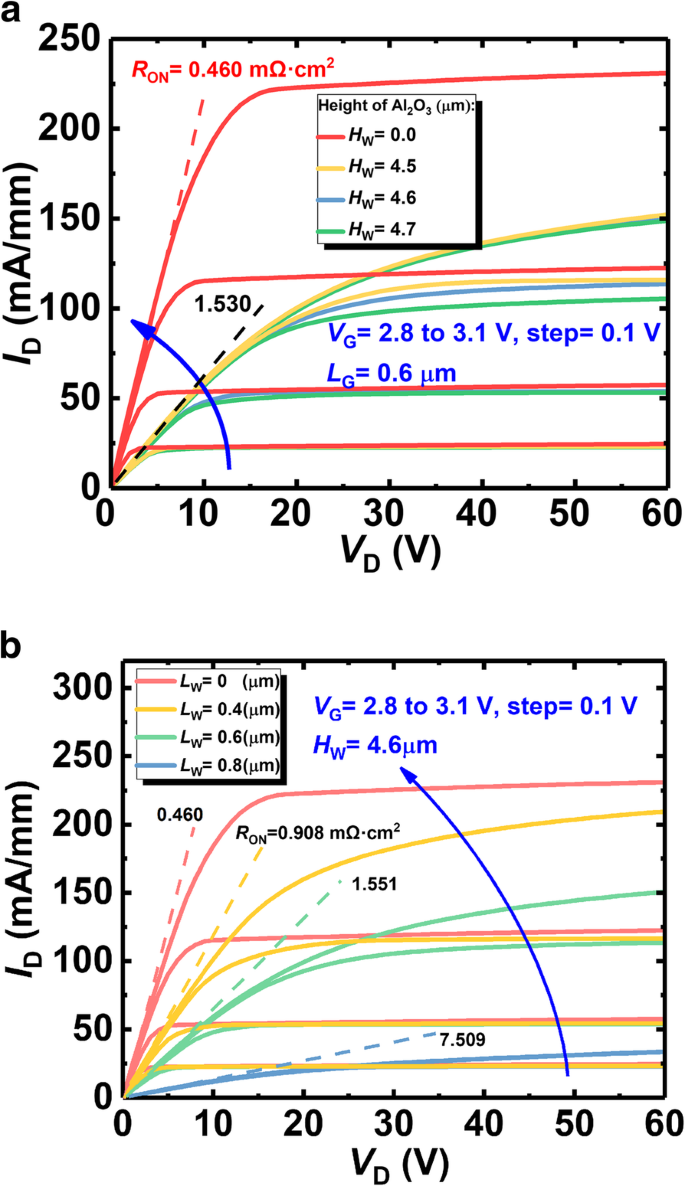

На рисунке 8 показаны выходные характеристики предлагаемых SP-VFET и VFET без SP. Можно видеть, что SP действительно оказывает сопротивление устройства, сужая вертикальный канал проводимости. В частности, сопротивление в открытом состоянии не зависит от высоты SP, когда высота меньше 4,7 мкм, в то время как существенно зависит от длины SP, которая соответствует механизму, который узкий вертикальный путь тока уменьшает проводимость. Первая независимость заключается в том, что 2DEG является основным боковым каналом проводимости, который не будет ослаблен SP в пределах своей умеренной высоты. Однако, если SP находится рядом с каналом 2-DEG, введенный отрицательный заряд вокруг SP будет выравнивать энергетический диапазон, что приводит к резкому снижению концентрации 2-DEG. Следовательно, сопротивление 2-DEG увеличивается, и общее сопротивление в открытом состоянии R на соответственно увеличивается. Кроме того, более поздняя зависимость проистекает из заметно увеличенного сопротивления в вертикальном канале, как упоминалось выше. Кроме того, следует отметить, что дефекты решетки в 2-градусной диаграмме, вызванные высоким SP, ограничивают высоту SP.

Выходные кривые предлагаемого SP-VFET с изменяющимся a Ширина SP и b Длина ИП по сравнению с устройством без ИП

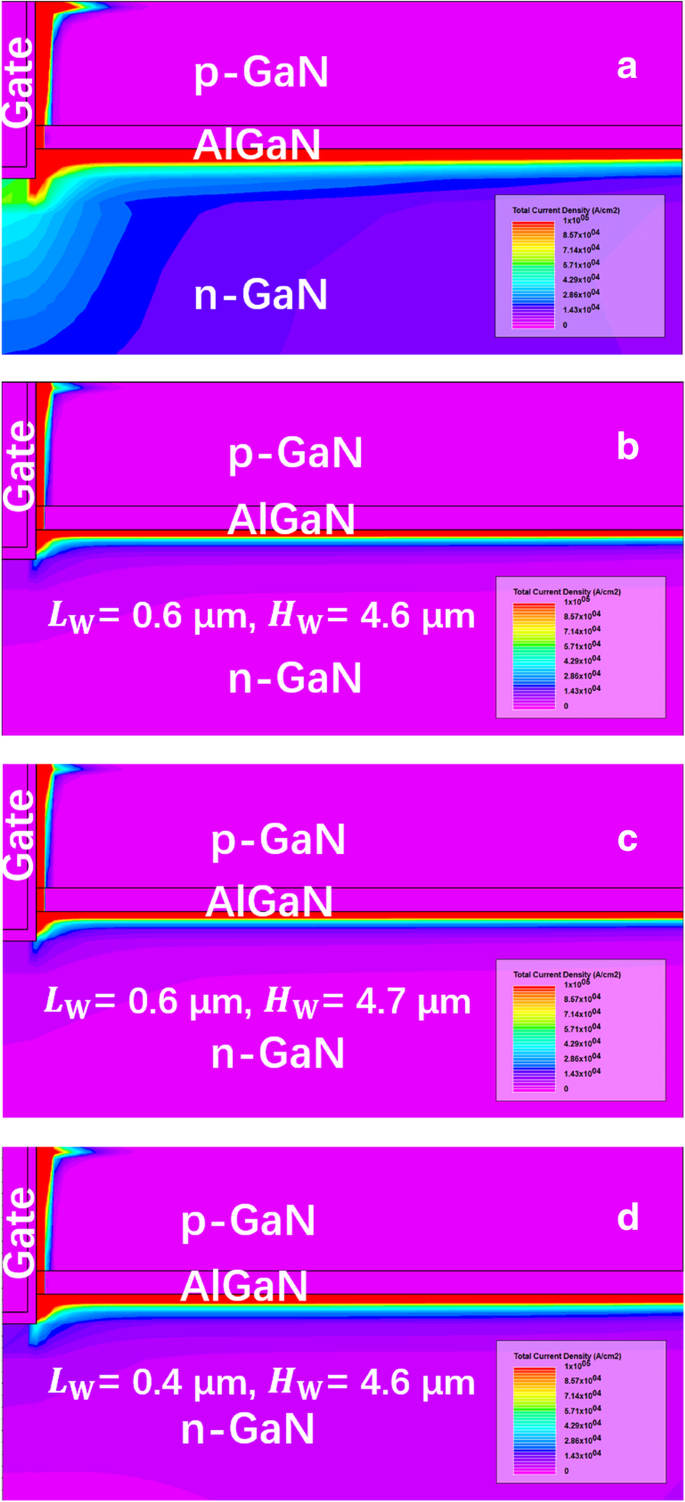

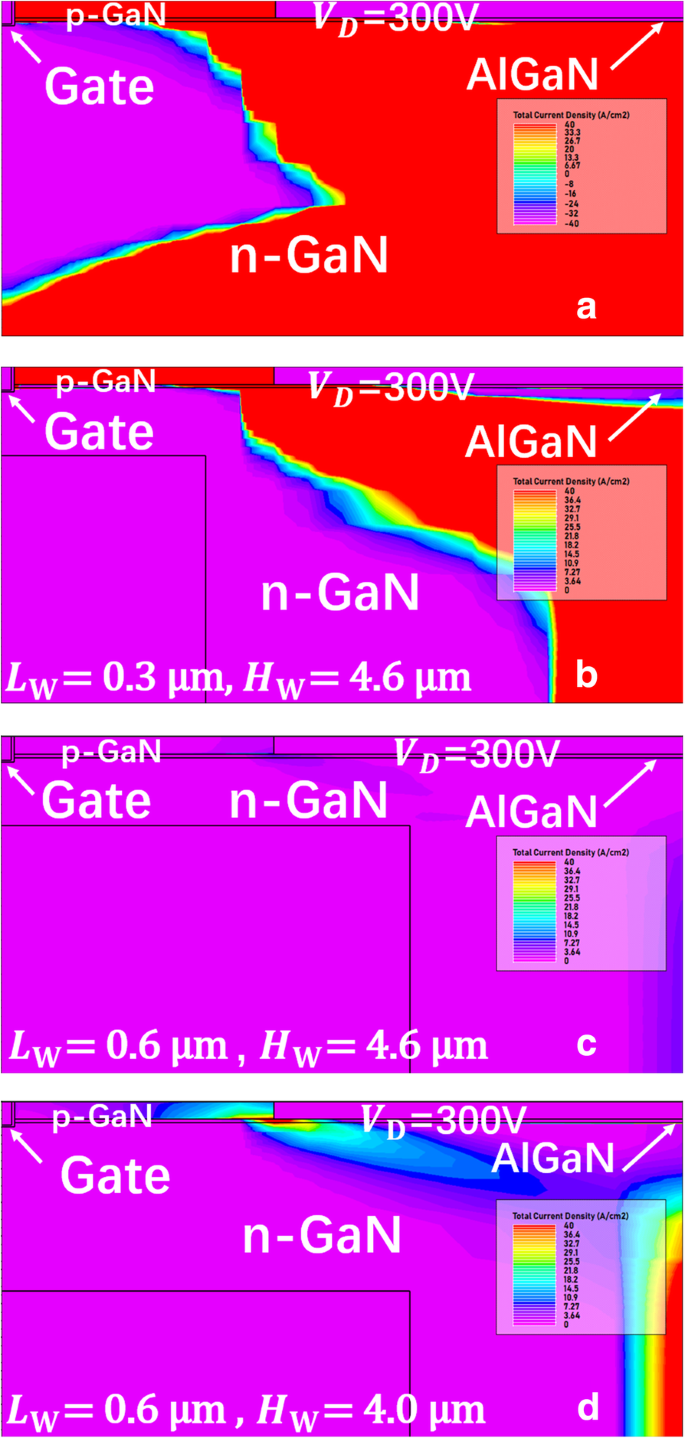

На рисунке 9 показаны детали распределения плотности тока вокруг затвора устройств VFET с SP или без него, при этом VFET без SP имеет более высокую пропускную способность по току, которая соответствует рисунку 8a. И наоборот, SP-VFET сокращает токопроводимость за счет сужения вертикального канала. Между тем, подробные рисунки ясно показывают, что ток в боковом канале переносится 2DEG, а общая плотность тока незначительно изменяется с увеличением высоты SP, что также демонстрируется в разделе механизма. Результаты показывают, что сопротивление бокового канала не особенно заметно со стороны SP в пределах умеренной высоты.

Плотность тока а устройство без ИП и б - г предлагаемый SP-VFET с различными геометрическими параметрами SP

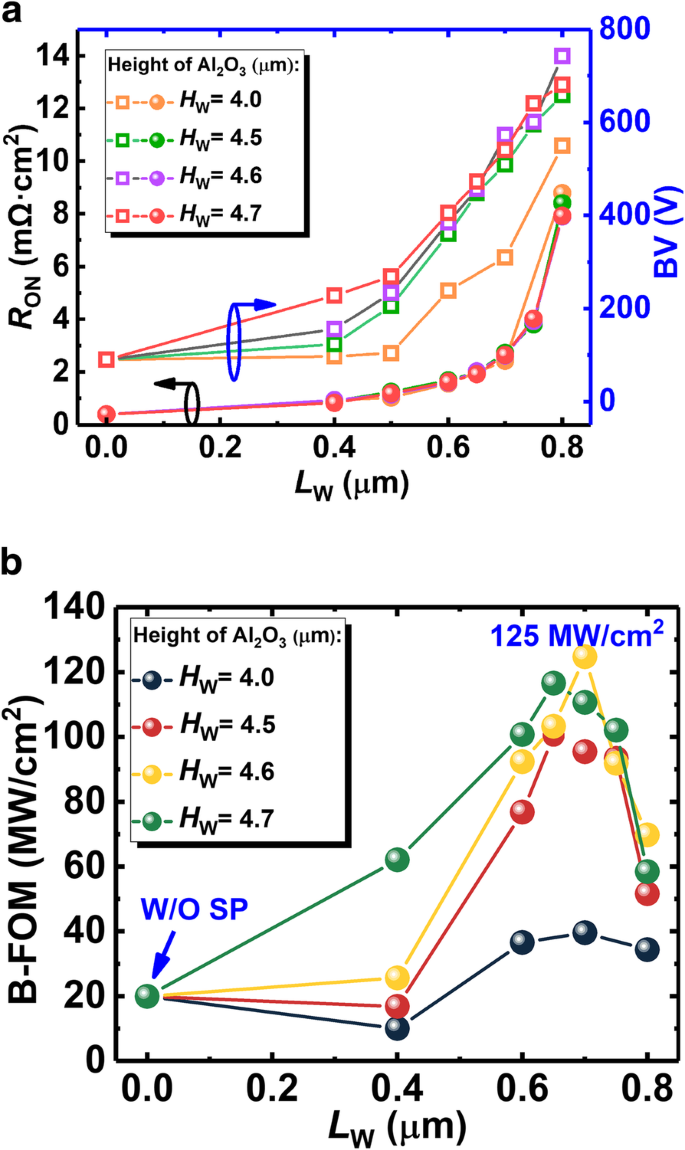

На рисунке 10a показано выделенное сопротивление в открытом состоянии и соответствующий BV. Сопротивление SP-VFET увеличивается с увеличением SP. И особенно, кривая зависимости сопротивления от длины SP демонстрирует гиперболический тренд, и градиент кривой увеличивается с увеличением длины SP. Как было проанализировано ранее, R на зависит от длины SP L Вт в виде гиперболической функции, которая соответствует результату моделирования. Более того, кривая сопротивления с разной высотой SP накладывается друг на друга, поскольку высота меньше 4,7 мкм, что позволяет предположить, что канал 2-DEG является основным боковым проводящим путем, и канал 2-DEG не затрагивается, как упомянуто выше.

а Извлеченное сопротивление в открытом состоянии, а также BV и b соответствующий BFOM предлагаемого SP-VFET с различной длиной и шириной SP

На рисунке 10b показана расчетная BFOM SP-VFET. Из-за разной скорости увеличения BV и сопротивления в открытом состоянии BFOM всех устройств сначала растет, а затем падает после того, как длина SP превышает 400 нм. Пиковая BFOM 125 МВт / см 2 достигается, когда длина достигает 700 нм, а высота достигает 4,6 мкм. По сравнению с устройством без SP, предлагаемый SP-VFET работает более чем в шесть раз лучше с точки зрения BFOM.

Это улучшение достигается благодаря подавлению сильного электрического поля под p-GaN, благодаря ловушке на границе раздела с отрицательным зарядом вокруг SP. Взаимодействие, которое происходит между захваченным отрицательным зарядом на границе раздела SP и обедненной областью вокруг p-GaN, формирует новое распределение E-поля в основном по направлению к захваченному заряду. Согласно закону Гаусса электрический поток ограничивается окруженным зарядом. Таким образом, введенное E-поле повлияет на электрический поток в другом месте. Поскольку отрицательный заряд обедненной области является основным источником напряженного E-поля вокруг p-GaN, E-поле, вносимое захваченным зарядом, будет играть роль в подавлении E-поля, скопившегося вокруг p-GaN, и, следовательно, BV увеличивается. В частности, когда длина SP меньше 400 нм, отрицательный заряд, вносимый SP, находится далеко от области истощения. Таким образом, E-поле, образованное между обедненной областью и захваченным отрицательным зарядом, слишком мало, чтобы играть роль в воздействии на сжатое E-поле под p-GaN. И в результате BV устройства немного вырастает. Однако, поскольку длина SP превышает 400 нм, из-за более захваченного отрицательного заряда на границе раздела SP и более короткого расстояния между областью обеднения и захваченным отрицательным зарядом, E-поле между областью обеднения и захваченным отрицательным зарядом составляет усилено, что привело к росту BV.

Кроме того, область вокруг SP чрезвычайно истощена из-за отрицательного заряда, вносимого SP. И, как показано на рис. 11, при более длинном SP вертикальный путь тока утечки сужается по ширине из-за того, что обедненная область сжимается к краю устройства, что также блокирует ток утечки и, следовательно, увеличивает BV. Следовательно, BV заметно возрастает с увеличением длины SP.

Плотность тока утечки a устройство без ИП и б - г предлагаемый SP-VFET с различными геометрическими параметрами SP

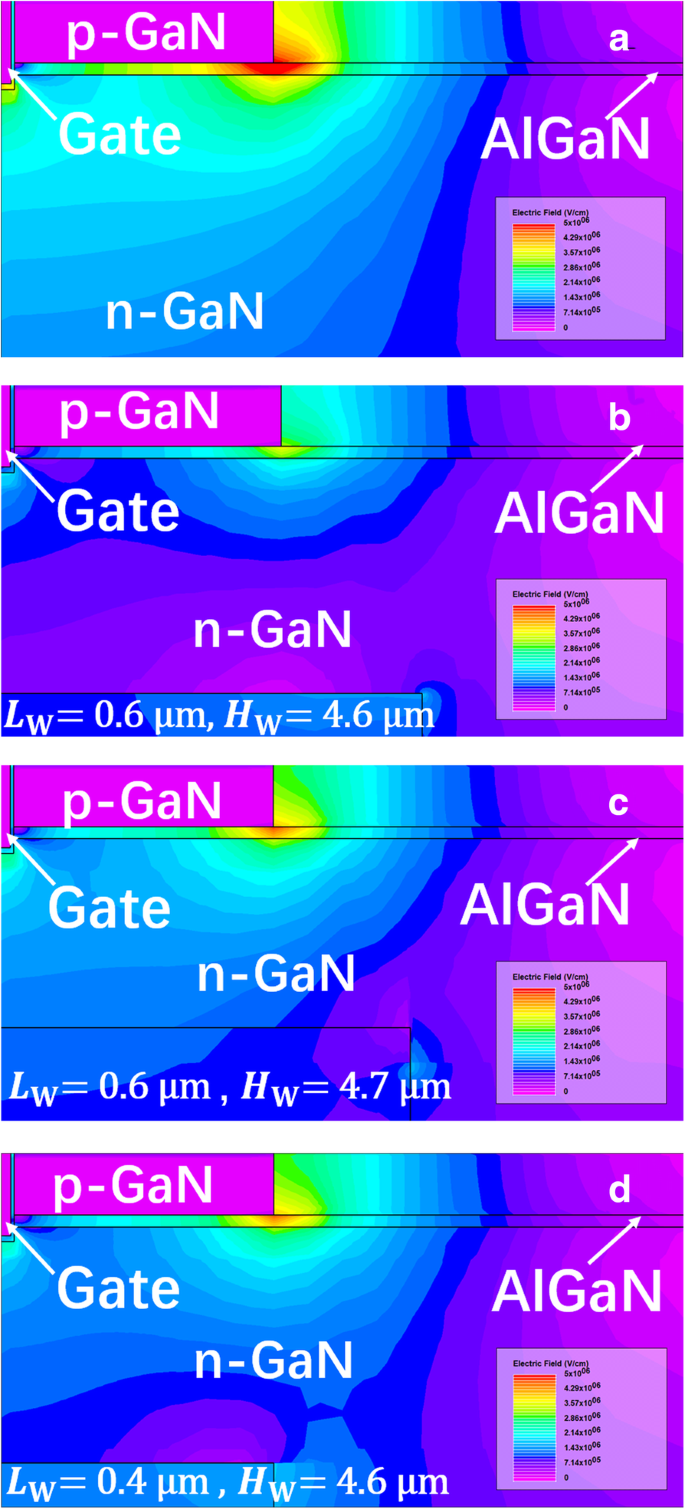

На рисунке 12 показано смоделированное распределение E-поля в SP-VFET при напряжении стока 300 В, где, очевидно, SP индуцирует другие новые точки концентрации E-поля, что означает, что область пика E-поля под p-GaN подавляется. . По сравнению с распределением E-поля в устройствах с разной высотой SP, увеличение длины SP подавляет скопление E-поля и, следовательно, увеличивает BV более эффективно.

Распределение электрического поля вокруг ворот VFET a с помощью или b - г без ИП при напряжении стока 300 В

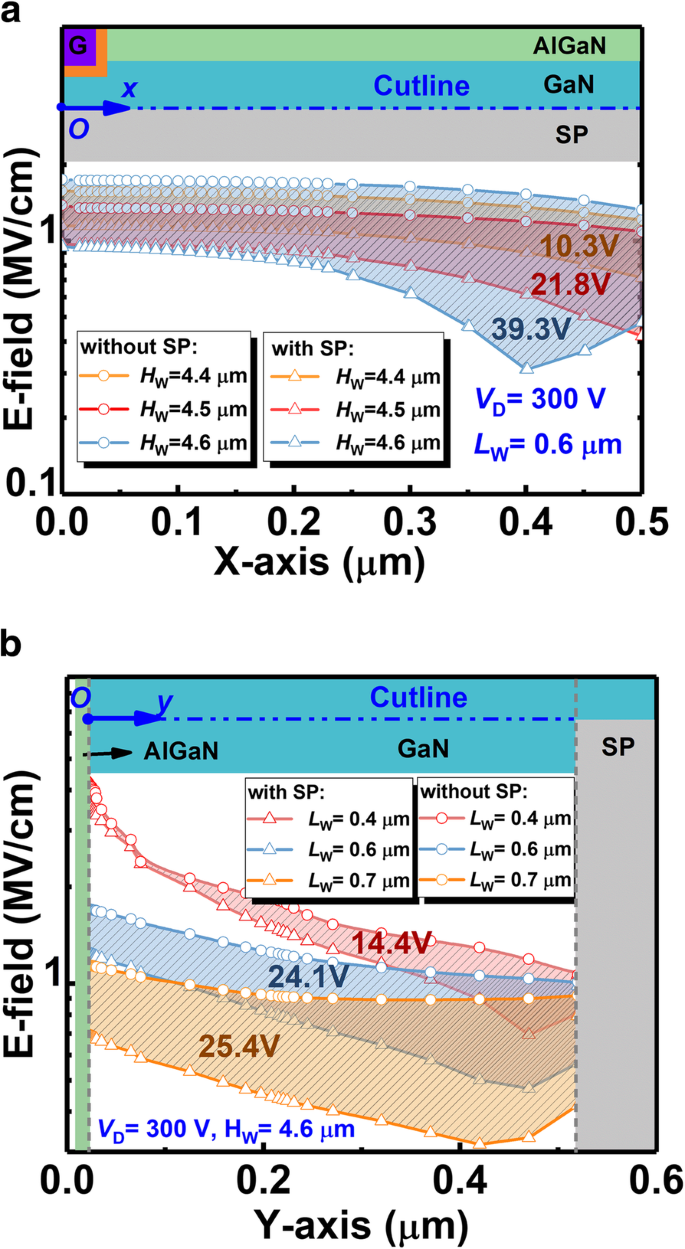

Такое сглаженное E-поле также можно было явно наблюдать на рис. 13, на котором нанесены распределения E-поля вдоль горизонтального и перпендикулярного края SP (см. Линию разреза). Как показано на полихромном рис.12, на рис.13 можно увидеть, что более высокий и длинный SP играет все более и более эффективную роль в восстановлении E-поля под p-GaN, и, привлекая E-поле для концентрации через SP край. Это перераспределение противодействует E-полю вокруг уязвимого p-GaN. Таким образом, BV устройства увеличивается, повышая B-FOM предлагаемого SP-VFET.

Распределение электронного поля a по горизонтали и b извлекается перпендикулярно по линии разреза кромки SP в SP-VFET

Заключение

В этой работе предлагается и исследуется новый улучшенный GaN вертикальный полевой транзистор (SP-VFET) с каналом 2DEG и рисунком подложки для улучшения его BFOM. Проверено экспериментально откалиброванным моделированием, реализованным с помощью ATLAS, именно SP снимает пик E-поля под p-GaN и одновременно привлекает новую концентрацию E-поля через SP, имеющую более высокое критическое E-поле. Следовательно, BV предлагаемого SP-VFET увеличивается с умеренно увеличивающимся сопротивлением в открытом состоянии из-за компенсации 2DEG. Следовательно, BFOM SP-VFET улучшается в шесть раз лучше, чем у устройства без SP, когда длина и высота SP составляют 700 нм и 4,6 мкм соответственно, что делает многообещающий потенциал предлагаемого SP-VFET в высокой плотности мощности. интеграция.

Сокращения

- n A :

-

Концентрация легирования GaN p-типа

- n D :

-

Концентрация легирования GaN n-типа

- 2DEG:

-

Двумерный электронный газ

- Al 0,23 GaN:

-

Нитрид алюминия-галлия с мольной долей 0,23 для алюминия

- Al 2 О 3 :

-

Оксид алюминия

- BFOM:

-

Достоинства Балиги

- D SP :

-

Плотность ловушек на границе раздела рисунка подложки

- Электронное поле:

-

Электрическое поле

- E Т :

-

Разница между зоной проводимости и уровнем энергии межфазной ловушки

- FET:

-

Полевой транзистор

- GaN:

-

Нитрид галлия

- HEMT:

-

Транзистор с высокой подвижностью электронов

- H G :

-

Высота ворот

- H W :

-

Высота рисунка подложки

- L Д :

-

Длина устройства

- L G :

-

Длина ворот

- L P :

-

Длина крышки p-GaN

- L Вт :

-

Длина рисунка подложки

- SiN:

-

Нитрид кремния

- SP:

-

Шаблон основания

- SP-VFET:

-

Вертикальный полевой транзистор с рисунком на подложке

- W Д :

-

Глубина устройства

- σ p :

-

Поляризационный заряд

Наноматериалы

- В пути с IoT

- Влияние состояний поверхности и мольной доли алюминия на поверхностный потенциал и 2DEG в HEMT из AlGaN / GaN

- Модуляция свойств электронной и оптической анизотропии ML-GaS вертикальным электрическим полем

- Влияние контактной неравновесной плазмы на структурные и магнитные свойства шпинелей Mn Х Fe3 - X О4

- Влияние отжига in situ на подвижность и морфологию органических полевых транзисторов на основе TIPS-пентацена

- Управляемый синтез BaYF5:Er3 +, Yb3 + с различной морфологией для усиления люминесценции с повышением частоты

- Влияние фотопроводимости, чувствительности к pH, шума и длины канала в датчиках Si Nanowire FET

- Зеленый синтез металлов и наночастиц оксидов металлов и их влияние на одноклеточную водоросль Chlamydomonas reinhardtii

- Влияние морфологии и кристаллической структуры на теплопроводность нанотрубок из диоксида титана

- Подготовка массива периодических полистирольных наносфер методом погружения-капли с травлением после осажд…