Поведение оборудования невозможно реализовать без условных операторов и других способов управления потоком логики. В Verilog есть набор блоков управления потоком и механизмов для достижения того же. если-иначе-если Этот условный оператор используется для принятия решения о том, следует ли выполнять

Блокировка Блокировка операторы присваивания назначаются с использованием = и выполняются друг за другом в процедурном блоке. Однако это не помешает выполнению операторов, работающих в параллельном блоке. module tb; reg [7:0] a, b, c, d, e; initial begin a = 8hDA; $display ([%0t

Размещение значений в сетях и переменных называется присвоением. Существует три основных формы: Процедурный Непрерывно Процедурный непрерывный Допустимые значения LHS Присваивание состоит из двух частей:правой (правой) и левой (левой) частей с символом равенства (=) или символом меньшего равенства

Существуют способы сгруппировать набор операторов вместе, которые синтаксически эквивалентны одному оператору и известны как блочные операторы. . Есть два типа блочных операторов:последовательные и параллельные. Последовательно Операторы обертываются с использованием begin и end ключевые слова и бу

В предыдущем примере исследовался простой детектор последовательности. Вот еще один пример детектора паттернов, который обнаруживает немного более длинный паттерн. Дизайн module det_110101 ( input clk, input rstn, input in, output out

Очень распространенным примером FSM является детектор последовательности, в котором аппаратная часть должна обнаруживать фиксированный шаблон в потоке двоичных битов, которые вводятся в него. Пример 00 Тестовый стенд 10 Журнал моделирования 27 В конструкции есть ошибка. Сможете найти?

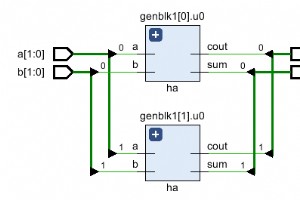

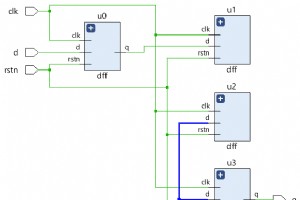

А generate Блок позволяет умножать экземпляры модулей или выполнять условное создание экземпляров любого модуля. Он предоставляет возможность построения дизайна на основе параметров Verilog. Эти операторы особенно удобны, когда одну и ту же операцию или экземпляр модуля необходимо повторить нескольк

Весь поведенческий код написан внутри 08 и 11 . Таким образом, какой бы цифровой дизайн вы ни собирались создать, он помещается в 23 блокировать. Он может иметь определенные порты, а может и не иметь их — разрешить вход сигналов в блок как 39 или экранируйте блок как 49 . Модуль Пустой модуль в при

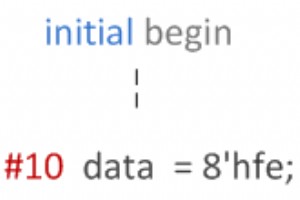

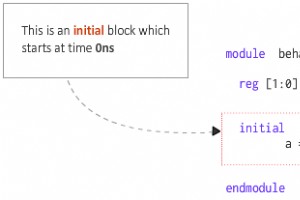

Набор операторов Verilog обычно выполняется последовательно при моделировании. Эти операторы помещаются внутри процедурного блокировать. В основном существует два типа процедурных блоки в Verilog - начальный и всегда Синтаксис initial [single statement] initial begin [multiple statemen

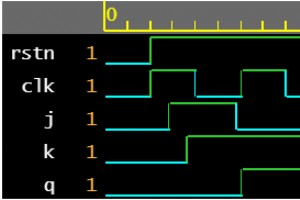

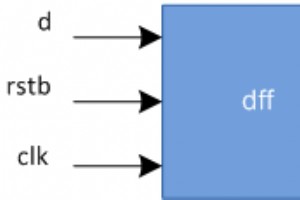

В предыдущей статье были показаны различные примеры использования always. блок для реализации комбинационной логики. always блок также в основном используется для реализации последовательного логика, которая имеет элементы памяти, такие как триггеры, которые могут хранить значения. JK Flip Flop Три

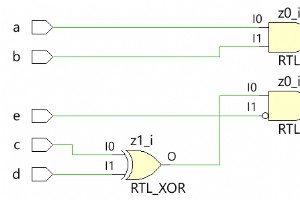

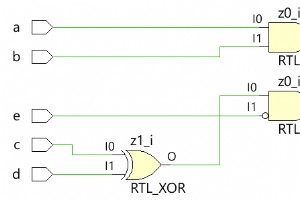

Блок verilog always можно использовать как для последовательной, так и для комбинационной логики. Несколько примеров дизайна были показаны с использованием assign утверждение в предыдущей статье. Далее будет рассмотрен тот же набор дизайнов с использованием always. блокировать. Пример №1. Простая ко

always блок является одним из процедурных блоки в Verilog. Операторы внутри блока always выполняются последовательно. Синтаксис always @ (event) [statement] always @ (event) begin [multiple statements] end always блок выполняется по какому-то конкретному событию. Событие определяется сп

Многобитовые проводники Verilog и переменные могут быть объединены вместе, чтобы сформировать более крупный мультисетевой проводник или переменную, используя конкатенацию. операторы { и } разделенных запятыми. Конкатенация также позволяет использовать выражения и размерные константы в качестве опера

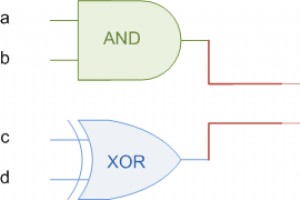

Данные, которые невозможно обработать, совершенно бесполезны, в цифровых схемах и компьютерных системах всегда будут требоваться какие-то расчеты. Давайте рассмотрим некоторые операторы в Verilog, которые позволят инструментам синтеза реализовать соответствующие аппаратные элементы. Арифметические о

Оператор Verilog assign обычно используется для непрерывного управления сигналом wire. тип данных и синтезируется как комбинационная логика. Вот еще несколько примеров дизайна с использованием assign заявление. Пример №1. Простая комбинационная логика Код, показанный ниже, реализует простую цифрову

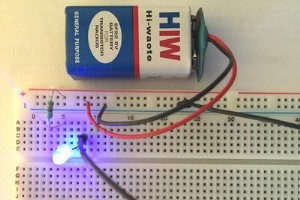

Сигналы типа wire или аналогичный проводной тип данных требует непрерывного присвоения значения. Например, рассмотрим электрический провод, используемый для соединения деталей на макетной плате. Пока батарея +5 В подключена к одному концу провода, компонент, подключенный к другому концу провода, пол

Как мы видели в предыдущей статье, более крупные и сложные проекты строятся путем иерархической интеграции нескольких модулей. Модули могут быть созданны внутри других модулей и портов этих экземпляров могут быть связаны с другими сигналами внутри родительского модуля. Эти соединения портов могут б

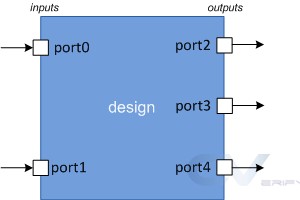

Порты — это набор сигналов, которые действуют как входы и выходы для определенного модуля и являются основным способом связи с ним. Думайте о модуле как о изготовленном чипе, размещенном на печатной плате, и становится совершенно очевидным, что единственный способ связи с чипом — через его контакты.

А module представляет собой блок кода Verilog, реализующий определенную функциональность. Модули могут быть встроены в другие модули, и модуль более высокого уровня может взаимодействовать со своими модулями более низкого уровня, используя их входные и выходные порты. Синтаксис модуль должен быть з

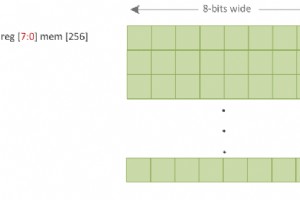

массив объявление сети или переменной может быть либо скалярным, либо векторным. Любое количество измерений может быть создано путем указания диапазона адресов после имени идентификатора и называется многомерным массивом. Массивы разрешены в Verilog для reg , wire , integer и real типы данных.

Verilog

Общие сведения о том, что ждет робототехнику в производстве

Trelleborg представляет высокотемпературный литой эпоксидный инструментальный материал

Программное обеспечение:создание собственных приложений на платформах с минимальным кодом и без кода

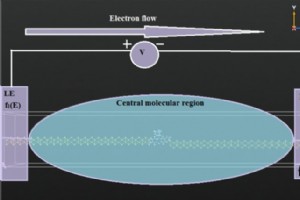

Электрически легированные наномасштабные устройства с использованием подхода из первых принципов:всесторо…