Весь поведенческий код написан внутри 08 и 11 . Таким образом, какой бы цифровой дизайн вы ни собирались создать, он помещается в 23 блокировать. Он может иметь определенные порты, а может и не иметь их — разрешить вход сигналов в блок как 39 или экранируйте блок как 49 . Модуль Пустой модуль в при

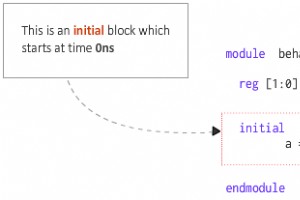

Набор операторов Verilog обычно выполняется последовательно при моделировании. Эти операторы помещаются внутри процедурного блокировать. В основном существует два типа процедурных блоки в Verilog - начальный и всегда Синтаксис initial [single statement] initial begin [multiple statemen

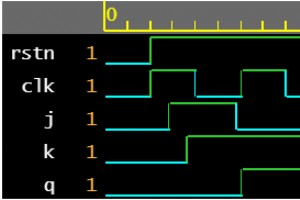

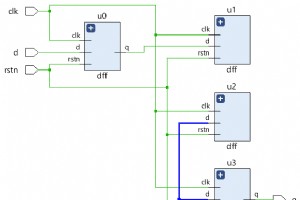

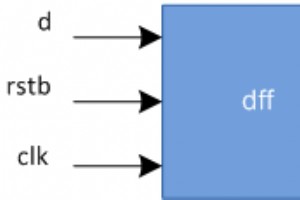

В предыдущей статье были показаны различные примеры использования always. блок для реализации комбинационной логики. always блок также в основном используется для реализации последовательного логика, которая имеет элементы памяти, такие как триггеры, которые могут хранить значения. JK Flip Flop Три

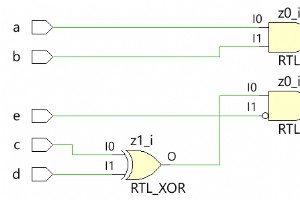

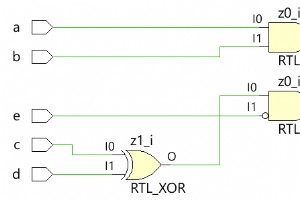

Блок verilog always можно использовать как для последовательной, так и для комбинационной логики. Несколько примеров дизайна были показаны с использованием assign утверждение в предыдущей статье. Далее будет рассмотрен тот же набор дизайнов с использованием always. блокировать. Пример №1. Простая ко

always блок является одним из процедурных блоки в Verilog. Операторы внутри блока always выполняются последовательно. Синтаксис always @ (event) [statement] always @ (event) begin [multiple statements] end always блок выполняется по какому-то конкретному событию. Событие определяется сп

Многобитовые проводники Verilog и переменные могут быть объединены вместе, чтобы сформировать более крупный мультисетевой проводник или переменную, используя конкатенацию. операторы { и } разделенных запятыми. Конкатенация также позволяет использовать выражения и размерные константы в качестве опера

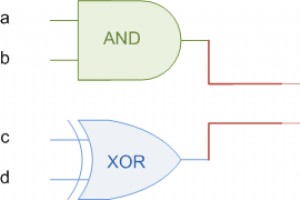

Данные, которые невозможно обработать, совершенно бесполезны, в цифровых схемах и компьютерных системах всегда будут требоваться какие-то расчеты. Давайте рассмотрим некоторые операторы в Verilog, которые позволят инструментам синтеза реализовать соответствующие аппаратные элементы. Арифметические о

Оператор Verilog assign обычно используется для непрерывного управления сигналом wire. тип данных и синтезируется как комбинационная логика. Вот еще несколько примеров дизайна с использованием assign заявление. Пример №1. Простая комбинационная логика Код, показанный ниже, реализует простую цифрову

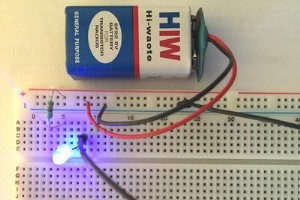

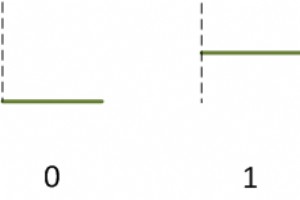

Сигналы типа wire или аналогичный проводной тип данных требует непрерывного присвоения значения. Например, рассмотрим электрический провод, используемый для соединения деталей на макетной плате. Пока батарея +5 В подключена к одному концу провода, компонент, подключенный к другому концу провода, пол

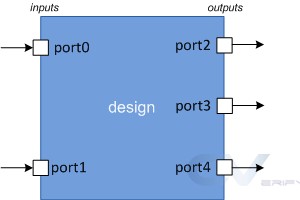

Как мы видели в предыдущей статье, более крупные и сложные проекты строятся путем иерархической интеграции нескольких модулей. Модули могут быть созданны внутри других модулей и портов этих экземпляров могут быть связаны с другими сигналами внутри родительского модуля. Эти соединения портов могут б

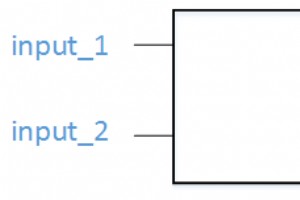

Порты — это набор сигналов, которые действуют как входы и выходы для определенного модуля и являются основным способом связи с ним. Думайте о модуле как о изготовленном чипе, размещенном на печатной плате, и становится совершенно очевидным, что единственный способ связи с чипом — через его контакты.

А module представляет собой блок кода Verilog, реализующий определенную функциональность. Модули могут быть встроены в другие модули, и модуль более высокого уровня может взаимодействовать со своими модулями более низкого уровня, используя их входные и выходные порты. Синтаксис модуль должен быть з

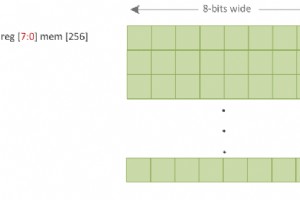

массив объявление сети или переменной может быть либо скалярным, либо векторным. Любое количество измерений может быть создано путем указания диапазона адресов после имени идентификатора и называется многомерным массивом. Массивы разрешены в Verilog для reg , wire , integer и real типы данных.

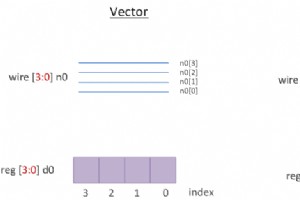

Verilog должен представлять как отдельные биты, так и группы битов. Например, однобитовый последовательный элемент представляет собой триггер. Однако 16-битный последовательный элемент представляет собой регистр, который может содержать 16 бит. Для этого в Verilog есть скаляр и вектор сети и перемен

Основное предназначение типов данных в языке Verilog состоит в том, чтобы представлять элементы хранения данных, такие как биты в триггере, и элементы передачи, такие как провода, соединяющие логические вентили и последовательные структуры. Какие значения содержат переменные? Почти все типы данных

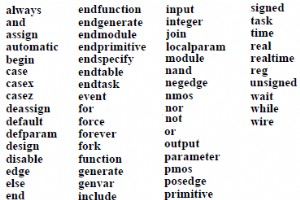

Лексические соглашения в Verilog аналогичны C в том смысле, что он содержит поток токенов. Лексическая лексема может состоять из одного или нескольких символов, а лексемы могут быть комментариями, ключевыми словами, числами, строками или пробелами. Все строки должны заканчиваться точкой с запятой ;

Прежде чем мы рассмотрим более подробно язык Verilog, было бы неплохо понять различные уровни абстракции при проектировании микросхем. Верхний уровень представляет собой архитектуру системного уровня, которая определяет различные подблоки и группирует их на основе функциональности. Например, класте

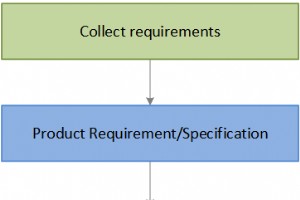

Типичный процесс проектирования следует структуре, показанной ниже, и может быть разбит на несколько этапов. Некоторые из этих фаз происходят параллельно, а некоторые последовательно. Мы посмотрим, как выглядит типичный цикл разработки проекта в современной отрасли. Требования Клиентом полупровод

На заре интегральных схем инженерам приходилось садиться и физически рисовать транзисторы и их соединения на бумаге, чтобы спроектировать их так, чтобы их можно было изготовить на кремнии. Большие и сложные схемы требовали большего количества инженеров, времени и других ресурсов, и вскоре возникла н

Verilog — это тип языка описания оборудования (HDL). Verilog — один из двух языков, используемых образованием и бизнесом для разработки FPGA и ASIC. Если вы не знакомы с тем, как работают FPGA и ASIC, вам следует прочитать эту страницу для ознакомления с FPGA и ASIC. Verilog и VHDL являются двумя на

Verilog

Blue Elephant:ведущий производитель фрезерных станков с ЧПУ в Китае

Фрезерный станок по дереву с ЧПУ Premium 2030 Linear ATC доставлен в Вальпараисо, Чили

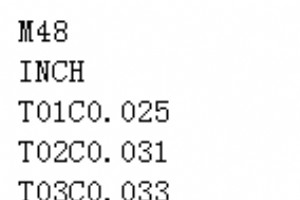

Как создать файлы NC Drill на основе другого программного обеспечения для проектирования печатных плат

Диэлектрические метаповерхности высокого порядка для высокоэффективных поляризационных светоделителей и о…