Введение в Верилог

Verilog — это тип языка описания оборудования (HDL). Verilog — один из двух языков, используемых образованием и бизнесом для разработки FPGA и ASIC. Если вы не знакомы с тем, как работают FPGA и ASIC, вам следует прочитать эту страницу для ознакомления с FPGA и ASIC. Verilog и VHDL являются двумя наиболее популярными используемыми HDL. По сравнению с традиционными языками программирования, такими как Java или C, Verilog работает совершенно по-другому. Давайте начнем с простого примера.

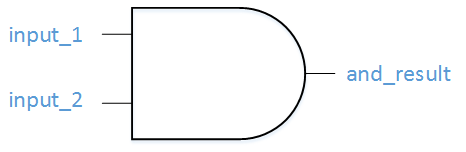

Сначала мы создадим файл Verilog, который описывает И Ворота. Напомним, что простой And Gate имеет два входа и один выход. Выход равен 1 только тогда, когда оба входа равны 1. Ниже приведено изображение ворот И, которые мы будем описывать с помощью Verilog.

И ворота

И ворота Давайте приступим! Одна фундаментальная единица Verilog называется проводом. А пока давайте предположим, что провод может быть только 0 или 1. Вот некоторая базовая логика проводов:

wire and_temp; assign and_temp = input_1 & input_2;

Мы создаем связь с именем and_temp в первой строке кода. Во второй строке кода мы берем созданный нами провод и назначаем провод. Чтобы присвоить его, мы используем логическую функцию AND, которая в Verilog представляет собой амперсанд (&). Если бы вам нужно было описать приведенный выше код, вы могли бы сказать:«Сигнал and_temp получает input_1 И с input_2."

Input_1 и Input_2 являются входными данными для этой части кода Verilog. Покажем полный список входов и выходов. Это делается в модуле определение. Модуль — это зарезервированное ключевое слово в Verilog, которое показывает создание блока кода с определенными входными и выходными данными.

module example_and_gate

(

input_1,

input_2,

and_result);

input input_1;

input input_2;

output and_result;

Это ваш основной модуль. Он определяет наш модуль с именем example_and_gate и 3 сигнала, 2 входа и 1 выход. Давайте соберем все вместе, чтобы закончить файл. Единственное, чего нам не хватает, так это назначения вывода and_result. . Еще одно примечание, // в Verilog используется для комментария.

///////////////////////////////////////////////////////////////////////////////

// File Downloaded from http://www.nandland.com

///////////////////////////////////////////////////////////////////////////////

module example_and_gate

(

input_1,

input_2,

and_result);

input input_1;

input input_2;

output and_result;

wire and_temp;

assign and_temp = input_1 & input_2;

assign and_result = and_temp;

endmodule // example_and_gate

Поздравляем! Вы создали свой первый файл Verilog.

Вам кажется, что вам пришлось написать много кода только для того, чтобы создать дурака и гейт? Во-первых, и ворота не дураки. Во-вторых, вы правы, HDL требуют много кода для выполнения относительно простых задач. Вас может утешить тот факт, что Verilog, по крайней мере, менее многословен, чем VHDL. Привыкайте к тому факту, что выполнение того, что было очень просто в программном обеспечении, займет у вас значительно больше времени в HDL, таком как Verilog или VHDL. Но просто попросите какого-нибудь программиста попытаться сгенерировать изображение на VGA-монитор, на котором отображается игра Конвея «Жизнь», и посмотрите, как у него закружится голова от изумления! Кстати, это видео создано с помощью FPGA. Вы сможете сделать это достаточно скоро!

Verilog