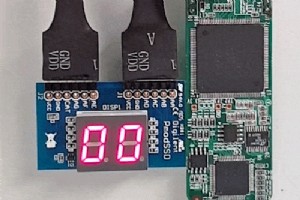

В этой статье я представлю модуль VHDL, способный отображать двузначное число на SSD Pmod:Seven-Segment Display от Digilent. Двойной 7-сегментный дисплей совместим с интерфейсом Pmod, что означает, что вы можете использовать его без пайки. Он подходит к разъему Pmod, который является стандартным для

* Эта статья содержит ссылку на рекламу UpCloud VPS Непрерывная доставка и непрерывная интеграция — это гибкие методологии разработки программного обеспечения, которые сокращают время цикла между изменением кода и его развертыванием. Используя автоматизацию для проверки изменений кода и создания ф

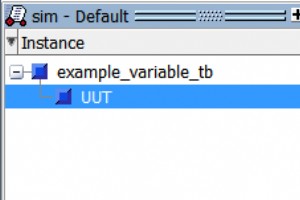

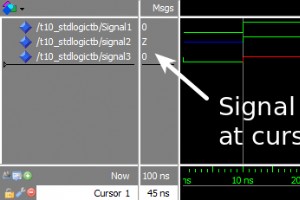

Как просмотреть переменные VHDL на сигнале моделирования В Modelsim есть способ просмотра переменных VHDL во время моделирования, но это не упрощает задачу. В Modelsim Объекты окно никогда не отображает переменные. Окно объектов Modelsim, без переменных Переменные можно включить, сначала отобра

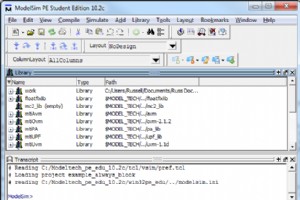

Учебное пособие. Использование Modelsim для моделирования для начинающих. Modelsim — это программа, созданная Mentor Graphics и используемая для моделирования проектов VHDL и Verilog. Это наиболее широко используемая программа моделирования в бизнесе и образовании. В этом руководстве сначала объясн

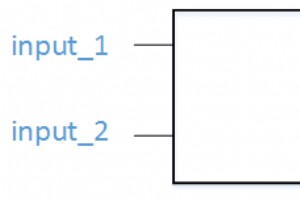

Учебное пособие. Введение в VHDL VHDL — ужасная аббревиатура. Это означает V. HSIC H аппаратное обеспечение D описание L язык. Аббревиатура внутри аббревиатуры, круто! VHSIC означает V. эри Ч ай S пописал Я интегрированный C цепь. Следовательно, расширенный VHDL равен V. очень быстродействующая инт

Короче говоря, VHDL — это компьютерный язык, используемый для проектирования цифровых схем. Я использую термин «компьютерный язык», чтобы отличить VHDL от других, более распространенных языков программирования, таких как Java или C++. Но является ли VHDL языком программирования? Да, это так. Это

Хотя инструменты VHDL и FPGA часто очень дороги, легко получить доступ к современному программному обеспечению бесплатно, если вы студент. Существует несколько симуляторов, редакторов и IDE для работы с VHDL. В этой статье показано, как установить две самые популярные программы, используемые инженер

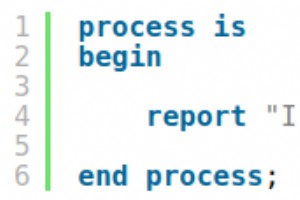

Изучая новый язык программирования, я всегда предпочитаю начинать с изучения печати. Когда вы освоите вывод «Hello World!», вы поймете, что среда работает. Он также показывает вам базовый скелет языка, минимальный код, необходимый для создания любого вывода. Вы можете подумать:но VHDL — это язык оп

В предыдущем уроке мы узнали, что процесс можно рассматривать как программный поток. Мы также узнали, что wait; оператор заставляет программу приостанавливаться на неопределенный срок. Но есть ли способ заставить программу ждать любое другое значение времени, кроме бесконечности? Если мы удалим wai

В предыдущем уроке мы научились задерживать время с помощью wait for. утверждение. Мы также узнали о цикле процесса. Теперь мы знаем, что если мы позволим этому, процесс «поток» навсегда зациклится внутри процесса. Но что, если мы хотим сделать что-то только один раз в начале процесса? А затем в ко

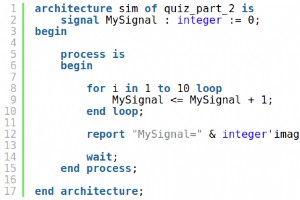

В предыдущем уроке мы научились создавать бесконечный цикл с помощью loop утверждение. Мы также узнали, как выйти из цикла с помощью exit утверждение. Но что, если мы хотим, чтобы цикл повторялся определенное количество раз? Цикл For-Loop — самый простой способ сделать это. Цикл For-Loop позволяет

В предыдущем уроке мы узнали, как использовать цикл For-Loop для перебора целочисленного диапазона. Но что, если нам нужно более детальное управление циклом, чем просто фиксированный диапазон целых чисел? Для этого мы можем использовать цикл while. Цикл While будет продолжать перебирать заключенный

Итак, вы завершили первую часть серии основных учебных пособий по VHDL. Поздравляем! Вы всего в нескольких часах и часах от того, чтобы стать настоящим гением VHDL. Но вы выполнили первый шаг, и сейчас это самая важная часть! Прежде чем мы пойдем дальше, вы должны проверить свои навыки с помощью эт

В предыдущем уроке мы узнали, как объявить переменную в процессе. Переменные хороши для создания алгоритмов внутри процесса, но они недоступны для внешнего мира. Если область действия переменной находится только в пределах одного процесса, как она может взаимодействовать с любой другой логикой? Реше

В предыдущем уроке мы узнали основные различия между сигналами и переменными. Мы узнали, что сигналы имеют более широкий охват, чем переменные, которые доступны только внутри одного процесса. Так как же мы можем использовать сигналы для связи между несколькими процессами? Мы уже научились использов

В предыдущем уроке мы использовали условное выражение с оператором «Ждать до». Выражение гарантировало, что процесс будет запускаться только тогда, когда два сигнала счетчика равны. Но что, если мы хотим, чтобы программа в процессе выполняла разные действия на основе разных входных данных? Оператор

Всегда следует использовать список деликатности. запускать процессы в производственных модулях. Списки чувствительности — это параметры процесса, в которых перечислены все сигналы, к которым этот процесс чувствителен. Если какой-либо из сигналов изменится, процесс проснется, и код внутри него будет

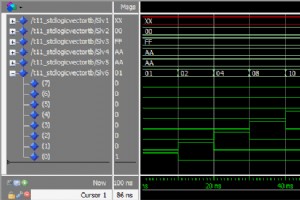

Наиболее распространенным типом, используемым в VHDL, является std_logic. . Думайте об этом типе как об одном бите, цифровой информации, передаваемой по одному физическому проводу. std_logic дает нам более детальный контроль над ресурсами в нашем дизайне, чем integer тип, который мы использовали в п

std_logic_vector тип может использоваться для создания сигнальных шин в VHDL. std_logic является наиболее часто используемым типом в VHDL, а std_logic_vector является его версией массива. В то время как std_logic отлично подходит для моделирования значения, которое может передаваться по одному пров

Проверьте свои навыки кодирования с помощью этой викторины VHDL после прохождения учебных пособий 6–11 из серии базовых учебных пособий по VHDL! Если вы читали сообщения в блогах, смотрели видео и выполняли упражнения, вы должны быть квалифицированы, чтобы ответить на большинство вопросов викторины

VHDL