Меня немного раздражали особенности интерфейса AXI, когда мне впервые пришлось создавать логику для интерфейса модуля AXI. Вместо обычных управляющих сигналов «занят/действителен», «полный/действителен» или «пустой/действителен» интерфейс AXI использует два управляющих сигнала с именами «готов» и «д

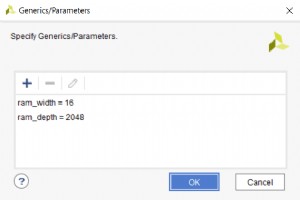

Удобный способ заполнить блочную ОЗУ начальными значениями — прочитать двоичные или шестнадцатеричные литералы из файла ASCII. Это также хороший способ создать ПЗУ (постоянную память) на VHDL. В конце концов, ОЗУ и ПЗУ в ПЛИС — это одно и то же, ПЗУ — это ОЗУ, из которого вы только читаете. В приме

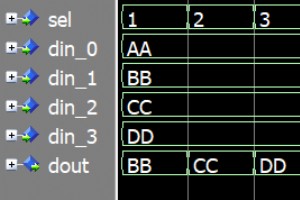

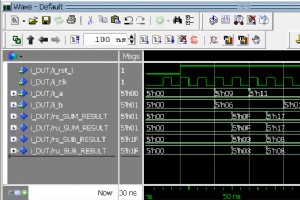

Чтение значений сигнала из файла — это альтернативный способ создания стимулов для тестируемого устройства (DUT). Последовательность тестового стенда и синхронизация жестко запрограммированы в файле стимула, который считывается тестовым стендом VHDL построчно. Это позволяет вам легко изменить шаблон

Преобразование файла изображения в формат растрового изображения обеспечивает самый простой способ чтения изображения с использованием VHDL. Поддержка формата файлов растровых графических изображений BMP встроена в операционную систему Microsoft Windows. Это делает BMP подходящим форматом изображени

Это видео представляет собой вводную презентацию о FPGA и технологии программируемой логики. Я выступил с этим 45-минутным докладом на мероприятии, организованном 7 Peaks Software в Бангкоке, Таиланд, 19 ноября 2019 года. Основные моменты презентации включают: 05:07 Кто использует ПЛИС? 09:06 Что

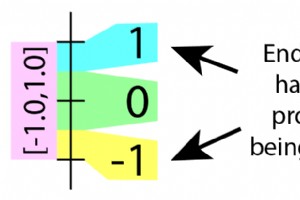

VHDL имеет встроенный генератор псевдослучайных чисел, но он может генерировать числа с плавающей запятой только в диапазоне от 0 до 1. К счастью, вы можете получить из него любой другой формат случайных данных, который вам нужен. Продолжайте читать эту статью, чтобы узнать, как создать real. или in

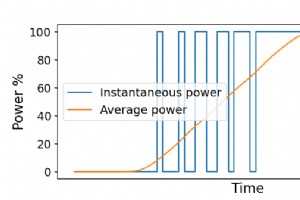

Широтно-импульсная модуляция (ШИМ) — это эффективный способ управления аналоговой электроникой с чисто цифровых выводов ПЛИС. Вместо того, чтобы пытаться регулировать аналоговое напряжение, ШИМ быстро включает и выключает ток питания аналогового устройства на полной мощности. Этот метод дает нам точ

Я заметил, что многие гаджеты, которые я купил за последние пару лет, перешли от мигания светодиодов к дыханию светодиодов. Большинство электронных приспособлений содержат светодиодный индикатор состояния, поведение которого указывает на то, что происходит внутри устройства. Моя электрическая зубна

Как остановить симулятор VHDL после завершения моделирования? Есть несколько способов сделать это. В этой статье мы рассмотрим наиболее распространенные способы успешного завершения тестового стенда. Представленный здесь код VHDL является универсальным и должен работать в любом поддерживающем симул

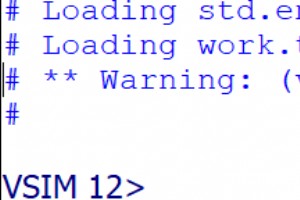

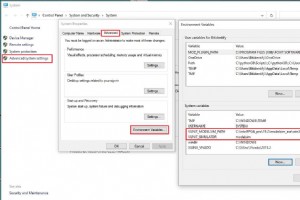

Большинство симуляторов VHDL используют язык команд инструментов (Tcl) в качестве языка сценариев. Когда вы вводите команду в консоли симулятора, вы используете Tcl. Кроме того, вы можете создавать сценарии с помощью Tcl, которые запускаются в симуляторе и взаимодействуют с вашим кодом VHDL. В этой

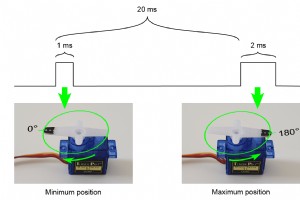

Сервоприводы моделей с радиоуправлением (RC) представляют собой крошечные приводы, обычно используемые в моделях самолетов, автомобилей и лодок для любителей. Они позволяют оператору дистанционно управлять транспортным средством по радиоканалу. Поскольку модели RC существуют уже давно, де-факто стан

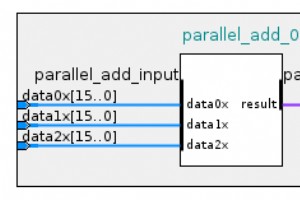

Оператор generate в VHDL может автоматически дублировать блок кода в замыкания с идентичными сигналами, процессами и экземплярами. Это цикл for для региона архитектуры, который может создавать связанные процессы или экземпляры модулей. В отличие от обычного цикла for, который может существовать т

Текстовые строки в VHDL обычно ограничиваются массивами символов фиксированной длины. Это имеет смысл, поскольку VHDL описывает аппаратное обеспечение, а строки общей длины требуют динамической памяти. Чтобы определить массив строк, вы должны выделить место во время компиляции для максимального кол

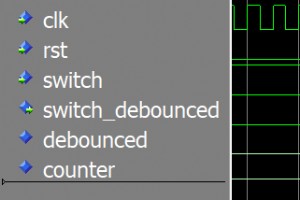

В этом руководстве рассматривается использование Integrated Logic Analyzer (ILA). и Виртуальный ввод/вывод (VIO) ядер для отладки и мониторинга проекта VHDL в Xilinx Vivado IDE. Во многих случаях разработчикам необходимо выполнять проверку на кристалле. То есть получить доступ к поведению внутренне

При разработке VHDL для критически важных с точки зрения безопасности приложений FPGA недостаточно написать испытательные стенды с максимальной отдачей. Вы должны предоставить доказательства того, что модуль работает должным образом и не имеет нежелательных побочных эффектов. Методы формальной пров

VUnit — одна из самых популярных на сегодняшний день сред проверки VHDL с открытым исходным кодом. Он сочетает в себе средство запуска тестов Python со специальной библиотекой VHDL для автоматизации ваших тестовых стендов. Чтобы дать вам это бесплатное руководство по VUnit, VHDLwhiz привлекает Ах

Вы когда-нибудь хотели запустить симуляцию VHDL, включающую IP-ядро Quartus, с помощью среды проверки VUnit? Это то, что имел в виду инженер FPGA Константинос Параскевопулос, но он не смог найти для этого подходящее руководство. К счастью, он использовал свой талант, чтобы понять, как это сделать,

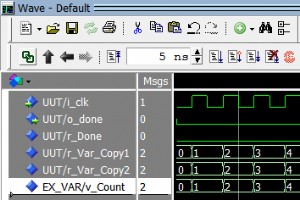

Переменные в VHDL действуют аналогично переменным в C. Их значение действительно в том месте кода, где переменная изменяется. Следовательно, если сигнал использует значение переменной before присвоение, оно будет иметь старое значение переменной. Если сигнал использует значение переменной after прис

Все цифровые дизайнеры должны понимать, как математика работает внутри FPGA или ASIC. Первым шагом к этому является понимание того, как работают типы сигналов со знаком и без знака. Подписанные и неподписанные типы существуют в numeric_std. пакет, который является частью библиотеки ieee. Следует отм

Конструкцию Record в VHDL можно использовать для упрощения кода. Записи похожи на структуры в C . Записи чаще всего используются для определения нового типа VHDL. Этот новый тип содержит любую группу сигналов, которую пожелает пользователь. Чаще всего это используется для упрощения интерфейсов. Это

VHDL