Что такое VHDL?

Короче говоря, VHDL — это компьютерный язык, используемый для проектирования цифровых схем.

Я использую термин «компьютерный язык», чтобы отличить VHDL от других, более распространенных языков программирования, таких как Java или C++. Но является ли VHDL языком программирования? Да, это так. Это язык программирования, который бесполезен для создания компьютерных программ!

VHDL — это язык параллельного программирования, управляемый событиями. Хотя он не подходит для создания программ, которые могут запускаться ЦП на компьютере, он отлично подходит для создания реального ЦП. Это язык описания оборудования, что означает, что его можно использовать для разработки цифровой логики.

Ознакомьтесь с серией учебных пособий по основам VHDL здесь!

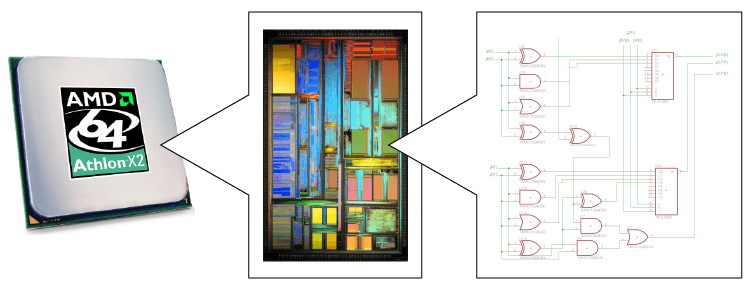

Рассмотрим приведенную выше иллюстрацию. Внутри микросхемы ЦП находится множество, в основном, цифровых электронных схем (посередине). Эти цифровые схемы можно показать с помощью принципиальной схемы (справа). При создании микросхемы интегральной схемы, такой как ЦП, мы должны начать с создания логической схемы справа.

Справедливо предположить, что такие принципиальные схемы создаются в каком-то редакторе схем, но это не так. Схемы описываются на текстовом языке, таком как VHDL.

Синтез

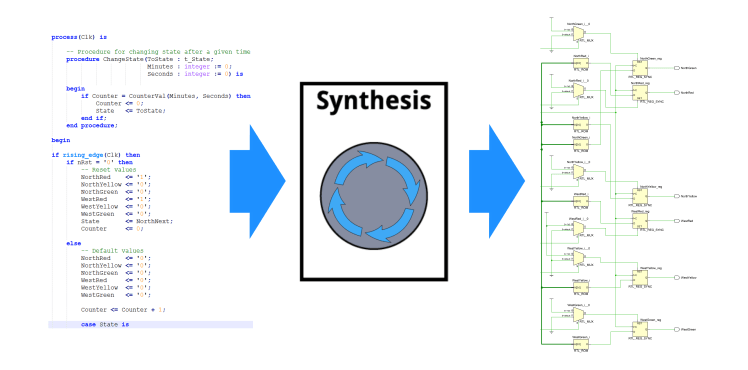

Вместо того, чтобы рисовать точные схемы в редакторе схем, мы используем VHDL для описания желаемого поведения схемы. Затем код VHDL можно преобразовать в точную схему в процессе, который называется синтез. . Инструмент синтеза — это программное приложение, которое берет код VHDL и пытается найти возможное решение для описанного вами поведения.

В случае успеха на выходе синтезатора будет список соединений, который, в свою очередь, можно просмотреть в редакторе схем.

Место и маршрут

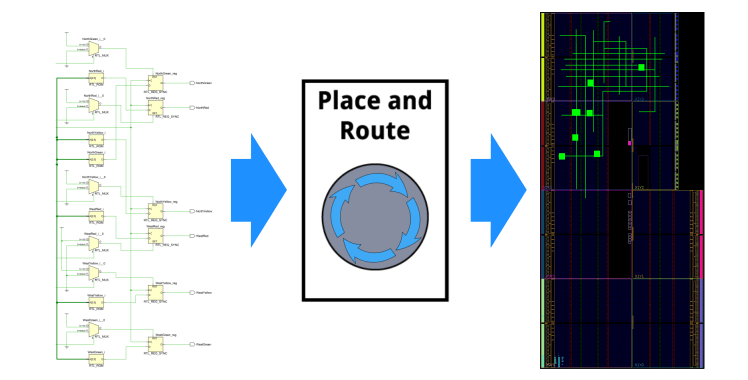

Хотя список соединений дает точное логическое описание схемы, он ничего не говорит о физической реализации. Чтобы получить точное описание физической схемы, список соединений проходит через процесс, который называется размещение и маршрут. или сокращенно ПАР. Маршрутизатор попытается выделить элементы из списка соединений физическим компонентам на целевом устройстве. Также необходимо проложить провода между всеми компонентами. Это гигантская головоломка, которую должен решить роутер!

В случае успеха выводом PAR будет другой вид списка соединений. Этот список соединений содержит информацию о размещении и маршрутизации и зависит от типа целевого устройства. Если целевым устройством является FPGA, маршрутизируемый список соединений можно преобразовать в программный файл. Если целевым устройством является ASIC, все будет немного сложнее.

Итак, что такое VHDL?

Это своего рода язык программирования, который используется для создания цифровой логики для интегральных схем.

Ознакомьтесь с основными учебными пособиями по VHDL здесь>>

VHDL