Учебное пособие — Введение в VHDL

VHDL — ужасная аббревиатура. Это означает V HSIC H аппаратное обеспечение D описание L язык. Аббревиатура внутри аббревиатуры, круто! VHSIC означает V очень H высокая S помочился я интегрированный C раздражение. Таким образом, расширение VHDL равно V. ery High Speed Integrated Circuit H аппаратное обеспечение D описание L язык. PHEW это полный рот. VHDL — это один из двух языков, используемых в сфере образования и бизнеса для разработки FPGA и ASIC. Если вы не знакомы с этими увлекательными схемами, сначала вам может быть полезно ознакомиться с FPGA и ASIC. VHDL и Verilog — это два языка, которые цифровые разработчики используют для описания своих схем, и они отличаются по своей конструкции от ваших традиционных языков программирования, таких как C и Java.

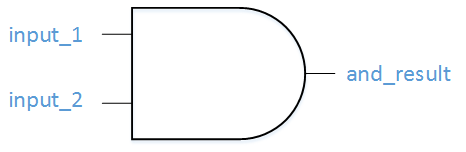

В приведенном ниже примере мы создадим файл VHDL, который описывает И Ворота. Напомним, что простой And Gate имеет два входа и один выход. Выход равен 1 только тогда, когда оба входа равны 1. Ниже приведено изображение вентиля И, который мы будем описывать с помощью VHDL.

И ворота

И ворота Давайте приступим! Основная единица VHDL называется сигналом. . А пока давайте предположим, что сигнал может быть либо 0, либо 1 (на самом деле есть и другие возможности, но мы доберемся до этого). Вот некоторая базовая логика VHDL:

signal and_gate : std_logic; and_gate <= input_1 and input_2;

Первая строка кода определяет сигнал типа std_logic и называется and_gate. Std_logic чаще всего используется для определения сигналов, но есть и другие, о которых вы узнаете позже. Этот код сгенерирует вентиль И с одним выходом (and_gate) и двумя входами (input_1 и input_2). Ключевое слово «и» зарезервировано в VHDL. Оператор <=известен как оператор присваивания. Когда вы словесно разбираете приведенный выше код, вы можете произнести вслух:«Сигнал and_gate ПОЛУЧАЕТ input_1 и обрабатывается input_2».

Теперь вы можете спросить себя, откуда берутся input_1 и input_2. Ну, как следует из их названия, они являются входными данными для этого файла, поэтому вам нужно сообщить о них инструментам. Входные и выходные данные файла определяются в сущности. . Сущность содержит порт, который определяет все входы и выходы в файл. Давайте создадим простую сущность:

entity example_and is

port (

input_1 : in std_logic;

input_2 : in std_logic;

and_result : out std_logic

);

end example_and;

Это ваша основная сущность. Он определяет объект с именем example_and и 3 сигнала, 2 входа и 1 выход, все они имеют тип std_logic. Для завершения этого необходимо еще одно ключевое слово VHDL, а именно архитектура. . Архитектура используется для описания функциональности конкретного объекта. Думайте об этом как о дипломной работе:сущность — это оглавление, а архитектура — это содержание. Давайте создадим архитектуру для этого объекта:

architecture rtl of example_and is signal and_gate : std_logic; begin and_gate <= input_1 and input_2; and_result <= and_gate; end rtl;

Приведенный выше код определяет архитектуру с именем rtl объекта example_and. Все сигналы, используемые архитектурой, должны быть определены между ключевыми словами «is» и «begin». Фактическая архитектурная логика находится между ключевыми словами «начало» и «конец». Вы почти закончили с этим файлом. И последнее, что вам нужно сказать инструментам, — какую библиотеку использовать. Библиотека определяет, как определенные ключевые слова ведут себя в вашем файле. А пока просто примите как должное, что вам нужны эти 2 строки в верхней части файла:

library ieee; use ieee.std_logic_1164.all;

Поздравляем! Вы создали свой первый файл VHDL. Готовый файл можно посмотреть здесь:

library ieee;

use ieee.std_logic_1164.all;

entity example_and is

port (

input_1 : in std_logic;

input_2 : in std_logic;

and_result : out std_logic

);

end example_and;

architecture rtl of example_and is

signal and_gate : std_logic;

begin

and_gate <= input_1 and input_2;

and_result <= and_gate;

end rtl;

Вам кажется, что вам пришлось написать много кода только для того, чтобы создать дурака и гейт? Во-первых, и ворота не дураки. Во-вторых, вы правы; VHDL — очень многословный язык. Привыкайте к тому факту, что выполнение того, что было очень просто в программном обеспечении, займет у вас значительно больше времени в HDL, таком как Verilog или VHDL. Но просто попросите какого-нибудь программиста попытаться сгенерировать изображение на VGA-монитор, на котором отображается игра Конвея «Жизнь», и посмотрите, как у него закружится голова от изумления! Кстати, это видео создано с помощью VHDL и FPGA. Вы сможете сделать это достаточно скоро!

VHDL