Переменные — пример VHDL

Переменные в VHDL действуют аналогично переменным в C. Их значение действительно в том месте кода, где переменная изменяется. Следовательно, если сигнал использует значение переменной before присвоение, оно будет иметь старое значение переменной. Если сигнал использует значение переменной after присваивание будет иметь новое значение переменной.

Правила переменных:

- Переменные можно использовать только внутри процессов.

- Любая переменная, созданная в одном процессе, не может использоваться в другом процессе.

- Переменные должны быть определены после ключевого слова process. но перед ключевым словом begin

- Переменные назначаются с помощью := символ присвоения

- Переменные, которым присвоено значение, немедленно принимают значение присвоенного значения.

Самое важное, что нужно понять, это то, что переменные сразу же принимают значение своего назначения. Вот пример, показывающий один полезный способ использования переменных:хранение данных для временного использования . Он использует оператор case и оператор конкатенации с амперсандом (&).

VAR_CASE : process (i_clk)

variable v_Choices : std_logic_vector(1 downto 0);

begin

v_Choices := i_select_1 & i_select_2; -- concatenation

case v_Choices is

when "00" =>

o_data <= "0001";

when "01" =>

o_data <= "0010";

-- ETC

В предыдущем примере мы объединили два сигнала, чтобы их можно было использовать в операторе case. Переменная v_Choices была сразу же доступна для использования, как только она была назначена. Давайте посмотрим на другой пример. Приведенный ниже пример является более полным и демонстрирует, как переменные немедленно принимают значение своего присвоения. Сигналы r_Var_Copy1 и r_Var_Copy2 кажутся одинаковыми, но r_Var_Copy2 никогда не достигает значения 5 до сброса.

library ieee;

use ieee.std_logic_1164.all;

use ieee.numeric_std.all;

entity variable_ex is

port (

i_clk : in std_logic;

o_done : out std_logic

);

end variable_ex;

architecture rtl of variable_ex is

signal r_Done : std_logic := '0';

signal r_Var_Copy1 : natural range 0 to 5 := 0;

signal r_Var_Copy2 : natural range 0 to 5 := 0;

begin

EX_VAR : process (i_clk)

variable v_Count : natural range 0 to 5 := 0;

begin

if rising_edge(i_clk) then

v_Count := v_Count + 1;

r_Var_Copy1 <= v_Count;

if v_Count = 5 then

r_Done <= '1';

v_Count := 0;

else

r_Done <= '0';

end if;

r_Var_Copy2 <= v_Count;

end if;

end process EX_VAR;

o_done <= r_Done;

end rtl;

Чтобы смоделировать наш дизайн, нам нужно создать тестовый стенд. Кроме того, переменные могут быть немного сложными для отображения в моделировании. Если вы используете Modelsim, узнайте больше о том, как увидеть ваши переменные в окне сигнала Modelsim.

Тестовый стенд:

library ieee;

use ieee.std_logic_1164.all;

entity variable_ex_tb is

end variable_ex_tb;

architecture behave of variable_ex_tb is

component variable_ex

port (

i_clk : in std_logic;

o_done : out std_logic

);

end component variable_ex;

constant c_CLK_PERIOD : time := 10 ns;

signal r_CLK : std_logic := '0';

signal w_DONE : std_logic;

begin

UUT : variable_ex

port map (

i_clk => r_CLK,

o_done => w_DONE

);

r_CLK <= not r_CLK after c_CLK_PERIOD/2;

end behave;

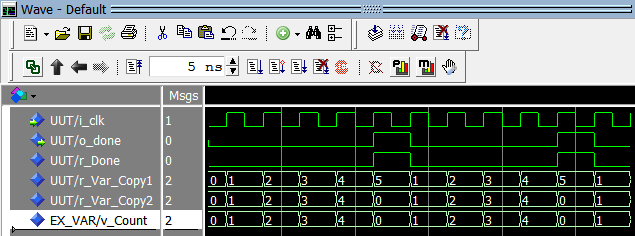

Переменные Пример формы сигнала тестового стенда

Переменные Пример формы сигнала тестового стенда В приведенном выше примере показано, как переменные действуют иначе, чем сигналы. Сигналы r_Var_Copy1 и r_Var_Copy2 кажутся одинаковыми, но r_Var_Copy2 никогда не достигает значения 5 до сброса.

VHDL

- Оператор процедуры — пример VHDL

- Записи — пример VHDL

- Параметры анализа

- Переменные C# и (примитивные) типы данных

- Переменные C++, литералы и константы

- C Переменные, константы и литералы

- Класс хранения C

- Строки в C:как объявить переменную, инициализировать, распечатать, пример

- Java — типы переменных

- С — переменные