Как связать библиотеки Quartus Prime IP с VUnit

Вы когда-нибудь хотели запустить симуляцию VHDL, включающую IP-ядро Quartus, с помощью среды проверки VUnit?

Это то, что имел в виду инженер FPGA Константинос Параскевопулос, но он не смог найти для этого подходящее руководство. К счастью, он использовал свой талант, чтобы понять, как это сделать, и был настолько любезен, что поделился этим с VHDLwhiz в этой гостевой статье. .

Давайте дадим слово Константиносу!

Часто бывает желательно включить предопределенные IP-адреса из каталога IP-адресов Quartus в ваш проект при моделировании вашей системы с помощью VUnit. Таким образом, цель следующего руководства — предоставить читателю знания о создании, включении и связывании внешних библиотек Quartus IP со средой VUnit.

Новый пользователь VUnit? Ознакомьтесь с этим руководством:Начало работы с VUnit

Обзор

Это руководство состоит из трех основных частей:

- Краткое описание выбранного IP.

- Действия, необходимые для создания и связывания соответствующих библиотек

- Проверка с использованием VUnit и Modelsim

Требования

- Квартус

- Скачать Quartus Prime

- QSYS должен быть указан в ПУТИ для ШАГА 2 (опция CMD)

- Intel Modelsim

- Пожалуйста, обратитесь к этой статье, чтобы узнать, как установить ModelSim бесплатно

- ModelSim должен быть в вашем PATH

- VUnit

- Пожалуйста, обратитесь к этой статье, чтобы узнать, как установить VUnit бесплатно

- Питон 3.6 или выше

- Загрузить Python

- Python должен быть на вашем пути

Также предполагается наличие базовых знаний VHDL и навыков работы с ModelSim.

Тестируемый дизайн

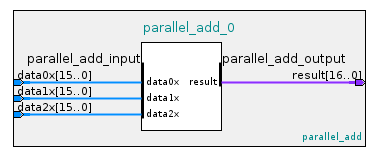

В нашем сценарии мы используем IP-адрес параллельного сумматора из списка IP-адресов Quartus Integer Arithmetic.

Наш проект принимает три 16-битных входных вектора и выводит добавленный результат в 17-битном векторе.

Шаг 1. Создание IP-адреса

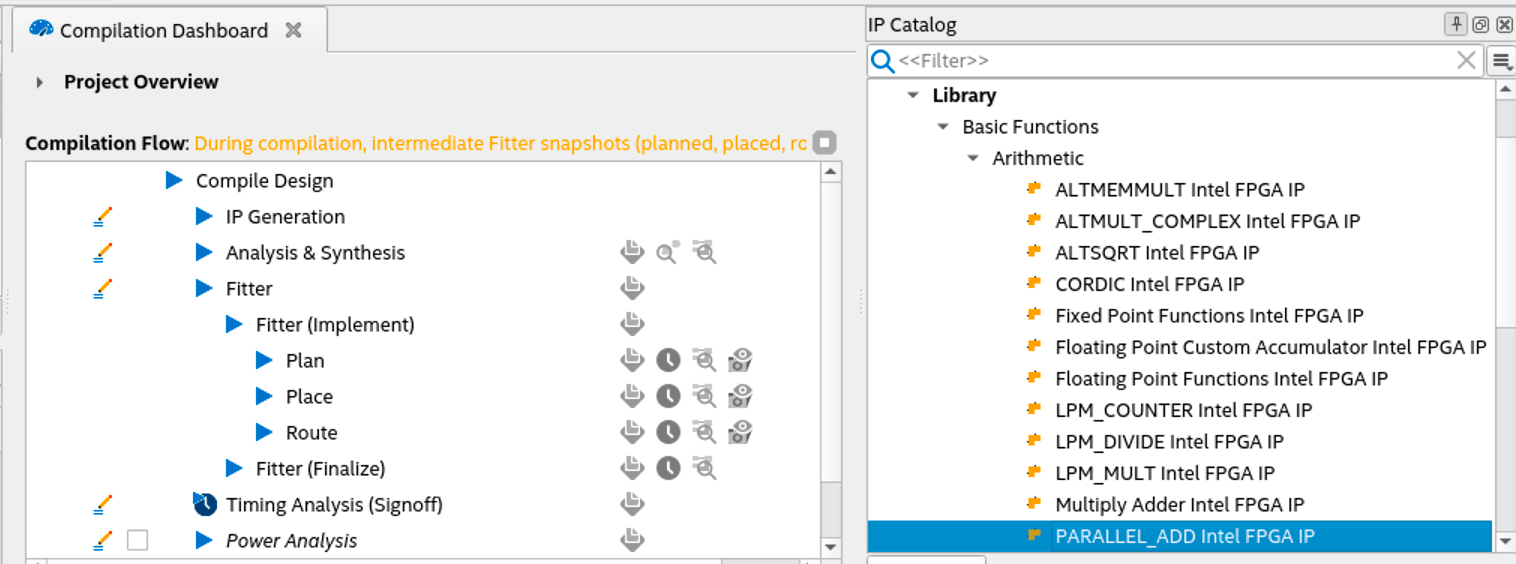

Мы создаем наш сумматор в окне каталога IP, дважды щелкнув компонент параллельного сумматора в разделе Библиотека/Основные функции/Арифметика.

После того, как мы укажем имя и настроим наш компонент в соответствии с нашими потребностями, мы нажимаем кнопку «Создать HDL» в правом нижнем углу.

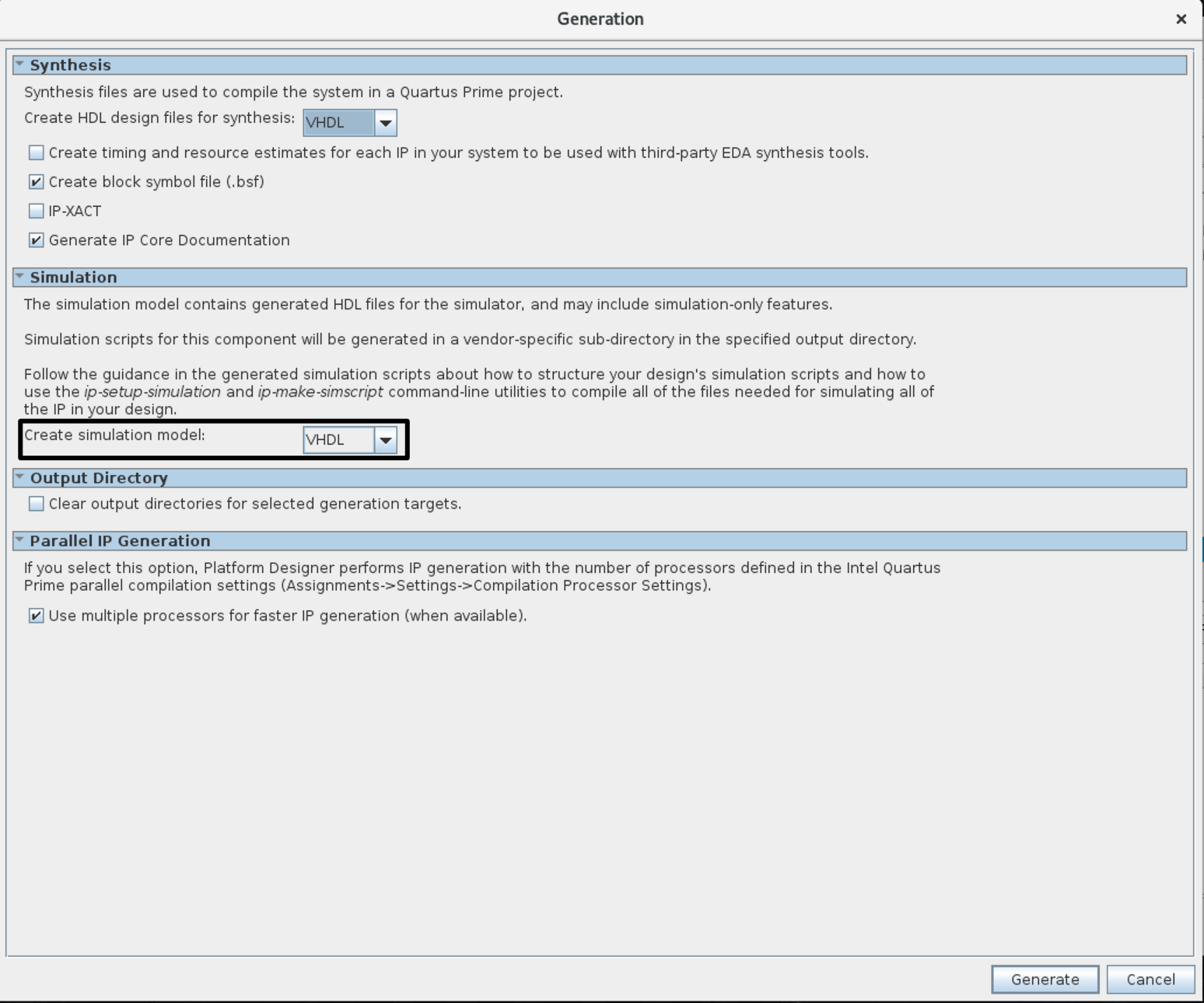

В этот момент появится окно, как показано на следующем рисунке.

Примечание. Мы должны установить Create simulation model под Simulation на VHDL или Verilog для создания файлов моделирования, поскольку параметр по умолчанию — none. Если мы не выберем ни одного, given_ip_name.spd файл не будет создан, что приведет к сбою следующего шага.

Приведенный выше процесс создает файл и папку под нашим quartus. каталог:

- Файл:

given_ip_name.ip - Папка:

given_ip_name

Папка содержит .vhd и .v файлы, которые необходимо добавить позже в наш run.py сценарий.

Шаг 2. Создание файлов моделирования IP

- Графический интерфейс: Выберите «Инструменты» ➤ «Создать сценарий настройки симулятора для IP» и укажите выходной каталог в окне подсказки,

- Командная команда: Используя команды Qsys, мы можем сгенерировать те же файлы, введя в терминале следующую команду:

ip-setup-simulation --quartus-project= <project's_QPF_filepath> --output-directory= <my_dir>

Используя один из двух описанных выше методов, мы указываем Quartus создать каталог для каждого поддерживаемого симулятора, который содержит сценарий для создания и компиляции библиотек IP.

Шаг 3. Создание и компиляция библиотек IP для Modelsim

Следующим шагом является поиск msim_setup.tcl сценарий в mentor папку, созданную на предыдущем шаге, и продублируйте ее с именем setup.tcl . Затем в setup.tcl файла, раскомментируйте показанные команды и установите $QSYS_SIMDIR переменная.

# # QSYS_SIMDIR is used in the Quartus-generated IP simulation script to # # construct paths to the files required to simulate the IP in your Quartus # # project. By default, the IP script assumes that you are launching the # # simulator from the IP script location. If launching from another # # location, set QSYS_SIMDIR to the output directory you specified when you # # generated the IP script, relative to the directory from which you launch # # the simulator. # # set QSYS_SIMDIR <script generation output directory> # # # # Source the generated IP simulation script. source $QSYS_SIMDIR/mentor/msim_setup.tcl # # # # Set any compilation options you require (this is unusual). # set USER_DEFINED_COMPILE_OPTIONS <compilation options> # set USER_DEFINED_VHDL_COMPILE_OPTIONS <compilation options for VHDL> # set USER_DEFINED_VERILOG_COMPILE_OPTIONS <compilation options for Verilog> # # # # Call command to compile the Quartus EDA simulation library. dev_com # # # # Call command to compile the Quartus-generated IP simulation files. com # #

После изменения и сохранения setup.tcl , мы можем безопасно выполнить файл Tcl, используя vsim команда.

vsim -c -do "do setup.tcl; quit"

Это генерирует скомпилированные библиотеки в mentor папка.

Шаг 4. Ссылка VUnit

Теперь, когда библиотеки IP созданы, мы должны связать их с помощью python run.py. сценарий.

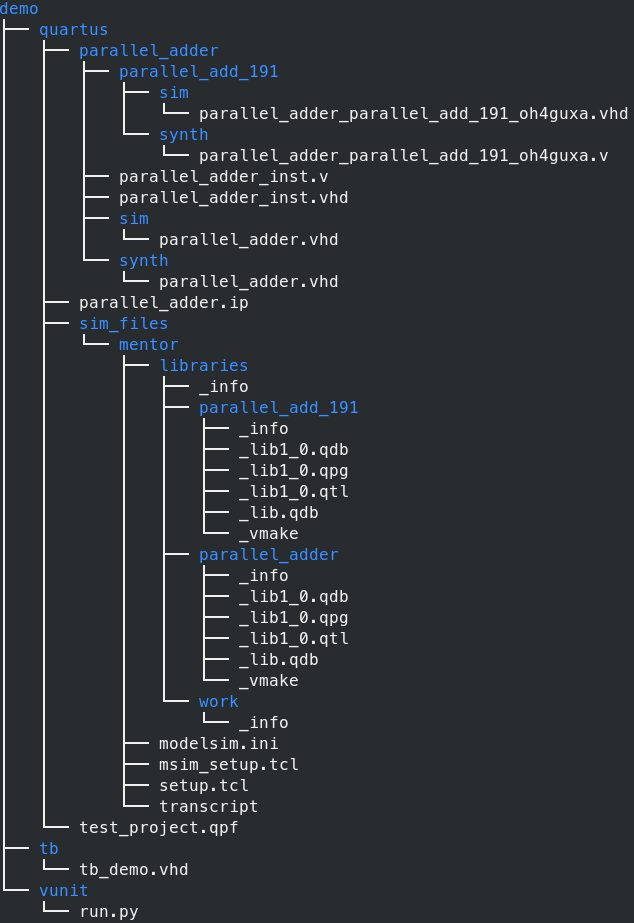

Посмотрите на рисунок ниже, чтобы лучше понять структуру каталогов нашего примера. Исходная топология состояла из корневой папки demo. , tb , vunit и quartus папки. Все подпапки и файлы в разделе quartus создаются с помощью платформы Quartus после создания проекта и выполнения шагов с 1 по 3.

Примечание. Quartus генерирует больше файлов и папок, но на изображении ниже показаны те, которые нас интересуют.

Используя это отдельное представление топологии в качестве эталона, мы можем указать наш КОРНЕВОЙ путь и пути к сгенерированным библиотекам, как показано ниже.

Обратите внимание, что sim_files — это каталог, который мы указали на шаге 2, где хранится папка наставника.

from vunit import VUnit from os.path import join, dirname, abspath # ROOT root = join(dirname(__file__), '../') # Path to generated libraries path_2_lib = '/quartus/sim_files/mentor/libraries/' # ROOT

После создания экземпляра VUnit с именем vu , мы можем указать библиотеку дизайна для нашего кода VHDL и связать любые необходимые внешние библиотеки:

# Create VUnit instance by parsing command line arguments

vu = VUnit.from_argv()

# create design's library

my_lib = vu.add_library('my_lib')

# Link external library

vu.add_external_library("parallel_adder", root + path_2_lib + "parallel_adder")

И, наконец, добавьте наши исходные файлы. Они расположены в трех подпапках в папке given_ip_name. каталог:

parallel_add_191synthsim

synth и sim dirs содержат ту же информацию, а именно дизайн верхнего уровня нашей ИС. Однако форматирование этих файлов в нашем случае в VHDL. Они могут быть в Verilog, и это зависит от выбранного языка на шаге 1.

Если наш проект верхнего уровня включает в себя подкомпоненты, мы также должны включить их исходные файлы. Они расположены в подпапках в given_ip_name каталог, например parallel_add_191 компонент в нашем случае.

my_lib.add_source_files(join(root,'quartus','parallel_adder','sim','parallel_adder.vhd'))

my_lib.add_source_files(join(root,'quartus','parallel_adder','parallel_add_191','sim','parallel_adder_parallel_add_191_oh4guxa.vhd'))

my_lib.add_source_files(join(root,'tb','tb_demo.vhd'))

testbench = my_lib.entity("tb_demo")

vu.main()

Тестовый стенд

Для начала вы можете перейти по этой ссылке, чтобы узнать об основах формирования тестового стенда VUnit.

Вернувшись к нашему тестовому стенду, мы добавляем необходимые библиотеки VUnit вместе с любой другой библиотекой, которую мы хотели бы использовать, и определяем наши сигналы.

Примечание. Выполнение процесса в нашем примере последовательное. Таким образом, управляющие сигналы (называемые флагами ) используются для уведомления процесса о том, должен ли он начаться или завершиться.

library IEEE; use IEEE.std_logic_1164.all; use ieee.numeric_std.all; library vunit_lib; context vunit_lib.vunit_context; entity tb_demo is generic ( runner_cfg : string:= runner_cfg_default); end tb_demo; architecture sim of tb_demo is constant clk_period : time := 10 ns; signal clk : std_logic := '0'; signal rst : std_logic := '0'; -- INPUTS signal data_a : std_logic_vector(0 to 15):= (others => '0'); signal data_b : std_logic_vector(0 to 15):= (others => '0'); signal data_c : std_logic_vector(0 to 15):= (others => '0'); -- OUTPUTS signal result : std_logic_vector(0 to 16); -- CONTROL FLAGS signal reset_done :boolean := false; signal sim_done :boolean := false; signal start_sim :boolean := false;

После этого мы создаем экземпляр нашего UUT. Quartus предоставляет примеры создания компонентов для VHDL и Verilog в соответствии с соглашениями об именах файлов ip_name_inst.vhd. и ip_name_inst.v .

begin -- Unit Under Test UUT : entity work.parallel_adder port map ( data0x => data_a, -- parallel_add_input.data0x data1x => data_b, -- .data1x data2x => data_c, -- .data2x result => result -- parallel_add_output.result );

Первые два запускаемых процесса:clk_process и reset_rel . Пока последний приостанавливается после сброса и вождения reset_done флаг true , clk_process работает на протяжении всего времени моделирования.

clk_process : process begin clk <= '1'; wait for clk_period/2; clk <= '0'; wait for clk_period/2; end process clk_process; reset_rel : process begin rst <= '1'; wait for clk_period*2; wait until rising_edge(clk); rst <= not rst; reset_done <= true; wait; end process reset_rel;

Теперь, когда сброс выполнен, мы можем вызвать test_runner процесс выполнения наших тестов. Кроме того, средство выполнения тестов остается активным до тех пор, пока sim_done флаг установлен на true , что происходит в последнем процессе.

test_runner : process

begin

test_runner_setup(runner, runner_cfg);

wait until reset_done and rising_edge(clk);

iterate : while test_suite loop

start_sim <= true;

if run("test_case_1") then

info ("Start");

info (running_test_case);

wait until sim_done;

end if;

end loop;

test_runner_cleanup(runner);

end process test_runner;

Наконец, data_generator процесс выполняет несколько сложений, присваивая значения трем входам нашего параллельного сумматора, используя for петля.

Примечание. Этот процесс запускается, когда test_runner процесс дает указание об этом, устанавливая start_sim флаг. В то время как в конце этого процесса он поднимает sim_done флаг, приказывающий исполнителю теста приостановить симуляцию.

data_generator : process

constant tag2 : log_level_t := new_log_level("INFO", fg => blue, bg => black, style => bright);

variable a,b,c,d : integer;

begin

wait until start_sim;

wait until rising_edge(clk);

show(display_handler, tag2);

if running_test_case = "test_case_1" then

for i in 0 to 10 loop

data_a <= std_logic_vector(to_unsigned(i+10,data_a'length));

data_b <= std_logic_vector(to_unsigned(i+20,data_a'length));

data_c <= std_logic_vector(to_unsigned(i+30,data_a'length));

wait until rising_edge(clk);

a := to_integer(unsigned(data_a));

b := to_integer(unsigned(data_b));

c := to_integer(unsigned(data_c));

d := to_integer(unsigned(result));

log( integer'image(a) &" + "& integer'image(b) &" + "& integer'image(c)

&" = "& integer'image(d), tag2);

end loop;

end if;

sim_done <= true;

end process data_generator;

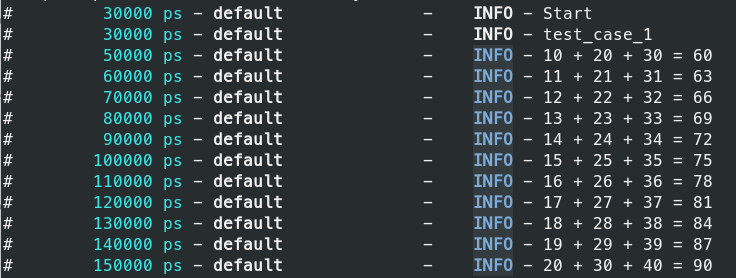

Подтверждение

Чтобы запустить тестовый пример и убедиться, что все работает должным образом, мы можем выполнить run.py script из каталога, в котором он находится, просто введя в терминале следующую команду.

python ./run.py -v

Примечание. Настраиваемый регистратор использовался для лучшей иллюстрации наших выходных данных, которые можно увидеть, предоставив подробный -v вариант. Кроме того, поскольку определен только один тестовый пример, нам не нужно указывать параметр для его указания.

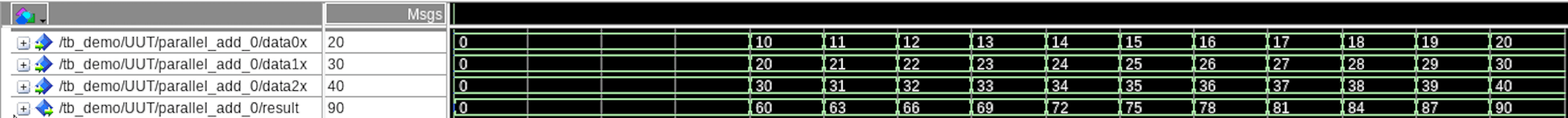

Наконец, для проверки наших результатов в ModelSim мы можем ввести следующую команду:

python ./run.py --gui

(Щелкните изображение, чтобы увеличить его)

Заключение

В заключение, в этом руководстве мы узнали, как включать и тестировать IP-адреса Quartus, которые находятся в каталоге IP-адресов, в VUnit. Мы использовали предопределенный IP. Однако мы также можем интегрировать упакованные настраиваемые IP-адреса таким образом в нашу среду VUnit.

Ознакомьтесь с этим руководством по VUnit, если вы еще этого не сделали:

Начало работы с VUnit

VHDL

- Что такое SigFox?

- Начало работы с VUnit

- Как создать список строк в VHDL

- Как остановить симуляцию в тестовом стенде VHDL

- Как создать ШИМ-контроллер на VHDL

- Как создать самопроверяющийся тестовый стенд

- Как технология обеспечивает решающее звено в этических цепочках поставок

- Машина для ограждения рабицы:принцип работы и бенефициар

- как заправить гидравлический шестеренчатый насос

- как заправить гидравлический насос трактора ford