Как остановить симуляцию в тестовом стенде VHDL

Как остановить симулятор VHDL после завершения моделирования? Есть несколько способов сделать это. В этой статье мы рассмотрим наиболее распространенные способы успешного завершения тестового стенда.

Представленный здесь код VHDL является универсальным и должен работать в любом поддерживающем симуляторе VHDL. Для методов, использующих Tcl, я перечислю команды для симуляторов ModelSim и Vivado.

Вы можете загрузить пример проекта с четырьмя различными тестовыми стендами из этой статьи, если у вас установлен ModelSim. Введите свой адрес электронной почты в форму ниже, чтобы получить Zip-файл!

Использование finish процедура

Готово VHDL процедура — мой любимый способ остановки тестового стенда VHDL, который завершается без ошибок. Вы должны импортировать «finish» из пакета STD.ENV, и вы должны скомпилировать тестовую среду в VHDL-2008 или новее, чтобы использовать его.

Приведенный ниже код завершает симуляцию, когда мы достигаем последней строки процесса секвенсора тестового стенда.

use std.env.finish; ... SEQUENCER_PROC : process begin -- Replace this line with your testbench logic wait until stop_condition; report "Calling 'finish'"; finish; end process;

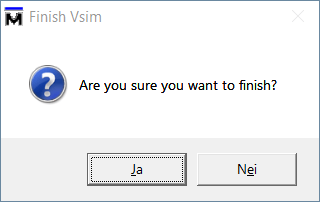

Обратите внимание, что завершить по умолчанию завершает симуляцию. Если вы используете ModelSim в версии с графическим интерфейсом, появится всплывающее окно с сообщением «Вы уверены, что хотите закончить?». Если вы нажмете Да, ModelSim закроется.

Это, вероятно, не то, что вы хотите. К счастью, мы можем предотвратить такое поведение, добавив параметр «-onfinish stop» в команду vsim, как показано ниже. Таким образом, заканчивается процедура будет вести себя так же, как stop процедура, которую мы обсудим в следующем разделе этой статьи.

vsim -onfinish stop work.using_finish_tb

Преимущество использования finish заключается в том, что вы можете использовать поведение по умолчанию при моделировании в пакетном режиме. Если вы используете сценарии для запуска моделирования, вы хотите вернуть управление вызывающему сценарию после завершения моделирования.

В приведенном ниже примере показан тестовый стенд с использованием finish процедура запущена в пакетном режиме ModelSim в Linux. После завершения тестового стенда симулятор завершает работу, и в последней строке мы возвращаемся в оболочку Linux.

jonas@ubuntu:~/stop_tb$ vsim -c -do 'vsim work.using_finish_tb; run -all' Reading pref.tcl # 10.5b # vsim work.using_finish_tb # vsim work.using_finish_tb # Start time: 22:58:31 on Jun 21,2020 # Loading std.standard # Loading std.env(body) # Loading work.using_finish_tb(sim) # run -all # ** Note: Calling 'finish' # Time: 1 ms Iteration: 0 Instance: /using_finish_tb # End time: 22:58:31 on Jun 21,2020, Elapsed time: 0:00:00 # Errors: 0, Warnings: 8 jonas@ubuntu:~/stop_tb$

Готово VHDL Процедура определена в стандартном пакете ENV. Как видно из приведенного ниже кода, он существует в двух перегруженных вариантах. Есть версия без каких-либо параметров, которую я всегда использую, и еще одна, которая принимает целое число состояния в качестве константы ввода.

procedure FINISH (STATUS: INTEGER); procedure FINISH;

Вы могли бы подумать, что целое число состояния становится кодом выхода при вызове из оболочки Linux, но это не так, по крайней мере, не с ModelSim. Проблема с использованием этого кода состояния заключается в том, что то, что он делает, зависит от симулятора. Формулировка в стандарте VHDL-2008 гласит:«значение параметра STATUS может использоваться хост-симулятором способом, определяемым реализацией “.

Однако вы можете управлять значением кода выхода Linux в ModelSim с помощью команды Tcl exit -code <value> , но это уже другая история.

Использование остановки процедура

VHDL стоп Процедура приостанавливает моделирование. Это может быть полезно, если вы хотите проверить значения сигнала вручную или даже продолжить моделирование позже. Симулятор рассматривает его как точку останова.

В приведенном ниже примере показано, как импортировать и использовать stop процедура.

use std.env.stop; ... SEQUENCER_PROC : process begin -- Replace this line with your testbench logic wait until stop_condition; report "Calling 'stop'"; stop; end process;

Проблема с использованием stop в установках на основе сценариев заключается в том, что он не выходит из симуляции. Вместо того, чтобы вернуть управление вызывающей стороне, ModelSim открывает командную оболочку Tcl, в результате чего вызывающий скрипт зависает на неопределенный срок.

В приведенном ниже листинге показан результат запуска тестового стенда, в котором используется stop. процедура в пакетном режиме. После остановки моделирования мы все еще находимся в ModelSim. Чтобы выйти из оболочки Tcl, нам нужно было бы набрать «exit».

jonas@ubuntu:~/stop_tb$ vsim -c -do 'vsim work.using_stop_tb; run -all' Reading pref.tcl # 10.5b # vsim work.using_stop_tb # vsim work.using_stop_tb # Start time: 22:58:56 on Jun 21,2020 # Loading std.standard # Loading std.env(body) # Loading work.using_stop_tb(sim) # run -all # ** Note: Calling 'stop' # Time: 1 ms Iteration: 0 Instance: /using_stop_tb # Break in Process SEQUENCER_PROC at ~/stop_tb/src/using_stop_tb.vhd line 23 # Stopped at ~/stop_tb/src/using_stop_tb.vhd line 23 VSIM 3>

Так же, как финиш процедура, остановить требуется VHDL-2008 или новее. Как показано ниже, существует перегруженная версия процедуры. Он принимает целочисленное значение состояния, но поведение зависит от симулятора.

procedure STOP (STATUS: INTEGER); procedure STOP;

Использование утверждения ключевое слово

Надежный и универсальный способ остановить испытательный стенд VHDL — создать ошибку утверждения. Это был первый способ, которым меня научили заканчивать симуляцию, когда я изучал VHDL в университете.

Дополнительный импорт не требуется, и он работает во всех версиях VHDL. Просто убедитесь, что используется уровень серьезности сбой. , как показано в примере ниже.

SEQUENCER_PROC : process begin -- Replace this line with your testbench logic wait until stop_condition; assert false report "Test: OK" severity failure; end process;

И почему я ненавижу этот способ остановить успешную симуляцию?

Во-первых, распечатка из приведенного выше примера выглядит странно и сбивает с толку:

# ** Failure: Test: OK

Пишет, что это «неудача», но в то же время тест «ОК». Это потому, что assert оператор должен указывать на состояние ошибки, а не на успешное завершение моделирования.

Другая досадная проблема, о которой я могу думать, заключается в том, что программно становится трудно определить, была ли симуляция успешной.

Большинство профессионалов VHDL в какой-то момент запускают моделирование из сценария, например, как часть более крупной схемы регрессионного тестирования. Если тестовый стенд также останавливается при ошибке утверждения, когда все в порядке, мы не можем использовать это в качестве маркера для определения работоспособности модуля VHDL.

Использование Tcl

Последний метод остановки симуляции, о котором я расскажу, — это использование Tcl в сочетании с VHDL. Вместо того, чтобы останавливать тестовый стенд из файла VHDL, мы устанавливаем обычный сигнал VHDL, когда пора остановиться. И заранее мы настраиваем симулятор на прослушивание этого триггерного сигнала.

Читайте также:

Почему вам нужно изучать Tcl

Посмотрите на приведенный ниже пример, в котором устанавливается сигнал с именем stop_condition. когда все тестовые примеры завершены.

signal stop_condition : boolean;

begin

-- Replace this line with your DUT instantiation

stop_condition <= not stop_condition after 1 ms;

SEQUENCER_PROC : process

begin

-- Put your testbench logic here

-- Pause this process forever after all tests are done

wait;

end process;

Любой процесс тестового стенда, выполнивший свою работу, можно перевести в спящий режим с помощью одного wait. оператор перед завершением процесса ярлык. Это предотвратит его перезапуск. Код Tcl для фактической остановки симуляции различается между симуляторами.

В ModelSim

Мы хотим остановить тестовый стенд, когда stop_condition Сигнал VHDL становится истинным . Мы можем сделать это, настроив обратный вызов в Tcl перед запуском тестового стенда VHDL.

Согласно справочному руководству по командам ModelSim, мы можем добиться этого, используя Tcl when команда. В приведенном ниже Tcl-коде мы регистрируем такой обратный вызов, а затем запускаем симулятор с помощью run -all. .

when {stop_condition} {

stop

echo "Test: OK"

}

run -all

Обратите внимание, что код в фигурных скобках не будет выполняться до тех пор, пока не произойдет обратный вызов. Когда код VHDL изменяет stop_condition сигнал на true , симулятор сделает паузу и выполнит две строки. В примере мы останавливаем симуляцию и выводим на консоль «Test:OK». У вас также может быть Tcl выход там есть команда, которая закроет симулятор, точно так же, как finish VHDL процедура.

# vsim # Start time: 22:31:11 on Jun 22,2020 # Loading std.standard # Loading work.using_tcl_tb(sim) # Test: OK # Simulation stop requested.

В приведенном выше листинге показан вывод, выводимый на консоль ModelSim после завершения тестового стенда Tcl/VHDL. Если вы хотите попробовать его на своем компьютере, используйте форму ниже, чтобы загрузить проект ModelSim со всеми примерами из этой статьи!

В Вивадо

Согласно Справочному руководству по командам Tcl Vivado Design Suite, мы можем зарегистрировать обратный вызов Tcl, используя add_condition команда. В приведенном ниже коде показан эквивалент Xilinx для ранее обсуждавшейся версии ModelSim.

set sim_fileset sim_1

launch_simulation -simset [get_filesets $sim_fileset]

add_condition -notrace stop_condition {

stop

puts "Test: OK"

}

run all

-notrace switch предотвращает вывод строк кода в функции обратного вызова на терминал во время их выполнения. Я предпочитаю, чтобы в консоли не было лишнего беспорядка.

В приведенном ниже листинге показан фрагмент симуляции, запущенной в консоли симулятора Vivado.

launch_simulation: ...

add_condition -notrace stop_condition {

stop

puts "Test: OK"

}

condition8

run all

Test: OK

Заключительные мысли

Как вы видели, есть много способов завершить симуляцию VHDL. Однако единственный, который я когда-либо использовал, — это finish VHDL-2008. процедура.

Все симуляторы сейчас поддерживают VHDL-2008, и вам не нужно компилировать код RTL в 2008 году, только тестовый стенд. окончание процедура является наиболее переносимым методом и позволяет остановить симулятор при работе в режиме графического интерфейса или выйти из него при работе в пакетном режиме. Именно такое поведение мне нужно большую часть времени.

Но у методов Tcl есть преимущества, которые выходят за рамки этой статьи. Когда вы приостановили симулятор в обратном вызове Tcl, вы можете сделать гораздо больше, чем просто остановить симулятор и выйти. Вы можете исследовать сигналы VHDL и даже манипулировать ими с помощью Tcl, находясь в обратном вызове. Это проверка с использованием Tcl.

VHDL

- Как создать список строк в VHDL

- Как создать управляемый Tcl тестовый стенд для модуля кодовой блокировки VHDL

- Как создать ШИМ-контроллер на VHDL

- Как генерировать случайные числа в VHDL

- Интерактивный тестовый стенд с использованием Tcl

- Как создать самопроверяющийся тестовый стенд

- Как создать связанный список в VHDL

- Как использовать процедуру в процессе в VHDL

- Как использовать функцию в VHDL

- Как остановить Rust