Как использовать наиболее распространенный тип VHDL:std_logic

Наиболее распространенным типом, используемым в VHDL, является std_logic. . Думайте об этом типе как об одном бите, цифровой информации, передаваемой по одному физическому проводу. std_logic дает нам более детальный контроль над ресурсами в нашем дизайне, чем integer тип, который мы использовали в предыдущих уроках.

Обычно мы хотим, чтобы провод в цифровом интерфейсе имел значение '1' или '0' . Эти два значения являются единственными значениями, которые может иметь бит, двоичная цифра. Но на самом деле физический цифровой сигнал может находиться в нескольких состояниях, которые std_logic type хорошо подражает. Поэтому это наиболее часто используемый тип в VHDL.

Эта запись в блоге является частью серии учебных пособий по основам VHDL.

std_logic type может принимать следующие значения:

| '1' | Логика 1 |

| '0' | Логический 0 |

| Z | Высокое сопротивление |

| W | Слабый сигнал, не могу определить 0 или 1 |

| L | Слабый 0, раскрытие |

| "Н" | Слабое 1, подтягивание |

| '-' | Не важно |

| "У" | Неинициализированный |

| "X" | Неизвестно, несколько водителей |

Может показаться, что это множество различных состояний для типа, который должен моделировать одно двоичное значение. Не волнуйтесь, мы не будем использовать все эти типы в этой серии руководств. Мы будем использовать '1' и '0' конечно. И мы также увидим 'U' и 'X' , что поможет нам обнаружить ошибки в нашем дизайне. Другие значения — это расширенные функции VHDL, которые можно использовать для таких вещей, как моделирование связи, например, с I

2

. C-устройства или для создания шин с тремя состояниями.

Если несколько процессов пытаются записать в сигнал разные значения, мы говорим, что у него несколько драйверов. . Если std_logic signal имеет несколько драйверов, это не будет ошибкой компиляции или времени выполнения, по крайней мере, не в симуляторе. Это потому, что std_logic является разрешенным типом , что означает, что его значение будет определяться функцией разрешения.

Значение std_logic сигнал с двумя драйверами будет определяться на основе этой таблицы разрешений:

| U | X | 0 | 1 | Z | W | L | H | – | <тд>|

|---|---|---|---|---|---|---|---|---|---|

| U | X | X | 1 | 1 | 1 | 1 | 1 | X | 1 |

| U | X | 0 | X | 0 | 0 | 0 | 0 | X | 0 |

| U | U | U | U | U | U | U | U | U | U |

| U | X | X | X | X | X | X | X | X | X |

| U | X | 0 | 1 | Z | W | L | H | X | Z |

| U | X | 0 | 1 | W | W | W | W | X | W |

| U | X | 0 | 1 | L | W | L | W | X | L |

| U | X | 0 | 1 | H | W | W | H | X | H |

| U | X | X | X | X | X | X | X | X | – |

Упражнение

В этом видеоуроке мы узнаем, как использовать объявления и показы std_logic. сигналы в форме волны:

Окончательный код, который мы создали в этом руководстве:

library ieee;

use ieee.std_logic_1164.all;

entity T10_StdLogicTb is

end entity;

architecture sim of T10_StdLogicTb is

signal Signal1 : std_logic := '0';

signal Signal2 : std_logic;

signal Signal3 : std_logic;

begin

process is

begin

wait for 10 ns;

Signal1 <= not Signal1;

end process;

-- Driver A

process is

begin

Signal2 <= 'Z';

Signal3 <= '0';

wait;

end process;

-- Driver B

process(Signal1) is

begin

if Signal1 = '0' then

Signal2 <= 'Z';

Signal3 <= 'Z';

else

Signal2 <= '1';

Signal3 <= '1';

end if;

end process;

end architecture;

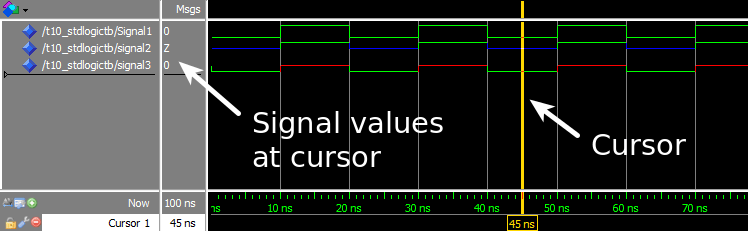

Окно сигнала в ModelSim после того, как мы нажали кнопку «Выполнить» и увеличили временную шкалу:

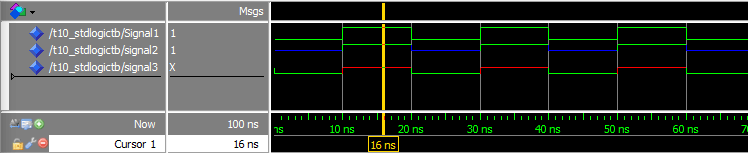

Форма сигнала с курсором, расположенным на другой части повторяющегося цикла сигнала:

Анализ

Упражнение продемонстрировало, как функция разрешения VHDL работает с кодом std_logic. тип. При работе с цифровой логикой часто практичнее изучать временную шкалу в виде сигнала. вместо использования распечаток. Поэтому мы использовали сигнал ModelSim для проверки значений сигнала в этом упражнении.

Первый процесс и Signal1 используется только для изменения значения, которое третий процесс использует для Signal2 и Signal3 .

Второй процесс, Драйвер A, попытается управлять 'Z'. на Signal2 и '0' на Signal3 постоянно.

Третий процесс, Драйвер B, будет попеременно управлять '1' и 'Z' на оба Signal2 и Signal3 .

На снимках экрана мы видим, что Signal1 изменяется между '0' и '1' , потому что только один процесс пытается управлять этим сигналом. Мы также можем видеть, что сигналы нескольких драйверов разрешаются в соответствии с таблицей разрешений, опубликованной в комментариях к коду VHDL:

| Сигнал | Водитель А | Водитель Б | Результат |

|---|---|---|---|

| Сигнал2 | "З" | "З" | "З" |

| Сигнал2 | "З" | "1" | "1" |

| Сигнал3 | '0' | "З" | '0' |

| Сигнал3 | '0' | "1" | 'X' |

Вывод

std_logicнаиболее распространенный тип, используемый для хранения однобитового значения в VHDL.- Подумайте о

std_logicсигнал как физический провод в нашем цифровом дизайне - Если несколько процессов пытаются управлять

std_logicсигнала, его значение определяется таблицей разрешений

Перейти к следующему руководству »

VHDL

- Наиболее распространенные узкие места в рабочем процессе 3D-печати - и как их исправить

- Наиболее распространенные проблемы с системой охлаждения автомобиля

- Как максимально использовать свои данные

- Как создать связанный список в VHDL

- Как использовать процедуру в процессе в VHDL

- Как использовать нечистую функцию в VHDL

- Как использовать функцию в VHDL

- Как безопасно использовать подъемный механизм на рабочем месте

- Наиболее распространенные причины аварий кранов (и как их избежать)

- Наиболее распространенные приложения a286