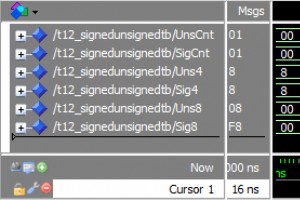

Типы со знаком и без знака в VHDL являются битовыми векторами, как и тип std_logic_vector. Разница в том, что хотя std_logic_vector отлично подходит для реализации шин данных, он бесполезен для выполнения арифметических операций. Если вы попытаетесь добавить любое число к типу std_logic_vector, Mod

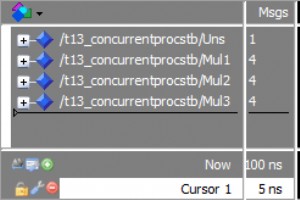

Параллельный оператор в VHDL — это назначение сигнала в архитектуре, но вне обычной конструкции процесса. Параллельный оператор также называется параллельным присваиванием или параллельным процессом. Когда вы создаете параллельный оператор, вы фактически создаете процесс с определенными, четко опре

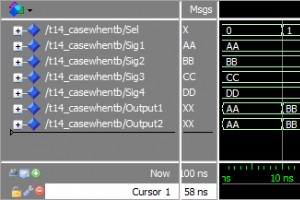

Оператор Case-When заставит программу выбрать один из нескольких различных путей, в зависимости от значения сигнала, переменной или выражения. Это более элегантная альтернатива оператору If-Then-Elsif-Else с несколькими операторами Elsif. В других языках программирования есть похожие конструкции, и

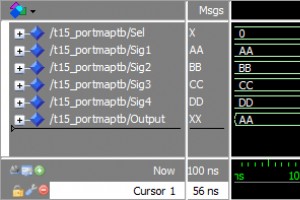

Модуль — это автономная единица кода VHDL. Модули взаимодействуют с внешним миром через сущность. . Карта порта это часть инстанцирования модуля, где вы объявляете, к каким локальным сигналам должны быть подключены входы и выходы модуля. В предыдущих уроках этой серии мы писали весь наш код в основ

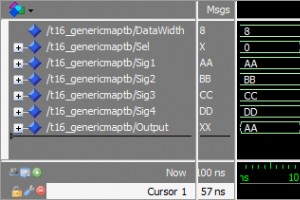

Создание модулей — отличный способ повторного использования кода, но часто вам нужен один и тот же модуль с меньшими вариациями в вашем дизайне. Это то, для чего предназначены дженерики и универсальная карта. Это позволяет сделать определенные части модуля настраиваемыми во время компиляции. Конста

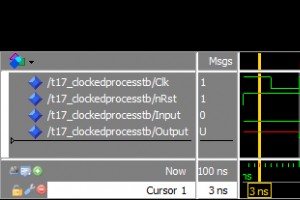

В подавляющем большинстве проектов VHDL используется логика синхронизации. , также известный как синхронная логика или последовательная логика . Синхронизированный процесс запускается только главным тактовым сигналом, а не при изменении любого другого входного сигнала. Основным строительным блоком

Проверьте свой прогресс с помощью этой викторины VHDL после прохождения учебных пособий 12–17 из серии базовых учебных пособий по VHDL! Какое утверждение о знаковом типе верно? Они могут представляют более высокие значения, чем беззнаковые типы Если крайний левый бит равен 1, значение должно

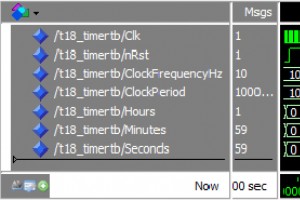

В предыдущих уроках мы использовали wait for оператор для задержки времени в моделировании. А как же производственные модули? wait for оператор не может быть использован для этого. Это работает только в моделировании, потому что мы не можем просто сказать электронам в цепи остановиться на заданное в

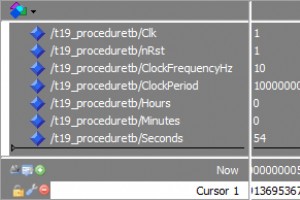

Процедура — это тип подпрограммы в VHDL, которая помогает избежать повторения кода. Иногда возникает необходимость выполнить одинаковые операции в нескольких местах по всей конструкции. Хотя создание модуля может быть излишним для мелких операций, часто вам нужна процедура. Процедуры могут быть объ

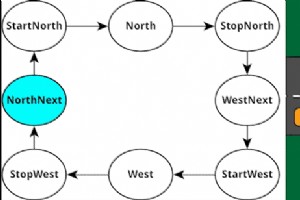

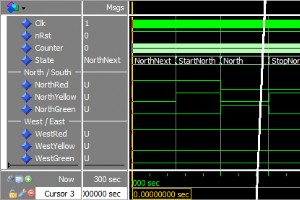

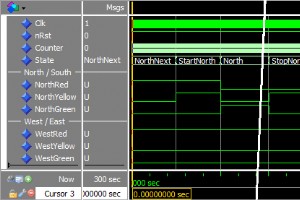

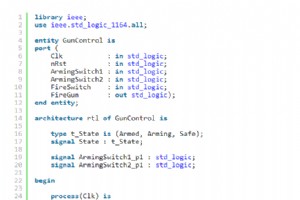

Конечный автомат (FSM) — это механизм, выходные данные которого зависят не только от текущего состояния ввода, но и от прошлых входных и выходных значений. Всякий раз, когда вам нужно создать какой-то зависящий от времени алгоритм на VHDL или если вы сталкиваетесь с проблемой реализации компьютерно

Функции — это подпрограммы на VHDL, которые можно использовать для реализации часто используемых алгоритмов. Функция принимает ноль или более входных значений и всегда возвращает значение. В дополнение к возвращаемому значению функция отличается от процедуры тем, что она не может содержать операторы

Нечистая функция может читать или записывать любой сигнал в пределах своей области действия, даже те, которых нет в списке параметров. Мы говорим, что функция имеет побочные эффекты . Под побочными эффектами мы подразумеваем, что не гарантируется, что функция будет возвращать одно и то же значение

Можно управлять внешними сигналами из процедуры. Пока сигнал находится в рамках процедуры, к нему можно получить доступ для чтения или записи, даже если он не указан в списке параметров. Процедуры, объявленные в декларативной области архитектуры, не могут управлять никакими внешними сигналами. Это

Проверьте свои успехи с помощью этой викторины VHDL после прохождения части 4 из серии основных учебных пособий по VHDL! Как мы измеряем в реальном времени в VHDL? С помощью оператор ждать 1 нс По подсчету тактовые периоды Путем использования задержка распространения Правильный! Неправильны

Связный список — это динамическая структура данных. Связный список можно использовать, когда общее количество элементов заранее неизвестно. Он увеличивается и уменьшается в памяти в зависимости от количества содержащихся в нем элементов. Связные списки удобнее всего реализовать с помощью классов в

Самопроверяющийся тестовый стенд — это программа VHDL, которая проверяет правильность тестируемого устройства (DUT), не полагаясь на то, что оператор вручную проверит выходные данные. Тестовый стенд с самопроверкой работает полностью самостоятельно и в конце выводит сообщение «ОК» или «Не удалось».

Интерактивный испытательный стенд — это установка симулятора, при которой ввод данных в тестируемое устройство (ИУ) осуществляется оператором во время работы испытательного стенда. Чаще всего это будет означать, что вы вводите команды в консоли симулятора, чтобы предоставить тестируемому устройству

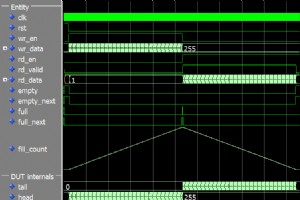

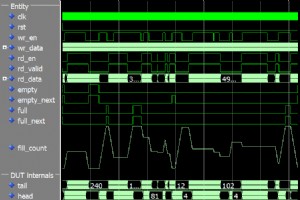

Циклические буферы — популярные конструкции для создания очередей в последовательных языках программирования, но они также могут быть реализованы аппаратно. В этой статье мы создадим кольцевой буфер на VHDL для реализации FIFO в блочной оперативной памяти. При реализации FIFO вам придется принять м

Ограниченная случайная проверка — это стратегия тестового стенда, основанная на генерации псевдослучайных транзакций для тестируемого устройства (DUT). Цель состоит в том, чтобы обеспечить функциональный охват ряда предопределенных событий за счет случайного взаимодействия с тестируемым устройством.

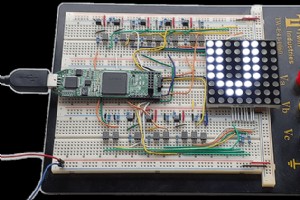

Я рад сообщить, что курс VHDL и FPGA, над которым я работал последние шесть месяцев, начинает завершаться. В настоящее время курс находится в стадии бета-тестирования, и я планирую запустить его впервые этой осенью. Для кого предназначен курс FPGA? Курс FPGA предназначен для разработчиков, знакомых

VHDL