Как использовать создание экземпляра карты портов в VHDL

Модуль — это автономная единица кода VHDL. Модули взаимодействуют с внешним миром через сущность. . Карта порта это часть инстанцирования модуля, где вы объявляете, к каким локальным сигналам должны быть подключены входы и выходы модуля.

В предыдущих уроках этой серии мы писали весь наш код в основном файле VHDL, но обычно мы этого не делали. Мы создаем логику с целью использования ее в конструкции FPGA или ASIC, а не для симулятора.

Модуль VHDL, созданный для работы в симуляторе, обычно не имеет входных и выходных сигналов. Он полностью автономен. Вот почему сущность наших проектов была пустой. Между entity ничего не было тег и end entity; тег.

Эта запись в блоге является частью серии учебных пособий по основам VHDL.

Модуль без каких-либо входных или выходных сигналов не может использоваться в реальном проекте. Его единственная цель — позволить нам запускать код VHDL в симуляторе. Поэтому он называется тестбенч. . Чтобы смоделировать модуль с входными и выходными сигналами, мы должны создать экземпляр это на тестовом стенде.

Модули и тестбенчи часто идут парами и хранятся в разных файлах. Обычная схема именования состоит в том, чтобы называть testbench именем модуля с добавлением «Tb» и называть архитектуру «sim». Если модуль называется «MyModule», тестовый стенд будет называться «MyModuleTb». Следовательно, имена файлов становятся «MyModuleTb.vhd» и «MyModule.vhd».

С помощью кода тестового стенда мы можем проверить правильность работы модуля в среде моделирования. Тестируемый модуль обычно называют тестируемым устройством. (ДУТ).

Модули также могут быть созданы внутри других модулей. Разделение кода на модули позволяет создавать его несколько раз. Вы можете создать несколько экземпляров модуля в одном дизайне, и его можно повторно использовать во многих проектах.

Синтаксис объекта с портом в VHDL:entity <entity_name> is

port(

<entity_signal_name> : in|out|inout <signal_type>;

...

);

end entity;

Синтаксис для создания экземпляра такого модуля в другом файле VHDL:<label> : entity <library_name>.<entity_name>(<architecture_name>) port map(

<entity_signal_name> => <local_signal_name>,

...

);

<label> может быть любым именем, и оно будет отображаться в окне иерархии в ModelSim. <library_name> для модуля устанавливается в симуляторе, а не в коде VHDL. По умолчанию каждый модуль компилируется в work библиотека. <entity_name> и <architecture_name> должен соответствовать модулю, экземпляр которого мы создаем. Наконец, каждый из сигналов объекта должен быть сопоставлен с именем локального сигнала.

Существуют и другие способы создания экземпляра модуля в VHDL, но это основной синтаксис для явного создания экземпляра.

Упражнение

В этом видеоуроке мы узнаем, как создать и создать экземпляр модуля в VHDL:

Окончательный код для testbench MUX :

library ieee;

use ieee.std_logic_1164.all;

use ieee.numeric_std.all;

entity T15_PortMapTb is

end entity;

architecture sim of T15_PortMapTb is

signal Sig1 : unsigned(7 downto 0) := x"AA";

signal Sig2 : unsigned(7 downto 0) := x"BB";

signal Sig3 : unsigned(7 downto 0) := x"CC";

signal Sig4 : unsigned(7 downto 0) := x"DD";

signal Sel : unsigned(1 downto 0) := (others => '0');

signal Output : unsigned(7 downto 0);

begin

-- An instance of T15_Mux with architecture rtl

i_Mux1 : entity work.T15_Mux(rtl) port map(

Sel => Sel,

Sig1 => Sig1,

Sig2 => Sig2,

Sig3 => Sig3,

Sig4 => Sig4,

Output => Output);

-- Testbench process

process is

begin

wait for 10 ns;

Sel <= Sel + 1;

wait for 10 ns;

Sel <= Sel + 1;

wait for 10 ns;

Sel <= Sel + 1;

wait for 10 ns;

Sel <= Sel + 1;

wait for 10 ns;

Sel <= "UU";

wait;

end process;

end architecture;

Окончательный код модуля MUX. :

library ieee;

use ieee.std_logic_1164.all;

use ieee.numeric_std.all;

entity T15_Mux is

port(

-- Inputs

Sig1 : in unsigned(7 downto 0);

Sig2 : in unsigned(7 downto 0);

Sig3 : in unsigned(7 downto 0);

Sig4 : in unsigned(7 downto 0);

Sel : in unsigned(1 downto 0);

-- Outputs

Output : out unsigned(7 downto 0));

end entity;

architecture rtl of T15_Mux is

begin

process(Sel, Sig1, Sig2, Sig3, Sig4) is

begin

case Sel is

when "00" =>

Output <= Sig1;

when "01" =>

Output <= Sig2;

when "10" =>

Output <= Sig3;

when "11" =>

Output <= Sig4;

when others => -- 'U', 'X', '-', etc.

Output <= (others => 'X');

end case;

end process;

end architecture;

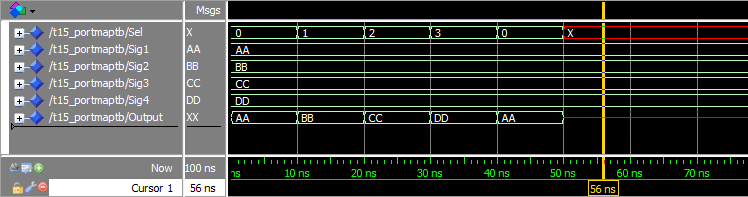

Окно сигнала в ModelSim после того, как мы нажали кнопку «Выполнить» и увеличили временную шкалу:

Анализ

Как мы видим из сигнала, модуль мультиплексора (MUX) работает должным образом. Форма волны идентична форме из предыдущего урока, которую мы создали без использования модулей.

Теперь существует четкое разделение между модулем проектирования и тестовым стендом. Модуль, содержащий MUX, — это то, что мы собираемся использовать в проекте, и единственная цель тестового стенда — позволить нам запустить его в симуляторе. В тестовом стенде есть процесс, который использует wait инструкции для создания искусственных временных задержек в моделировании. Модуль дизайна не имеет понятия о времени, он реагирует только на внешние раздражители.

Мы назвали архитектуру тестового стенда sim , для имитации. Архитектура модуля дизайна получила название rtl , что означает уровень регистрации-передачи. Это просто соглашения об именах. Когда видишь файл с таким названием, сразу понимаешь, это тестовый стенд или модуль дизайна. У разных компаний могут быть разные соглашения об именах.

Вывод

- Входные и выходные сигналы указаны в объекте модуля

- Модуль без входных/выходных сигналов называется тестовым стендом. , и его можно использовать только в симуляторе

- Модуль с входными/выходными сигналами обычно нельзя запустить непосредственно в симуляторе.

Перейти к следующему руководству »

VHDL

- Как мы используем молибден?

- Как создать список строк в VHDL

- Как создать управляемый Tcl тестовый стенд для модуля кодовой блокировки VHDL

- Как остановить симуляцию в тестовом стенде VHDL

- Как создать ШИМ-контроллер на VHDL

- Как генерировать случайные числа в VHDL

- Как использовать процедуру в процессе в VHDL

- Как использовать нечистую функцию в VHDL

- Как использовать функцию в VHDL

- Как использовать шлифовальный станок