Вместо константных выражений можно использовать математические функции Verilog, которые поддерживают как целые и настоящие математика. Целые математические функции Функция $clog2 возвращает потолок log2 данного аргумента. Обычно это используется для вычисления минимальной ширины, необходимой для а

Отображение системных задач в основном используется для отображения информационных и отладочных сообщений для отслеживания потока моделирования из файлов журнала, а также помогает ускорить отладку. Существуют разные группы задач отображения и форматов, в которых они могут печатать значения. Отображ

Часы необходимы для создания цифровых схем, поскольку они позволяют различным блокам синхронизироваться друг с другом. Свойства часов Ключевыми свойствами цифровых часов являются их частота. который определяет период часов , его рабочий цикл и фаза часов относительно других часов. Часовой период Ч

Дизайн и тестовый стенд Verilog обычно содержат много строк кода, состоящих из always. или initial блоки, непрерывные присваивания и другие процедурные операторы, которые становятся активными в разное время в ходе моделирования. Каждое изменение значения сигнала в модели Verilog считается событием

Моделирование Verilog зависит от того, как определяется время, потому что симулятор должен знать, что означает № 1 с точки зрения времени. `timescale директива компилятора указывает единицу времени и точность для следующих за ней модулей. Синтаксис `timescale <time_unit>/<time_precisio

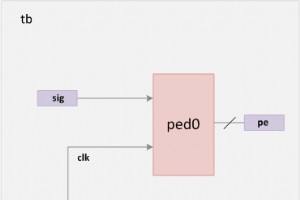

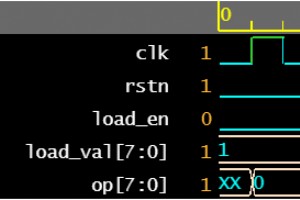

Verilog — это язык описания оборудования, и разработчикам не требуется моделировать свои RTL-проекты, чтобы иметь возможность преобразовывать их в логические вентили. Так в чем же необходимость симуляции? Моделирование — это метод применения различных входных воздействий к дизайну в разное время,

Стандартные примитивы Verilog, такие как nand и not не всегда может быть простым или достаточным для представления сложной логики. Новые примитивные элементы под названием UDP или пользовательские примитивы можно определить для моделирования комбинационной или последовательной логики. Все UDP имеют

Verilog также обеспечивает поддержку моделирования на уровне транзисторов, хотя в наши дни разработчики редко используют его, поскольку сложность схем требует от них перехода к более высоким уровням абстракции, а не к моделированию на уровне переключателей. НМОП/ПМОП module des (input d, ctrl,

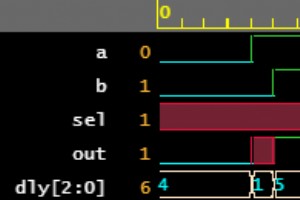

Цифровые элементы являются двоичными объектами и могут содержать только одно из двух значений — 0 и 1. Однако переход от 0 к 1 и от 1 к 0 имеет переходную задержку, как и каждый вентильный элемент для распространения значения от входа к выходу. Например, логический элемент И с двумя входами должен

Некоторые из основных встроенных примитивов обсуждались в предыдущей статье, и было бы неплохо увидеть несколько практических примеров использования простого and. , nor и not ворота. Обратите внимание, что для написания кода Verilog с использованием вентилей вам необходимо знать, как соединять элем

Большинство цифровых проектов выполняются на более высоком уровне абстракции, таком как RTL, хотя иногда становится интуитивно понятно создавать более мелкие детерминированные схемы на более низком уровне с использованием комбинационных элементов, таких как и и или . Моделирование, выполняемое на эт

Большинство языков программирования имеют характерную особенность, называемую scope. который определяет видимость определенных разделов кода для переменных и методов. Область определяет пространство имен чтобы избежать конфликтов между разными именами объектов в одном пространстве имен. Verilog опр

Операторы задержки Verilog могут иметь задержки, указанные либо в левой, либо в правой части оператора присваивания. Задержки между назначениями // Delay is specified on the left side #<delay> <LHS> = <RHS> взаимное назначение Оператор задержки имеет значение задержки в лев

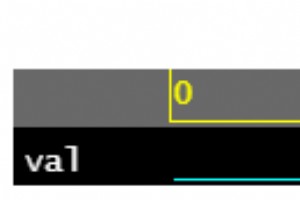

В Verilog есть два типа контроля времени:задержка и событие выражения. задержка управление — это просто способ добавить задержку между моментом, когда симулятор встречает оператор, и моментом его фактического выполнения. Выражение события позволяет отложить оператор до возникновения некоторого событ

Verilog поддерживает несколько директив компилятора, которые по существу предписывают компилятору обрабатывать код определенным образом. Например, часть кода может представлять собой реализацию определенной функции, и должен быть какой-то способ не включать код в дизайн, если эта функция не использу

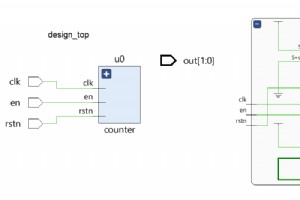

Параметры — это конструкции Verilog, которые позволяют повторно использовать модуль с другой спецификацией. Например, 4-битный сумматор может быть параметризован для приема значения количества битов, а новые значения параметров могут быть переданы во время создания экземпляра модуля. Таким образом,

А 04 предназначен для обработки входных данных и возврата единственного значения, тогда как 11 является более общим и может вычислять несколько значений результата и возвращать их с помощью output и вход тип аргументов. Задачи могут содержать элементы, отнимающие время моделирования, такие как @ , п

Часто мы обнаруживаем, что определенные фрагменты кода повторяются и вызываются несколько раз в RTL. В основном они не требуют времени моделирования и могут включать сложные вычисления, которые необходимо выполнять с различными значениями данных. В таких случаях мы можем объявить function и поместит

case Оператор проверяет, соответствует ли данное выражение одному из других выражений в списке, и соответственно переходит. Обычно он используется для реализации мультиплексора. Конструкция if-else может оказаться непригодной, если необходимо проверить множество условий, и будет синтезирована в коди

А for Цикл — это наиболее широко используемый цикл в программном обеспечении, но в основном он используется для реплицирования аппаратная логика в Verilog. Идея for Цикл состоит в повторении набора операторов, заданных в цикле, до тех пор, пока данное условие истинно. Это очень похоже на while цикла

Verilog

Покрытия и насосы в Джексоне, штат Мичиган

Соглашение о Boom Supersonic добавляет сверхзвуковые самолеты net-zero в глобальный флот United Airlines

Почему прослеживаемость продуктов важна в пищевой промышленности и производстве напитков

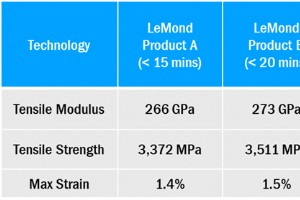

LeMond Carbon проверяет технологию быстрого окисления углеродного волокна