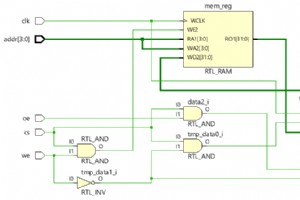

Дизайн module single_port_sync_ram # (parameter ADDR_WIDTH = 4, parameter DATA_WIDTH = 32, parameter DEPTH = 16 ) ( input clk, input [ADDR_WIDTH-1:0] addr, inout [DATA_WIDTH-1:0] data, input cs, input we, input oe ); re

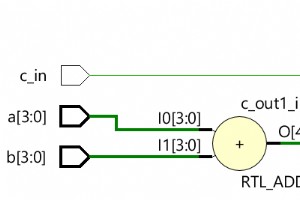

Сумматор — это цифровой компонент, выполняющий сложение двух чисел. Это основной компонент внутри ALU процессора, который используется для увеличения адресов, индексов таблиц, указателей буферов и во многих других местах, где требуется добавление. Полный сумматор добавляет входной перенос вместе с

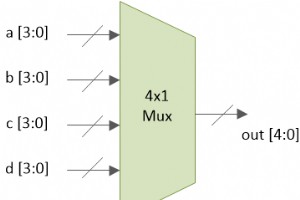

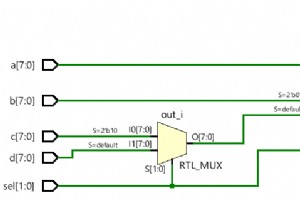

Что такое мультиплексор или мультиплексор? Мультиплексор или мультиплексор Короче говоря, это цифровой элемент, который передает данные с одного из N входов на выход на основе сигнала выбора. Ниже показан случай, когда N равно 4. Например, 4-битный мультиплексор будет иметь N входов по 4 бита, кажд

Дизайн 00 Схема оборудования Тестовый стенд 10

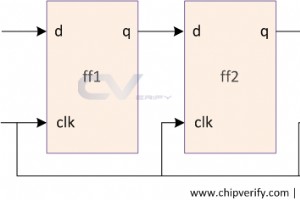

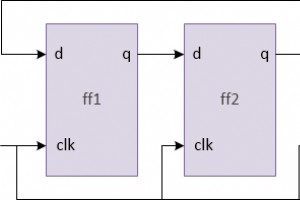

В цифровой электронике сдвиговый регистр представляет собой каскад триггеров, где выходной контакт q одного флопа подключается к контакту ввода данных (d) следующего. Поскольку все флопы работают с одними и теми же часами, битовый массив, хранящийся в сдвиговом регистре, сдвинется на одну позицию. Н

Дизайн module gray_ctr # (parameter N = 4) ( input clk, input rstn, output reg [N-1:0] out); reg [N-1:0] q; always @ (posedge clk) begin if (!rstn) begin q <= 0; out <= 0; end else begin q <= q + 1; `ifdef FOR_LOOP for (int i

Дизайн module modN_ctr # (parameter N = 10, parameter WIDTH = 4) ( input clk, input rstn, output reg[WIDTH-1:0] out); always @ (posedge clk) begin if (!rstn) begin out <= 0; end else begin if (out == N-1) out <= 0; else ou

Дизайн module johnson_ctr #(parameter WIDTH=4) ( input clk, input rstn, output reg [WIDTH-1:0] out ); always @ (posedge clk) begin if (!rstn) out <= 1; else begin out[WIDTH-1] <= ~out[0]; for (int i = 0; i < WIDTH-1; i=i+1

Дизайн module ring_ctr #(parameter WIDTH=4) ( input clk, input rstn, output reg [WIDTH-1:0] out ); always @ (posedge clk) begin if (!rstn) out <= 1; else begin out[WIDTH-1] <= out[0]; for (int i = 0; i < WIDTH-1; i=i+1) b

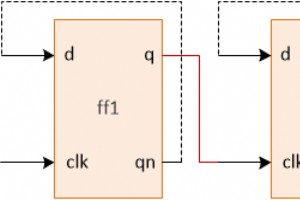

рябь counter — это асинхронный счетчик, в котором все флопы, кроме первого, синхронизируются с выходом предыдущего флопа. Дизайн module dff ( input d, input clk, input rstn, output reg q, output qn); always @ (posedge clk or neg

4-битный счетчик начинает увеличиваться с 4b0000 до 4h1111, а затем возвращается к 4b0000. Он будет продолжать считать до тех пор, пока у него есть работающие часы, а сброс удерживается на высоком уровне. Ролловер происходит, когда отбрасывается самый старший бит последнего добавления. Когда счетчи

Триггер захватывает данные на своем входе по положительному или отрицательному фронту тактового сигнала. Важно отметить, что все, что происходит с данными после фронта тактового сигнала до следующего фронта тактового сигнала, не будет отражено в выводе. защелка с другой стороны, не захватывает край

Дизайн 06 Тестовый стенд 15 Журнал моделирования 23

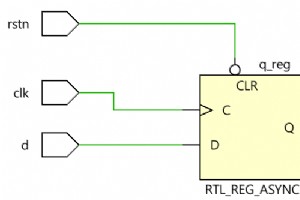

D-триггер это последовательный элемент, который следует за входным выводом d на заданном краю часов. Дизайн № 1:с асинхронным сбросом с активным низким уровнем 06 Схема оборудования Тестовый стенд 15 Дизайн № 1:с активным сбросом синхронизации 23 Схема оборудования Тестовый стенд 37

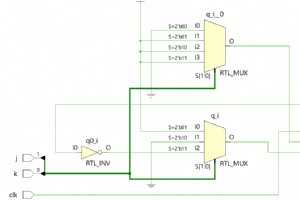

Дизайн module jk_ff ( input j, input k, input clk, output q); reg q; always @ (posedge clk) case ({j,k}) 2b00 : q <= q; 2b01 : q <= 0; 2b10 : q <= 1; 2b11 : q <= ~q; endcase endmodule Схе

Всегда лучше начинать с очень простого примера, и ни один из них не подходит лучше всего, кроме Hello World!. // Single line comments start with double forward slash // // Verilog code is always written inside modules, and each module represents a digital block with some functionality module tb

Verilog имеет системные задачи и функции, которые могут открывать файлы, выводить значения в файлы, считывать значения из файлов и загружать в другие переменные и закрывать файлы. Открытие и закрытие файлов 06 Режимы открытия файла Аргумент Описание r или rb Открыть для чтения w или wb Создать

Шкала времени по умолчанию Хотя ожидается, что модули Verilog будут иметь шкалу времени, определенную перед модулем, симуляторы могут вставлять шкалу времени по умолчанию. Фактическую шкалу времени, которая применяется в любой области в разработанной Verilog иерархии, можно распечатать с помощью си

Директива временной шкалы Verilog указывает единицу измерения времени и точность моделирования. Верилог $timeformat системная функция указывает %t стиль сообщения спецификатора формата в операторах отображения, таких как $display и $strobe . Синтаксис $timeformat(<unit_number>, <preci

Вместо константных выражений можно использовать математические функции Verilog, которые поддерживают как целые и настоящие математика. Целые математические функции Функция $clog2 возвращает потолок log2 данного аргумента. Обычно это используется для вычисления минимальной ширины, необходимой для а

Verilog