Дельта-сигма-модулятор с непрерывным временным диапазоном и динамическим диапазоном 80 дБ с полосой пропускания 100 МГц и тактовой частотой 2,4 ГГц

Аннотация

Полоса пропускания Δ Σ Модулятор ограничен тактовой частотой из-за требования передискретизации. Поскольку наноразмерные КМОП процессы быстро развиваются, можно разработать широкую полосу пропускания и широкий динамический диапазон с непрерывным временем Δ Σ модуляторы для высокочастотных приложений. В этой статье предлагается 4-битовый непрерывный алгоритм 3-го порядка Δ Σ модулятор с одноконтурной топологией с прямой связью. Этот модулятор разработан по технологии КМОП с длиной волны 40 нм и обеспечивает динамический диапазон 80 дБ и полосу пропускания 100 МГц при тактовой частоте 2,4 ГГц. Модулятор потребляет 69,7 мВт от источника питания 1,2 В.

Введение

В связи с растущими требованиями к приложениям беспроводной связи, таким как стандарты сотовой связи, аналого-цифровые преобразователи (АЦП) быстро развиваются, чтобы поддерживать более высокую полосу пропускания сигнала (BW) и динамический диапазон (DR). Требование BW в стандарте связи Long-Term-Evolution Advanced (LTE-A) возросло до 100 МГц. АЦП Найквиста, обычно конвейерные АЦП [1, 2], использовались в макробазовых станциях из-за их высокой полосы пропускания. Однако незаменимые входные буферы для управления переключаемыми входными конденсаторами с ограничением теплового шума и сглаживающий фильтр приводят к значительному энергопотреблению и сложности конструкции. Более того, тот факт, что конвейерные АЦП полагаются на точное межкаскадное усиление, которое определяет широкополосный остаточный усилитель с высоким коэффициентом усиления и технологию калибровки, приводит к сложности и рассеиванию мощности. Δ Σ АЦП известны своей высокой производительностью и энергоэффективностью за счет использования технологии передискретизации и шумоподавления. Однако требование коэффициентов передискретизации (OSR), которое обычно превышает 16 [3–6], определяет частоту дискретизации за пределами ГГц. Недавно Δ Σ Были предложены АЦП с полосой пропускания более 50 МГц с использованием наноразмерных КМОП-процессов, которые обеспечивают тактовую частоту до нескольких ГГц. Ранее высокая частота Δ Σ АЦП обычно используют реализации с непрерывным временем (CT) [3–9] вместо реализаций с дискретным временем (DT). Последний реализуется схемой переключаемого конденсатора, и его точность зависит от согласования конденсаторов, что означает надежную работу при изменении процесса. Кроме того, обеспечивается превосходная устойчивость к джиттеру тактовых импульсов, поскольку постоянные времени конденсаторов и переключателей достаточно малы. Однако, поскольку операция выборки выполняется перед модулятором, необходим фильтр сглаживания. С другой стороны, из-за требования к установке для обеспечения стабильности в каскадах операционные усилители в модуляторах DT реализованы с более широкой полосой пропускания с единичным усилением (UGBW), чем модуляторы CT. Таким образом, модуляторы DT могут обеспечивать высокую точность, но узкий сигнал [10, 11] и широко используются для реализации измерительных приложений, таких как интеллектуальные датчики и биомедицинская визуализация. Напротив, были более широкие попытки разработать модуляторы ТТ для высокочастотных приложений, чем модуляторы ТТ с сопоставимой сложностью и потребляемой мощностью.

Требуемая цель проектирования - более высокая BW в данном процессе определяет более низкий OSR из-за ограниченной тактовой частоты процесса. Для достижения достаточного DR требуется агрессивное формирование шума, реализованное с помощью высокого порядка передаточной функции шума, которое обычно выполняется каскадом петлевых фильтров и обычно равно или больше 3 в предыдущих работах. Однако увеличенные порядки контурных фильтров вызывают энергопотребление, нестабильность и сложность конструкции. Архитектура многокаскадного формирования шума (MASH) [6, 8], реализованная каскадным локальным управлением низкого порядка Δ Σ модуляторы без обратной связи друг с другом использовались для устранения проблем со стабильностью, но с чувствительностью к рассогласованию. Более того, модулятор с многобитовым квантователем получает условно высокий DR с экспоненциально увеличивающейся величиной компаратора.

В этой статье описывается модулятор CT в 40 нм CMOS, который обеспечивает 80 DR на полосе пропускания 100 МГц с потреблением 69,7 мВт с использованием процесса CMOS 40 нм. Эта статья организована следующим образом. В разделе «Метод» описывается топология модулятора и реализация схемы. В разделе «Результаты и обсуждение» показаны смоделированные результаты, а в разделе «Заключение» приводится краткое изложение этой работы.

Метод

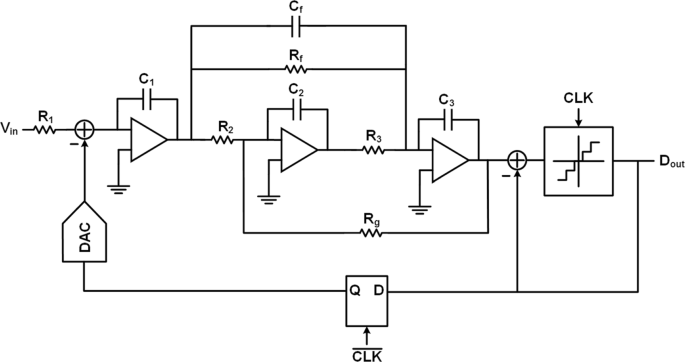

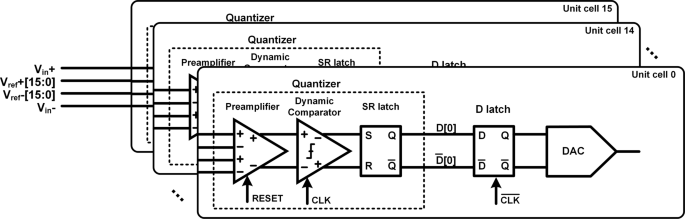

На рисунке 1 представлена общая схема предлагаемого ТТ 3-го порядка Δ Σ модулятор с несимметричной структурой для упрощения. Формирование шума 3-го порядка представляет собой отличный компромисс между динамическим диапазоном и стабильностью контура. Предлагаемый модулятор имеет частоту дискретизации 2,4 ГГц с OSR 12. Относительно высокий OSR в Δ Σ модуляторы с полосой пропускания более 100 МГц обеспечивают высокое динамическое сопротивление. Модулятор содержит три интегратора RC, 4-битный квантователь и 4-битный ЦАП с регулированием тока. Интеграторы реализованы в виде инновационных усилителей с прямой связью с малой мощностью рассеяния, обеспечивающих высокую энергоэффективность. ЦАП с обратной связью имеет дополнительную задержку на половину периода дискретизации, чтобы ослабить требования квантователя к метастабильности. Путь быстрой обратной связи, реализованный пассивным сумматором и управляемый непосредственно квантователем, реализует компенсацию избыточной задержки контура (ELD). Топология с прямой связью используется для повышения энергоэффективности за счет функции передачи внеполосного сигнала.

Общая схема предлагаемого одноконтурного 4-битного ТТ 3-го порядка Δ Σ модулятор с прямой топологией

Дизайн усилителя

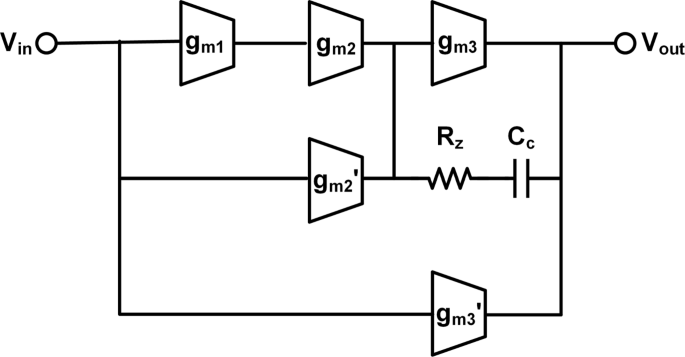

Требуется высокий коэффициент усиления усилителя в Δ Σ модуляторы для обеспечения желаемой функции преобразования шума. Однако наноразмерные технологии, используемые для достижения тактовой частоты в несколько ГГц, страдают низким внутренним усилением. Поэтому для реализации достаточного усиления по постоянному току используется трехкаскадный усилитель, как показано на рис. 2. Топология с прямой связью и компенсация Миллера объединены для улучшения запаса по фазе без уменьшения полосы пропускания единичного усиления. Усилители с прямой связью были одним из популярных решений для достижения высокого усиления с адекватным UGBW и запасом по фазе (PM). Нуль в левой полуплоскости, вызванный трактом прямой связи, должен эффективно нейтрализовать отрицательный фазовый сдвиг полюсов. Это требует высокой крутизны усилителей в тракте прямой связи и потребляет значительную мощность. Преимущественная схема повторного использования тока смещения позволяет экономить электроэнергию, в то время как она ограничивает g . м ценности. Недостаточно г м обычно приводит к нулю за пределами UGBW и не может обеспечить адекватный запас по фазе. Оптимизированный ноль, расположенный ниже общего UGBW, обеспечивается добавлением компенсирующего конденсатора Миллера и резистора обнуления.

Топология предлагаемого трехкаскадного усилителя прямой связи с компенсацией Миллера

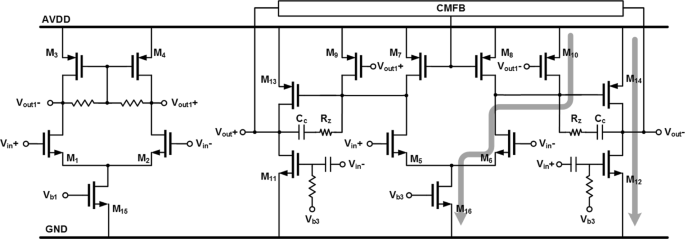

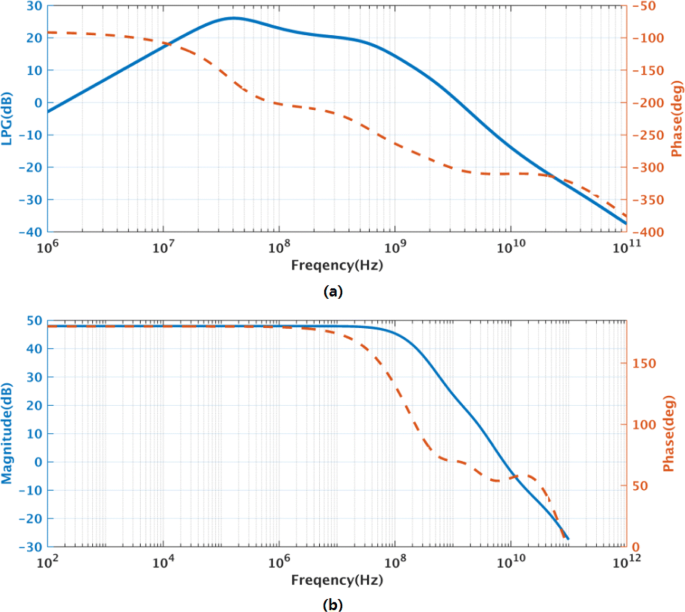

На рисунке 3 показана схема транзисторного уровня усилителя, используемого в первом интеграторе. Транзисторы M 1–4 образуют входной каскад усилителя, а транзисторы M 9,10 и M 13,14 образуют соответственно вторую и третью ступени. Транзисторы M 5-8 и M 11,12 создать два высокоскоростных тракта с прямой связью между входом и выходом, разделяя токи смещения с усилителями второго и третьего каскада. Синфазный выход первого каскада (CM) фиксируется локально. Выход CM второго и третьего каскада фиксируется путем обратной связи второго каскада через усилитель CMFB, M 7,8 и M 13,14 . На рис. 4а показан смоделированный отклик без обратной связи усилителя первого интегратора после компоновки при полной нагрузке, а на рис. 4b показан отклик без обратной связи. Первый интегратор достигает 3,6 ГГц UGBW и 57,8 ∘ PM со всем эффектом нагрузки при потреблении 10,5 мВт от источника питания 1,2 В. Второй и третий интеграторы используют ту же топологию, но с масштабированными токами смещения, достигая UGBW 4,7 и 3,3 ГГц и PM 58,0 и 57,8 ∘ при потреблении 4,3 и 17,3 мВт соответственно.

Схема усилителя на уровне транзистора

Пост-макет смоделировал результаты усилителя в 1-м интеграторе. а Отклик на переменный ток без обратной связи; б Реакция на переменный ток с обратной связью

Квантизатор и ЦАП

Как показано на схеме квантователя и ЦАП на рис. 5, каждый состоит из 16 элементарных ячеек. Квантователь реализован в виде 4-разрядного флэш-АЦП с 16-уровневым кодером, генерируемым из 17-ступенчатой резистивной лестницы. Квантователь, продолжительность работы которого согласно требованиям ELD составляет менее половины периода выборки, чтобы гарантировать стабильность цикла, является ключевым блоком, ограничивающим максимальную полосу пропускания.

Упрощенная схема квантователей и ЦАП

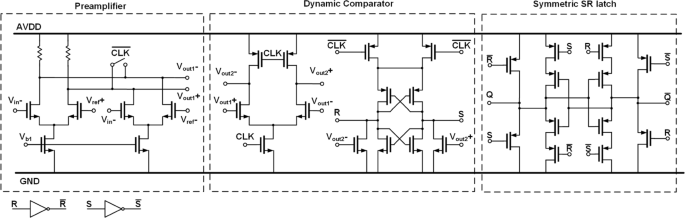

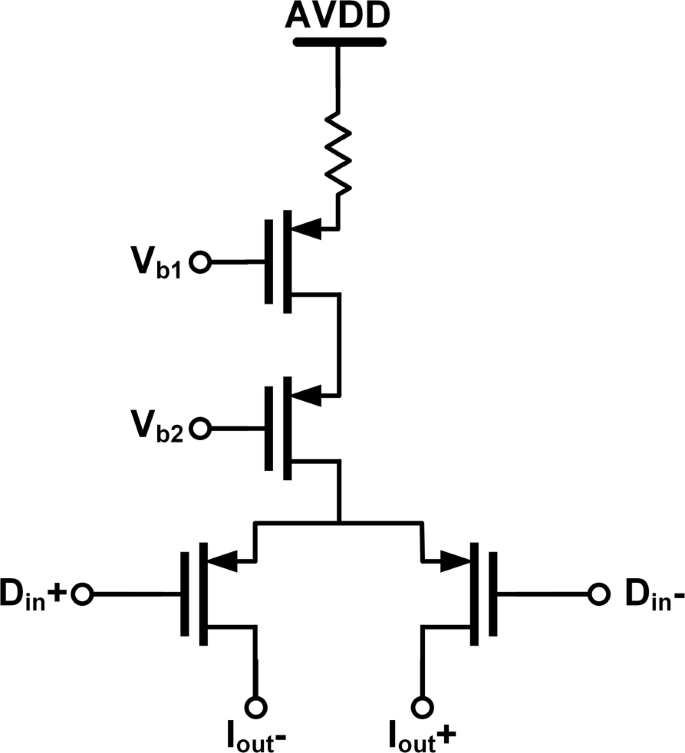

Для реализации высокоскоростных импульсных АЦП используется трехступенчатая архитектура компаратора, состоящая из каскада предусилителя, каскада динамического компаратора и симметричной защелки установки и сброса (SR) [12], показанной на рис. 6. Предварительный усилитель для уменьшения смещения, относящегося к входу, представляет собой две дифференциальные пары резистивной нагрузки с переключателем сброса, подключенным к выходам для быстрого восстановления. В отличие от обычных динамических компараторов, дифференциальная пара и инверторы с перекрестной связью разделены на две части, чтобы минимизировать количество транзисторов на каждом пути тока для низковольтных источников питания. Когда часы переключаются на высокий уровень, динамические компараторы начинают принимать решение о сравнении, зависящем от входа. Затем оба выхода каждого динамического компаратора сбрасываются в 0 по мере того, как возврат тактового сигнала переходит с высокого на низкий, запуская регенерацию и фиксацию симметричной защелки SR. Поскольку активен только один транзистор в каждой ветви, симметричная структура защелки SR обеспечивает высокую способность управления нагрузкой. Это позволяет использовать транзистор небольшого размера со значительной скоростью выключения и низким энергопотреблением. Кроме того, это приводит к одинаковым задержкам обоих выходных сигналов. Защелки D перед модулями DAC имеют низкую чувствительность к уровню тактового сигнала, обеспечивая половину длительности ELD. Схема транзисторного уровня текущего блока ЦАП рулевого управления представлена на рис. 7.

Транзисторная схема одного единичного элемента предлагаемого квантователя

Элемент блока ЦАП текущего рулевого управления PMOS

Результаты и обсуждение

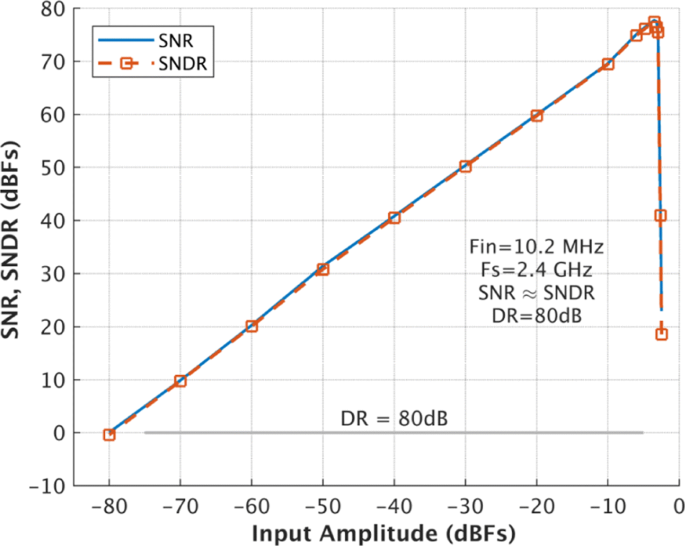

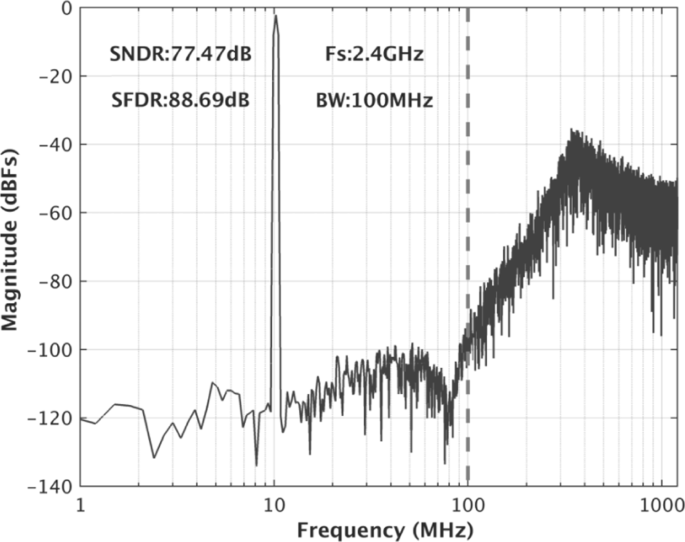

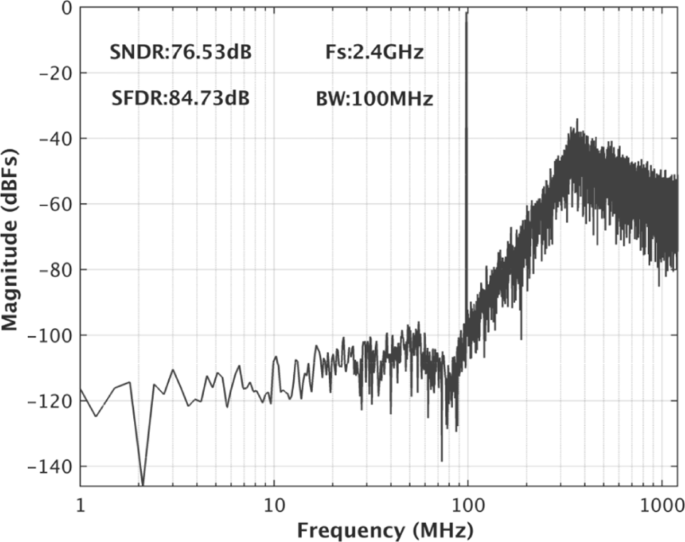

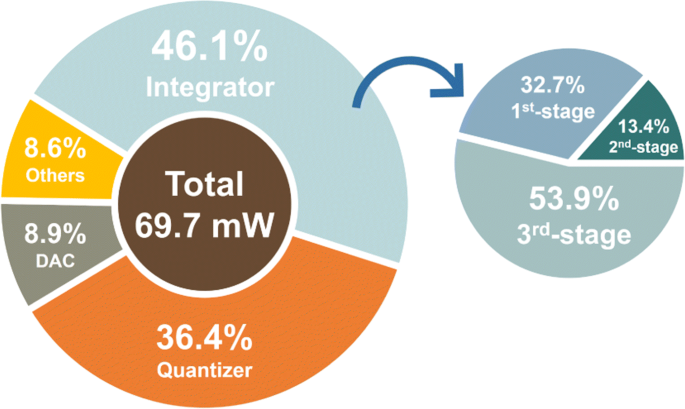

Прототип Δ Σ Модулятор построен по 40-нм КМОП-технологии. Поскольку результаты постмоделирования отношения сигнал / шум и SDNR в зависимости от входной амплитуды на частоте 10,2 МГц, показанные на рисунке 8, достигают 80 дБ DR. На рисунках 9 и 10 показаны смоделированные спектры с однотональным входом - 3,52 дБФ на частотах 10,2 и 97 МГц, соответственно, поскольку 0 дБФ соответствует полной шкале модулятора 2,4 В (пиковая амплитуда). SNDR составляет 77,47 дБ и 76,53 дБ соответственно. Как показано на рис. 11, потребление модулятора составляет 69,7 мВт. Интегратор, квантователь и ЦАП потребляют соответственно 32,1 мВт, 25,4 мВт и 6,2 мВт. Мощность 6,0 мВт потребляется другими токами, включая тактовые буферы, токовые смещения и опорные напряжения. Модулятор достигает FOM Шрайера 171,6 дБ на основе DR. В таблице 1 эта работа сравнивается с несколькими ранее опубликованными работами. Предлагаемый модулятор обеспечивает широкую полосу пропускания при самом высоком FOM.

Пост-моделирование SNR и SNDR в зависимости от амплитуды входного сигнала при входной частоте 10,2 МГц

Постмоделированные спектры с однотональным входом на частоте 10,2 МГц

Постмоделированные спектры с однотональным входом на 97 МГц

Постмоделированная разбивка энергопотребления

Заключение

В этой работе мы предложили 4-битный CT 3-го порядка Δ Σ модулятор с одноконтурной топологией с прямой связью. Этот модулятор разработан по 40-нм КМОП-технологии и обеспечивает динамическое восстановление 80 дБ в полосе пропускания 100 МГц при тактовой частоте 2,4 ГГц. Конструкция усилителя с малой мощностью рассеяния обеспечивает высокую энергоэффективность, а модулятор потребляет 69,7 мВт от источника питания 1,2 В и обеспечивает FOM Шрайера 171,6 дБ.

Доступность данных и материалов

Все данные, полученные или проанализированные в ходе этого исследования, включены в эту опубликованную статью.

Сокращения

- АЦП:

-

Аналого-цифровые преобразователи

- BW:

-

Пропускная способность

- CT:

-

Непрерывное время

- DR:

-

Динамический диапазон

- DT:

-

Дискретное время

- ELD:

-

Избыточная задержка петли

- LTE-A:

-

Продвинутое долгосрочное развитие

- OSR:

-

Коэффициенты передискретизации

- PM:

-

Запас по фазе

- UGBW:

-

Пропускная способность Unity-gain

Наноматериалы

- Самодельные простейшие часы Numitron IV9 с Arduino

- Высокоскоростная 3D-печать с AION500MK3

- Полный контроль терагерцовой поляризации с расширенной полосой пропускания через диэлектрические метапове…

- Изготовление наноразмерных ямок с высокой производительностью на полимерной тонкой пленке с использованием…

- Совместно модифицированные ТИМы RGO и трехмерных графеновых сетей с высокой производительностью

- Графен / полианилиновый аэрогель со сверхэластичностью и высокой емкостью в качестве высокостойкого к сжати…

- Преобразователь поляризации с управляемым двулучепреломлением на основе гибридной метаповерхности полност…

- Высокоэффективный гибридный кремниевый элемент с органической наноструктурой и измененной структурой пове…

- Чрезвычайно улучшенный отклик фототока в нанолистах топологического изолятора с высокой проводимостью

- Многофункциональное устройство с переключаемыми функциями преобразования поглощения и поляризации в тераг…