Ge pMOSFET с высокой подвижностью и пассивированием аморфным Si:влияние ориентации поверхности

Аннотация

Мы сообщаем об пассивации аморфным кремнием Ge pMOSFET, изготовленных на (001) -, (011) - и (111) -ориентированных поверхностях для усовершенствованных применений КМОП и тонкопленочных транзисторов. Пассивация Ge аморфным Si осуществляется магнетронным распылением при комнатной температуре. При фиксированной толщине Si t Si Ge pMOSFET с ориентацией (001) обеспечивает более высокий ток в открытом состоянии I ВКЛ и эффективная подвижность дырок μ eff по сравнению с устройствами других ориентаций. При инверсионной плотности заряда Q inv из 3,5 × 10 12 см −2 , Ge (001) транзисторы с размером 0,9 нм t Si продемонстрировать пик μ eff 278 см 2 / V × s, что в 2,97 раза выше универсальной подвижности Si. При уменьшении t Si , Я ВКЛ транзисторов Ge увеличивается из-за уменьшения эффективной толщины емкости, но характеристики подпорогового размаха и минимальной утечки ухудшаются из-за увеличения среднего зазора D это .

Фон

Германий (Ge) привлекает огромные исследовательские интересы в области применения передовых КМОП и тонкопленочных транзисторов из-за его более высокой подвижности отверстий и меньшего теплового баланса по сравнению с Si [1,2,3,4,5,6]. Для достижения высокой мобильности каналов перед формированием пакета затворов требуется процесс пассивации поверхности, ведущий к высокому качеству интерфейса. Несколько методов поверхностной пассивации были разработаны для обеспечения преимуществ подвижности носителей в полевых транзисторах Ge металл-оксид-полупроводник (MOSFET) [1, 2, 7,8,9,10]. Среди этих методов кремниевый (Si) колпачок, пассивированный на Ge, был горячим местом в последние годы из-за его преимуществ, заключающихся в эффективном подавлении интерфейсных состояний и хорошей термостабильности и надежности [11]. Формирование пассивирующего покрытия Si широко изучалось с помощью химического осаждения из газовой фазы (CVD) с прекурсорами SiH 4 [1], Si 2 H 6 [4], Si 3 H 8 [12] и электронно-лучевое испарение [13]. Хотя метод химического осаждения из паровой фазы может обеспечить более однородный пассивирующий слой по сравнению с физическим осаждением из паровой фазы (PVD), его скорость пассивирования имеет сильную корреляцию между ориентацией поверхности канала и температурой процесса. Технология PVD может обеспечить улучшенную скорость пассивации даже при комнатной температуре, которая имеет преимущества низкого теплового бюджета и низкой стоимости, что делает ее более подходящей для тонкопленочных транзисторов и приложений для интегрированной 3D-интеграции. В этом письме мы изготовили Ge pMOSFET с высокой подвижностью на (001) -, (011) - и (111) -ориентированных поверхностях с использованием пассивации аморфного Si методом магнетронного распыления. Значительно улучшенная эффективная подвижность дырок μ eff достигается в транзисторах Ge по сравнению с универсальной мобильностью Si. Влияние ориентации поверхности и толщины аморфного Si t Si на усиление эффекта пассивации аморфного Si на μ eff изучаются.

Методы

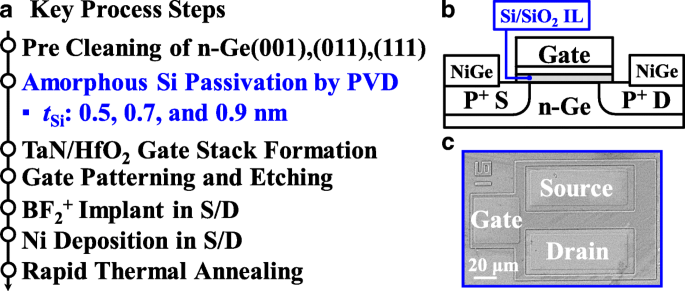

На рисунке 1а показаны основные этапы процесса изготовления Ge pMOSFET на поверхностях с ориентацией (001) -, (011) - и (111). После предварительной очистки затвора в разбавленном растворе HF (1:50) ультратонкий пассивирующий слой аморфного Si был нанесен на подложки n-Ge магнетронным распылением при целевой мощности 50 Вт. Три длительности пассивации:60 с, 80 с и 100 с. s использовались, соответствующие осаждению 0,5, 0,7 и 0,9 нм t si , соответственно. После этого HfO 2 толщиной 5 нм Диэлектрик затвора был нанесен при 250 ° C осаждением атомных слоев с использованием TDMAHf и H 2 O как предшественники Hf и O соответственно. Электрод затвора из TaN с длиной волны 50 нм был нанесен методом реактивного распыления. Затем на электрод затвора был нанесен рисунок и травление, за которым последовал BF 2 + имплантация в области истока / стока (S / D) при 30 кэВ с дозой 1 × 10 15 см - 2 . Несамоупорядоченные S / D-металлы из 15 нм никеля были сформированы методом отрыва. Наконец, был проведен быстрый термический отжиг при 400 ° C для активации легирующей примеси и S / D металлизации. На рисунке 1b показано поперечное сечение Ge pMOSFET с Si / SiO 2 . межфазный слой (ИС). На рис. 1с показано изображение изготовленного Ge pMOSFET, полученное с помощью микроскопа сверху.

а Последовательность процесса, показывающая основные этапы изготовления полевых МОП-транзисторов на основе Ge с различными значениями t Si . б Схема поперечного сечения Ge pMOSFET с SiO 2 IL. c Изображение изготовленного Ge pMOSFET, полученное с помощью микроскопа, вид сверху

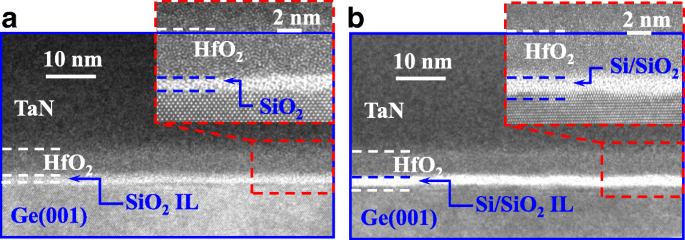

На рис. 2а, б показаны изображения, полученные с помощью просвечивающего электронного микроскопа (ПЭМ), стопки затвора с высоким значением κ / металл с SiO 2 . / Si интерфейсный слой (IL) на канале Ge (001) с t Si 0,5 и 0,9 нм соответственно. На вставках показаны изображения образцов, полученные методом просвечивающей электронной микроскопии (ПЭМВР) с высоким разрешением. Для устройства с t Si 0,5 нм слой аморфного Si был полностью окислен, а для устройства с 0,9 нм t Si , после последующих стадий отжига осталось около двух монослоев Si.

Поперечное сечение ПЭМ-изображений стеков затворов Ge pMOSFET с a 0,5 нм t Si и b 0,9 нм t Si . Изображения HRTEM на вставках показывают, что Si / SiO 2 ИЖ образуется между HfO 2 и канал Ge

Результаты и обсуждение

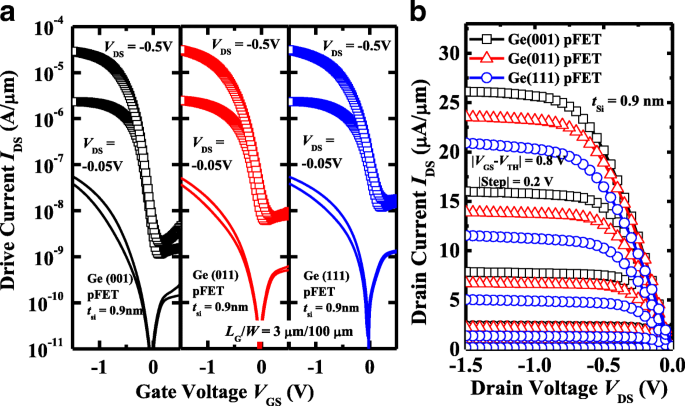

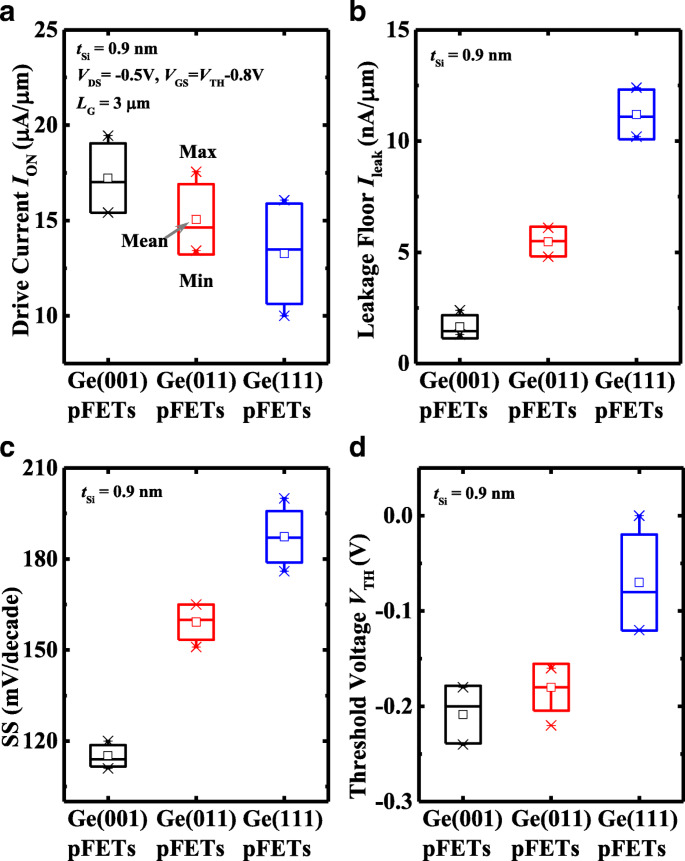

На рис. 3а показаны измеренные значения I DS - V GS и я G - V GS кривые типичных Ge pMOSFET на (001) -, (011) - и (111) -ориентированных поверхностях с 0,9 нм t Si , которые показывают отличные передаточные характеристики. Все транзисторы имеют длину затвора L G 3 мкм и шириной затвора W 100 мкм. Направление канала [110] для всех ориентаций. Я DS - V DS кривые устройств, измеренные при разной перегрузке ворот V GS - V TH показаны на рис. 3б. Здесь пороговое напряжение В TH определяется как V GS в I DS из 10 −7 А / мкм. Замечено, что Ge (001) pMOSFET обеспечивает более высокий ток возбуждения I ВКЛ по сравнению с транзисторами на поверхностях (011) и (111) при фиксированном V GS - V TH . Позже мы покажем, что это связано с тем, что полевые МОП-транзисторы Ge (001) имеют более высокую эффективную подвижность дырок μ eff по сравнению с устройствами на двух других ориентациях поверхности. Мы проводим комплексное сравнение электрических характеристик устройств с фиксированным значением t . Si 0,9 нм, включая I ВКЛ , перекрытие утечки I утечка , подпороговое колебание (SS) и V TH характеристики. Я утечка определяется как минимум I DS в V DS - 0,05 В. На рис. 4а представлен статистический график зависимости I ВКЛ для Ge pMOSFET различной ориентации и I ВКЛ был определен как I DS при V DS от - 0,5 В и В GS - V TH - 0,8 В. Все транзисторы на этом графике имеют напряжение L . G 3 мкм и W 100 мкм. (001) -ориентированные устройства демонстрируют улучшенное среднее значение I ВКЛ по сравнению с ориентациями (011) и (111), что объясняется более высокими значениями μ eff . На рисунке 4b сравнивается I утечка для устройств, показывая, что транзисторы Ge (001) имеют наименьшее значение I утечка из них, а полевые МОП-транзисторы Ge (011) имеют нижнее значение I утечка чем устройства с ориентацией (111). Следует отметить, что I утечка определяется обратным током p + / n-переход в области стока, на который влияет фоновая концентрация легирования n-типа в подложке Ge и активация имплантированного p + присадки. Концентрации легирования n-типа в пластинах разной ориентации не совсем одинаковы. Ориентация поверхности влияет на скорость активации легирующей примеси и качество рекристаллизации S / D областей. Кроме того, хотя I G ниже I DS до включения транзисторов это повлияло бы на I утечка . Аналогичным образом, (001) -ориентированные полевые МОП-транзисторы Ge демонстрируют улучшенные характеристики SS по сравнению с двумя другими ориентациями, что связано с тем, что транзисторы на поверхности (001) имеют более низкую плотность межзонного состояния интерфейса D это по сравнению с другими устройствами. На рис. 4d показано, что устройства в разной ориентации имеют разное V . TH . На основании результатов на рис. 4 делается вывод, что при фиксированном t Si Наилучшие электрические характеристики имеют полевые МОП-транзисторы Ge pMOSFET с ориентацией (001) 0,9 нм.

а Измерено I DS - V GS и я G - V GS кривые (001) -, (011) - и (111) -ориентированные Ge pMOSFET с 0,9 нм t Si показывая отличные передаточные характеристики. б Я DS - V DS кривые, измеренные при различных V GS - V TH для устройств

Сравнение а Я ВКЛ , b Я утечка , c SS и d V TH для (001) -, (011) - и (111) -ориентированных Ge pMOSFET с a t Si 0,9 нм

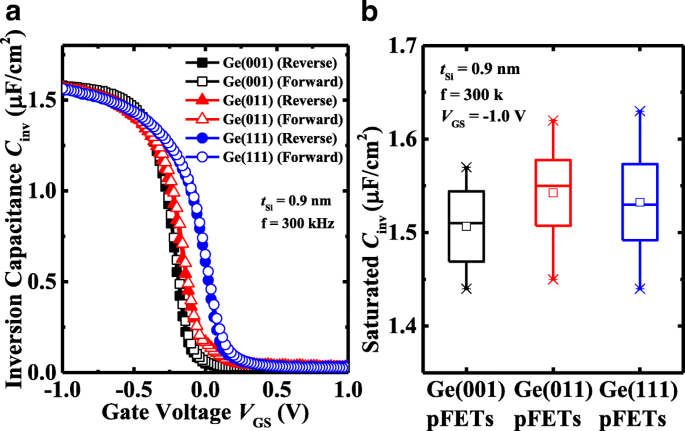

Толщина Si / SiO 2 ИЖ в транзисторах с 0,9 нм t Si на различных ориентациях поверхности изучаются с помощью инверсионной емкости C inv по сравнению с V GS измерения, как показано на рис. 5. Прямые и обратные измерения с разверткой показывают пренебрежимо малый гистерезис в устройствах. Транзисторы имеют одинаковую величину C inv , ~ 1,56 мкФ / см 2 , что соответствует эффективной емкостной толщине (CET) 2,2 нм. На рисунке 5b показаны статистические результаты насыщенного C inv для устройств, которые демонстрируют очень небольшую разницу в C inv в транзисторах с разной ориентацией поверхности. Это указывает на то, что скорость пассивации аморфного Si магнетронным распылением не зависит от ориентации поверхности. Правило сдвига влево-вправо C inv - V GS кривые хорошо согласуются с кривой V TH для устройств на рис. 4d, что может быть вызвано несколько различающейся концентрацией легирования в подложках с разной ориентацией.

а Сравнение инверсии C inv - V GS кривые среди Ge pMOSFET с 0,9 нм t Si на разные ориентации. Показаны как прямая, так и обратная развертка. б Статистические графики для насыщенного C inv устройств, показывающих незначительные различия в C inv в режиме инверсии

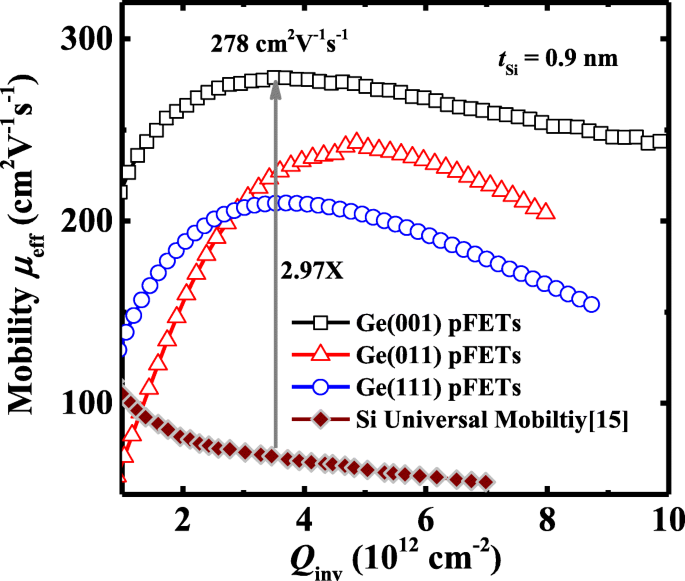

На рисунке 6 сравниваются характеристики подвижности транзисторов с 0,9 нм t Si на различной ориентации поверхности. μ eff был извлечен с использованием метода наклона полного сопротивления [14]. Полевые МОП-транзисторы на основе Ge (001) демонстрируют гораздо более высокую подвижность каналов по сравнению с устройствами с ориентацией (011) и (111). Транзисторы на подложке (001) достигают пика μ eff 278 см 2 / В · с при плотности заряда инверсии Q inv из ~ 3,5 × 10 12 см −2 , что в 2,97 раза выше универсальной подвижности Si. Шероховатость поверхности на границе Si / Ge и плотность интерфейсных состояний ( D это ) может повлиять на μ eff устройств с высокой плотностью инверсной несущей. Маловероятно, что коммерчески приобретаемые пластины Ge с различной ориентацией поверхности имеют очевидную разницу в шероховатости поверхности. Поэтому предполагается, что повышение подвижности в устройствах с ориентацией (001) в основном связано с уменьшенным рассеянием носителей, вносимым интерфейсными состояниями. В этой работе мы оцениваем средний промежуток D это устройств, и с фиксированным t Si 0,9 нм, (001) -ориентированные полевые МОП-транзисторы на основе Ge действительно имеют более низкий средний зазор D это по сравнению с другими ориентациями.

Участок μ eff против Q inv для Ge pMOSFET с 0,9 нм t Si на подложках с ориентацией (001) -, (011) - и (111). Полевые МОП-транзисторы Ge (001) достигают увеличения в 2,97 раза в μ eff на Q inv из 3,5 × 10 12 см −2 по сравнению с универсальной мобильностью Si. μ eff был извлечен с использованием метода наклона полного сопротивления [17]

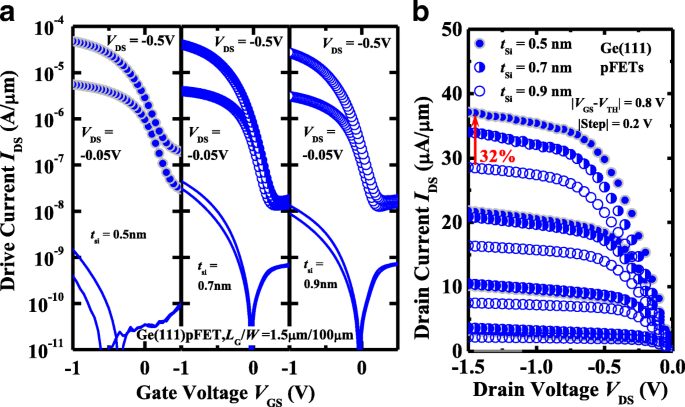

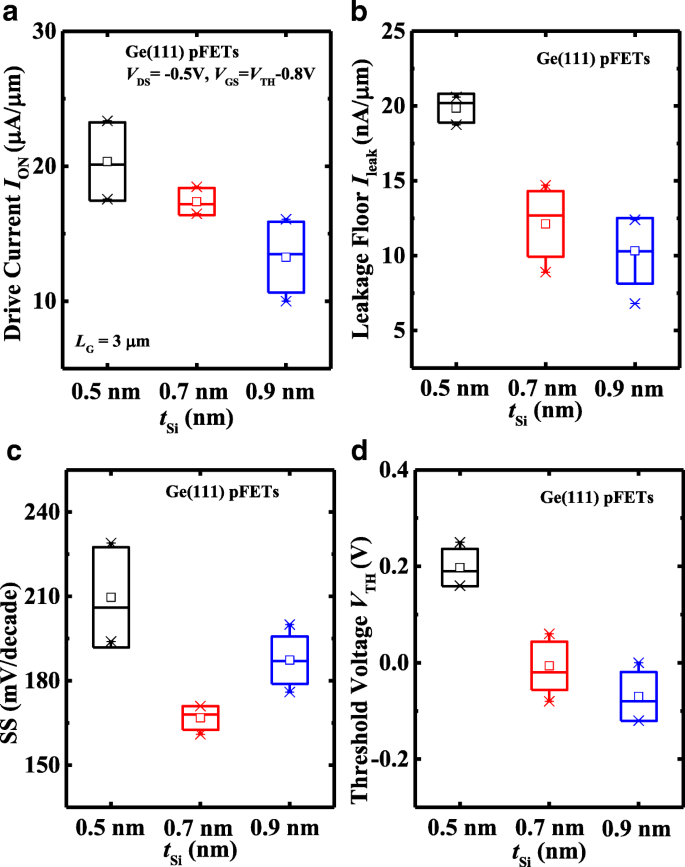

Влияние t Si электрические характеристики Ge pMOSFET также исследуются. На рис. 7а, б представлены измеренные значения I DS - V GS и я DS - V DS кривые соответственно (111) -ориентированных Ge pMOSFET с t Si 0,5, 0,7 и 0,9 нм при V DS от - 0,05 и - 0,5 В. Транзисторы имеют L G 1,5 мкм. Замечено, что полевые МОП-транзисторы Ge с длиной волны 0,9 нм t Si демонстрируют улучшенные характеристики передачи по сравнению с устройствами с более тонкими t Si , но я ВКЛ устройства уменьшается с увеличением t Si . В V DS от - 1,5 В и В GS - V TH из - 0,8 В, Ge (111) pMOSFET с 0,5 нм t Si демонстрирует улучшение на 32% в I ВКЛ по сравнению с устройством с 0,9 нм t Si . На рисунке 8 показаны статистические результаты I ВКЛ , Я утечка , SS и V TH полевых МОП-транзисторов Ge на (111) -ориентации с разными t Si . Из рис. 8а видно, что транзисторы с 0,5 нм t Si добиться улучшенного I ВКЛ по сравнению с аппаратами с более толстым t Si , что связано с транзистором с 0,5 нм t Si с меньшим CET, что приводит к более высокому C inv . Замечено, что Я утечка уменьшается с увеличением t Si (Рис. 8b), а транзисторы с 0,5 нм t Si имеет худшие характеристики ТС по сравнению с приборами с пассивирующим слоем аморфного кремния 0,7 и 0,9 нм (рис. 8в). Это может быть связано с транзисторами с 0,5 нм t Si имея более высокий средний промежуток D это . Связь между SS и midgap D это полевого МОП-транзистора Ge можно выразить как SS =ln (10) ⋅ ( kT / q) ⋅ [1 + ( C это + C d ) / C вол ], где C бык , C d , и C это - емкость оксида, емкость обедненного слоя и емкость от интерфейсных ловушек, соответственно. C это можно рассчитать по q × D это , были D это - плотность ловушек на границе раздела. Хотя транзистор с 0,5 нм t Si имеет больший C бык по сравнению с двумя другими устройствами его более высокий средний диапазон D это может привести к тому, что СС будет хуже устройств с более толстым t Si . Пассивирование поверхности также повлияет на I утечка от стока к истоку. С подметанием V GS из положения в отрицательное, канал переходит из режима накопления в режим инверсии. Однако если D это высокий, некоторые точки на поверхности канала закреплены интерфейсными ловушками, и могут образовываться пути утечки, увеличивая I утечка от стока к истоку. Как показано на рис. 8d, полевые МОП-транзисторы Ge (111) показывают сдвиг на V TH на отрицательное V GS направление с увеличением t Si , что связано с увеличением CET. Вдобавок плотность ловушек в нижней половине запрещенной зоны, кажется, увеличивается с более тонкими t Si , что может привести к смещению V TH [2].

а Я DS - V GS и я G - V GS и b Я DS - V DS кривые полевых МОП-транзисторов на основе Ge (111) с различными значениями t Si . Транзистор с 0,5 нм t Si показывает улучшение I на 32% ВКЛ по сравнению с устройством с 0,9 нм t Si в V DS от - 1,5 В и В GS - V TH из - 0,8 В

Сравнение а Я ВКЛ , b Я утечка , c SS и d V TH для (111) -ориентированных Ge pMOSFET с 0,5, 0,7 и 0,9 нм t Si показывает, что транзисторы с 0,5 нм t Si лучше я ВКЛ , но хуже СС и я утечка характеристики по сравнению с аппаратами с большей толщиной t Si

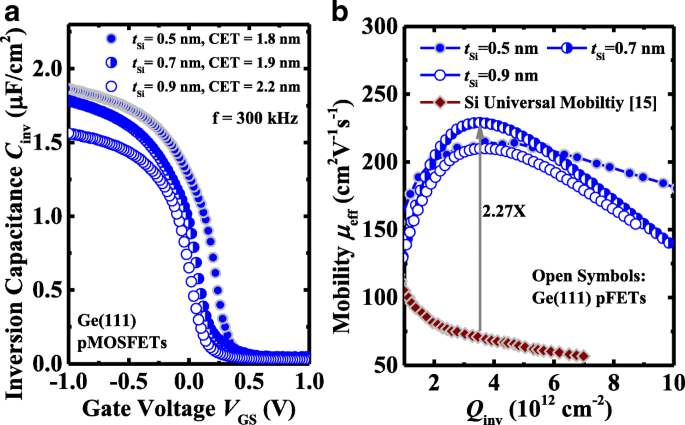

На рисунке 9a показан C inv как функция от V GS кривые для Ge pMOSFET на поверхности с ориентацией (111) с t Si 0,5, 0,7 и 0,9 нм, измеренные на частоте 300 кГц. Значения CET в областях инверсии получены равными 1,8, 1,9 и 2,2 нм для устройств с 0,5, 0,7 и 0,9 нм t si , соответственно. μ eff как функция от Q inv Характеристики устройств извлечены и показаны на рис. 9б. Ge pMOSFET с ориентацией (111) с длиной волны 0,7 нм t si достигает максимальной подвижности 229 см 2 / V s, что в 2,27 раза выше по сравнению с универсальной подвижностью Si. Следует отметить, что устройства с 0,5 нм t Si демонстрируют значительно улучшенный μ eff над транзисторами с большей толщиной t Si на высоком Q inv (например, 10 13 см −2 ). Это также приводит к более высокому I ВКЛ при высоком V GS - V TH в устройствах с 0,5 нм t Si по сравнению с приборами на 0,7 и 0,9 нм t Si . μ eff на высоком Q inv уменьшается как t Si увеличивается с 0,5 нм до 0,7 ~ 0,9 нм, что объясняется тем, что большая шероховатость поверхности приводит к более сильному рассеянию шероховатости поверхности носителей. Во время пассивации поверхности Ge с помощью магнетронного распыления при комнатной температуре диффузия поверхностных атомов сильно подавляется. Итак, с увеличением t Si , шероховатость поверхности больше, что можно наблюдать из изображений ПЭМВР на рис. 2.

а C inv - V G характеристики, измеренные на частоте 300 кГц для (111) -ориентированных устройств с 0,5, 0,7 и 0,9 нм t Si . б μ eff как функция от Q inv для Ge pMOSFET [17]

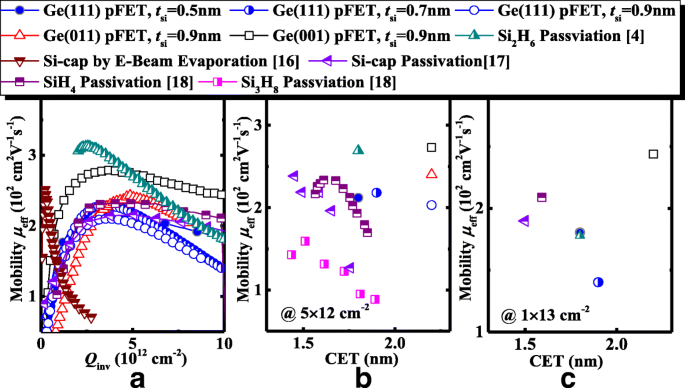

На рис. 10 мы тестируем μ eff Ge pMOSFET в этой работе с таковыми из описанных релаксированных Ge-транзисторов с Si путем испарения электронным пучком, SiH 4 , Si 2 H 6, и Si 3 H 8 пассивация. По сравнению с аморфным Si, полученным методом электронно-лучевого испарения в [5]. [15], Ge pMOSFET в этой работе демонстрируют значительно улучшенные μ eff . Видно, что при аналогичном CET полевые МОП-транзисторы Ge, использующие пассивацию аморфного кремния магнетронным распылением, имеют меньшее значение μ eff по сравнению с устройствами с Si 2 H 6 пассивация. Процесс пассивации с использованием аморфного Si требует дальнейшей оптимизации для увеличения подвижности носителей.

а μ eff для Ge pMOSFET в этой работе по сравнению с опубликованными результатами для релаксированных Ge pMOSFET. б , c Бенчмаркинг μ eff извлечено в Q inv =5 × 10 12 и 1 × 10 13 см −2 , соответственно, полевых МОП-транзисторов Ge с разными значениями CET [18, 19]

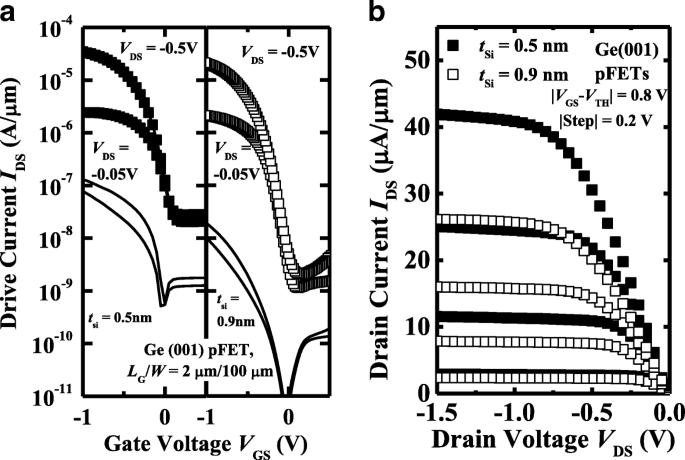

Ge pMOSFET с разными t Si на (001) -ориентированной поверхности. На рис. 11а, б показаны измеренные значения I DS - V GS и я DS - V DS кривые, соответственно, пары полевых МОП-транзисторов Ge (001) с 0,5 и 0,9 нм t Si . Подобно устройствам с ориентацией (111), Ge (001) pMOSFET с 0,5 нм t Si получает улучшение в I ВКЛ но деградация в I утечка по сравнению с транзистором на 0,9 нм t Si .

а Измерено I DS - V GS и я G - V GS кривые (001) -ориентированных Ge pMOSFET с 0,5 и 0,9 нм t Si . б Я DS - V GS кривые устройств

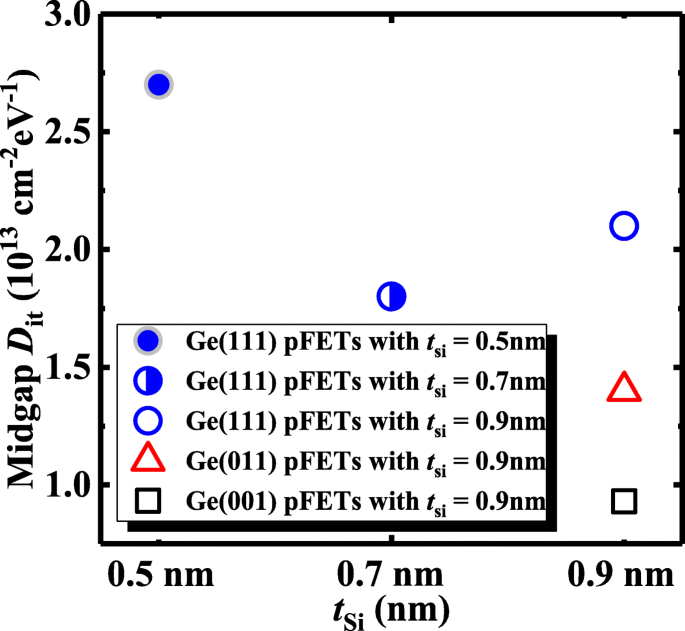

Средний промежуток D это характеристики Ge pMOSFET исследуются методом [16], а значения D это рассчитываются по D это =[SSlog (e) / ( kT / q ) - 1] C G / q , [16] где q - заряд электрона, k постоянная Больцмана, T - абсолютная температура, а C G - измеренная емкость затвора на единицу площади. На рисунке 12 показан D . это как функция толщины аморфного Si с различной ориентацией поверхности Ge. Для (111) -ориентированной поверхности прибор с 0,7 нм t si имеет самый низкий D это ценность. При длине волны 0,9 нм t Si , (001) -ориентированное устройство имеет нижнюю D это по сравнению с транзисторами других ориентаций.

Д это в зависимости от толщины аморфного Si с различной ориентацией поверхности Ge

Наконец, мы сравниваем ключевые электрические характеристики Ge pMOSFET для различных ориентаций в таблице 1. С фиксированным t Si , Ge (001) pMOSFET имеет улучшенные электрические характеристики по сравнению с двумя другими ориентациями. Ток привода можно увеличить, уменьшив t Si от 0,9 нм до 0,5 нм, что связано с тем, что тоньше t Si обеспечивает значительное снижение CET, не вызывая ухудшения в μ eff .

Выводы

Ge pMOSFET, пассивированный аморфным Si, продемонстрирован на подложке с ориентацией (001) -, (011) - и (111). С t Si 0,9 нм, улучшенный I ВКЛ и характеристики SS получены в Ge pMOSFET с ориентацией (001) по сравнению с устройствами с ориентацией (011) и (111) из-за более высоких значений μ eff и нижняя середина промежутка D это . Ge (001) pMOSFET с 0,9 нм t Si достичь максимальной подвижности 278 см 2 / V с при Q inv из 3,5 × 10 12 см −2 , что в 2,97 раза выше универсальной подвижности Si. Показано, что Я ВКЛ устройств улучшается с уменьшением t Si за счет снижения среднеевропейского времени. Но Ge pMOSFET с более толстым t Si демонстрируют превосходные подпороговые колебания и пол утечки благодаря этому среднему зазору D это можно уменьшить, увеличив t Si .

Сокращения

- ALD:

-

Осаждение атомного слоя

- BF 2 + :

-

Ион фторида бора

- CET:

-

Емкостная эффективная толщина

- Ge:

-

Германий

- GeO x :

-

Оксид германия

- HF:

-

Плавиковая кислота

- HfO 2 :

-

Диоксид гафния

- HRTEM:

-

Просвечивающий электронный микроскоп высокого разрешения

- IL:

-

Межфазный слой

- МОП-транзисторы:

-

Полевые транзисторы металл-оксид-полупроводник

- Ни:

-

Никель

- Si:

-

Кремний

- SS:

-

Подпороговое колебание

- TaN:

-

Нитрид тантала

- TDMAHf:

-

Тетракис (диметиламидо) гафний

Наноматериалы

- KUHMUTE изменяет мобильность с помощью 3D-печати SLS

- Высокоскоростная 3D-печать с AFPM

- Высокоскоростная 3D-печать с AION500MK3

- Высокая производительность PEDOT:солнечные элементы на основе PSS / n-Si на текстурированной поверхности с электро…

- Преобразователь поляризации с управляемым двулучепреломлением на основе гибридной метаповерхности полност…

- Высокоэффективный гибридный кремниевый элемент с органической наноструктурой и измененной структурой пове…

- Безрезисторный источник опорного напряжения в наномасштабе с низким энергопотреблением и высоким PSRR

- Пористые нанолисты ZnO с частичной модификацией поверхности для улучшенного разделения зарядов и высокой фот…

- Ge pMOSFET с пассивацией GeOx, образованной озоном и пост-окислением плазмы

- Новые сведения о факторах, ограничивающих перенос носителей в очень тонких аморфных пленках In2O3 с примесью Sn …