Расширение архитектуры RISC-V с помощью ускорителей, специфичных для предметной области

Когда рынок RISC-V только зародился, первоначальная спешка заключалась в сокращении затрат на проекты, которые в противном случае использовали бы проприетарные архитектуры набора команд (ISA) в глубоко встроенных приложениях. Когда эти системы на микросхемах (SoC) начали изготавливаться с использованием полупроводниковой технологии FinFET, стоимость масок выросла настолько, что многие конечные автоматы были заменены программируемыми микропоследовательностями, основанными на наборе команд RISC-V. Это вызвало поначалу ажиотаж, а затем и коммерциализацию простых ядер RISC-V с 2014 по 2018 год.

По мере того, как архитектура RISC-V становилась более зрелой и разработчики SoC познакомились с ISA, она нашла применение в приложениях реального времени, требующих высокой производительности:в частности, в качестве внешнего интерфейса для узкоспециализированных механизмов ускорения для таких приложений, как искусственный интеллект. . Одна из основных причин такого принятия заключается в том, что RISC-V - это открытая архитектура для пользователей, позволяющая добавлять инструкции, поэтому процессорам RISC-V не приходилось рассматривать ускорители как устройства ввода-вывода с отображением памяти, как это было в случае с традиционными архитектурами. . Вместо этого они могут использовать сопроцессор с малой задержкой.

Наличие процессоров RISC-V с векторным расширением позволило специализированным ускорителям обрабатывать слои между внутренними циклами ядра для таких приложений, как искусственный интеллект (AI), дополненная реальность / виртуальная реальность (AR / VR) и компьютерное зрение. Но это невозможно без специальных расширений, таких как пользовательская инструкция загрузки для переноса данных из внешнего ускорителя во внутренние векторные регистры.

Движущей силой этого сдвига является модель программирования, требуемая этими приложениями. Ускоритель специального назначения, представляющий собой один большой набор умножителей, очень эффективен, хотя и довольно негибкий, как при выполнении операций, так и при перемещении данных. Сравните это с процессором общего назначения, таким как x86, который дает программисту максимальную гибкость при программировании без учета ограничений вычислительного механизма - если только конструкция имеет 100 Вт мощности для сжигания, чего в большинстве своем нет.>

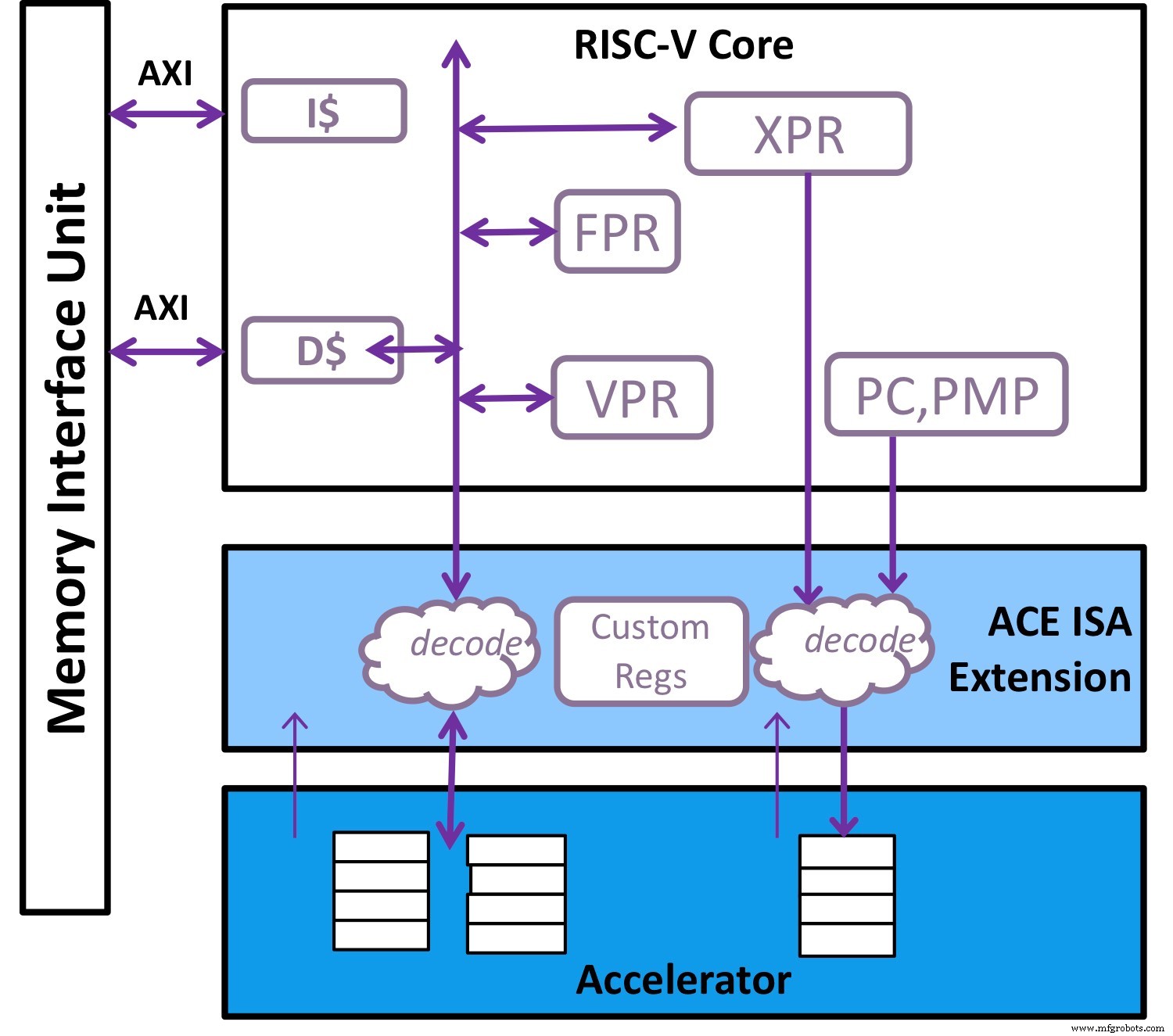

Стандартное расширение вектора в RISC-V, дополненное специальными пользовательскими инструкциями, является идеальным дополнением к ускорителю (Изображение:Andes Technology)

Очевидное решение - объединить гибкость универсального ЦП с ускорителем, который может справиться с очень конкретной задачей (см. Рисунок выше). В RISC-V развивающееся стандартное векторное расширение, дополненное специализированными настраиваемыми инструкциями, является идеальным дополнением к ускорителю, и это принятие стало очевидным в последние 18 месяцев, когда решения для доменно-ориентированного ускорения (DSA) сходятся на платформах RISC-V.

Чтобы сделать это видение возможным, мы заметили, что ускоритель должен иметь возможность выполнять свой собственный набор команд, используя свои собственные ресурсы, включая память. Чтобы упростить выполнение ускорителя, RISC-V также должен иметь возможность выравнивать микрокод до необходимой ширины и упаковывать всю необходимую управляющую информацию в ускоритель за одну команду. Кроме того, этот набор команд ускорителя должен учитывать скалярные регистры и векторные регистры процессора RISC-V, а также свои собственные ресурсы, такие как файлы регистров управления и память.

Когда ускорителю требуется помощь в переупорядочивании или обработке данных особым образом, архитектура Анд решает эту проблему с помощью блока векторной обработки (VPU), который выполняет сложную работу по перестановке данных - смещению, сбору, сжатию и расширению. Между слоями есть несколько ядер, которые вызывают сложности. Здесь VPU обеспечивает гибкость, помогающую удовлетворить эту потребность. В этих сокетах и ускоритель, и видеопроцессор выполняют огромное количество параллельных вычислений; поэтому мы добавили оборудование, чтобы значительно увеличить пропускную способность подсистемы памяти в соответствии с требованиями вычислений, включая, помимо прочего, предварительную выборку и неблокирующие транзакции с возвратом вне порядка.

Первый векторный процессор RISC-V от Andes Technology, поддерживающий последнюю версию V-extension 0.8, NX27V, выполняет каждое вычисление в единицах 8-битных, 16-битных и 32-битных целых чисел до 16-битных и 32-битных чисел с плавающей запятой. Он также поддерживает форматы Bfloat16 и Int4, чтобы уменьшить пропускную способность хранилища и передачи для весовых значений алгоритмов машинного обучения. Спецификация вектора RISC-V очень гибкая, позволяя разработчикам настраивать ключевые параметры проектирования, такие как длина вектора, количество битов в каждом векторном регистре и ширина SIMD, количество бит, обрабатываемых векторным механизмом в каждом цикле.

NX27V имеет длину вектора до 512 бит и расширяется до 4096 бит за счет объединения до восьми векторных регистров. С добавлением нескольких функциональных блоков, работающих в параллельных конвейерах, он может поддерживать производительность вычислений, необходимую в разнообразных приложениях. В реализации, сконфигурированной с длиной вектора 512 бит и той же шириной SIMD, он достигает скорости 1 ГГц при 7 нм в худшем случае в пределах области 0,3 мм 2 . Для поддержки разработки программного обеспечения, помимо компилятора, отладчика, векторных библиотек и симулятора циклов, инструмент визуализации для конвейера NX27V, Clarity, помогает анализировать и оптимизировать производительность критических циклов. Это решение уже включено в нашу программу раннего доступа.

За последние 15 месяцев мы увидели большой спрос на высокую производительность с добавлением мощного векторного расширения RISC-V, сопоставлением его с подсистемой памяти с высокой пропускной способностью и приближением ускорителя к процессору. Мы считаем, что именно такие вычислительные требования будут стимулировать спрос на RISC-V и векторную обработку.

>> Эта статья была первоначально опубликована на наш дочерний сайт EE Times.

Встроенный

- Представляем IIC теперь с OpenFog!

- 2-я версия эталонной архитектуры промышленного Интернета вышла с многоуровневой шиной данных

- Борьба с лесными пожарами с помощью Интернета вещей

- Достижение недоступности с помощью спутникового Интернета вещей

- Руководство по ускорению приложений с помощью правильных пользовательских инструкций RISC-V

- Печать предохранителя 1 с предохранителем 1

- Что мне делать с данными ?!

- Периферийные вычисления:архитектура будущего

- Защита вектора угроз Интернета вещей

- В пути с IoT