Руководство по ускорению приложений с помощью правильных пользовательских инструкций RISC-V

Открытая архитектура набора команд (ISA) RISC-V обеспечивает широкую гибкость в реализации и предлагает дополнительные функции, которые могут позволить новые подходы к разрешению компромиссов при проектировании аппаратного и программного обеспечения. Основываясь на модульной структуре, можно использовать ряд стандартных расширений и опций для настройки базового процессора в качестве отправной точки. Однако настоящая ценность на самом деле заключается в возможностях, которые RISC-V предлагает разработчикам для создания новых расширений, инструкций и конфигураций, которые однозначно отвечают потребностям их инновационных идей приложений.

Проблема программного обеспечения для фиксированных ISA

Традиционно ISA были интеллектуальной собственностью (IP) коммерческих организаций, которые либо хотели продавать микропроцессоры или микроконтроллеры, либо лицензировать свои разработки для использования другими. Разработчикам встраиваемых систем остается выполнить программное обеспечение для тестирования производительности, чтобы определить, какое решение лучше всего оптимизировано для их приложений. Из-за затрат на разработку независимого ISA со всей необходимой экосистемой поставщики полупроводников все больше полагались на стандартные фиксированные ISA, предлагаемые основными поставщиками IP, полагаясь на закон Мура и интегрированные периферийные устройства для обеспечения дифференциации, например, сверхнизкого энергопотребления. своим клиентам.

Проблема здесь в том, что инструкции, используемые для выполнения кода, не могут быть изменены. Следовательно, эффективность, которая потенциально может быть достигнута, например, с помощью оптимизированной инструкции для алгоритма шифрования, не может быть реализована. Это может означать, что приложение разработчика слишком медленное, потенциально потребляет слишком много энергии или регулярно пропускает крайний срок в реальном времени в контуре управления. Даже при самой доброй воле в мире эти факторы сложно решить только за счет улучшения производства полупроводников или сокращения технологических процессов.

RISC-V ISA начиналась как проект в Калифорнийском университете в Беркли и в настоящее время поддерживается Международной ассоциацией RISC-V, некоммерческой группой, насчитывающей более 300 членов. Они вносят вклад в спецификации ISA, программные инструменты, такие как симуляторы и компиляторы, и остальную часть экосистемы, которая необходима для поддержки такого начинания. Целесообразность использования зависит от того, можно ли использовать один из двух факторов:бесплатное с точки зрения лицензии или предоставляемая свобода.

Будучи открытым и свободно доступным, он обеспечивает базовую платформу обработки, которую могут легко использовать как академические круги для обучения и исследований, так и коммерческие приложения. Открытый ISA также поддерживает ряд бизнес-моделей для разработчиков, которые ищут исходные полупроводниковые IP-адреса, от коммерческого поставщика IP до проектов с открытым исходным кодом и собственных разработок с чистого листа. Коммерческие организации также находят это привлекательным, используя его в ПЛИС, SoC или даже в ядре микроконтроллеров или стандартных продуктов.

Благодаря предоставляемой им свободе академические круги могут исследовать новые подходы к решению вычислительных задач, внедряя что угодно:от новых инструкций и других ускорителей до многоядерных и многоядерных гетерогенных конструкций, а также различных вариантов микроархитектуры. Многие из этих вариантов также привлекательны для стартапов и предприятий, которые хотят решать сложные задачи, например, маломощные наборы микросхем искусственного интеллекта (ИИ), которые работают на периферии, путем добавления пользовательских инструкций, адаптированных к требованиям конечного приложения.

Поскольку экосистема была создана со встроенной гибкостью RISC-V, любая стандартная конфигурация или настраиваемое расширение должно иметь возможность использовать инструменты и программное обеспечение в рамках совместимой с ISA структуры.

Понимание гибкости открытого RISC-V ISA

Благодаря доступности RISC-V ISA и связанных инструментов, легко начать исследовательский проект, чтобы оценить его пригодность для использования в конкретном приложении. Инструменты моделирования позволяют опробовать стандартную базовую ISA для определения готовой работы. Например, хорошей отправной точкой может быть 32-разрядная конфигурация RISC-V с расширениями целого числа «I» и умножением «M» (на которые можно ссылаться как RV32IM), обеспечивающая поддержку базового 32-разрядного целочисленного набора команд; доступны другие варианты, но этого достаточно для данного примера. Затем он создается вместе с моделируемой памятью, включая задержки доступа и состояния ожидания.

Затем приложение, написанное на C / C ++, может быть скомпилировано с использованием стандартных цепочек инструментов. Это может быть запущено на «голом железе» или как часть операционной системы (реального времени) (RTOS / OS). Полученный двоичный код затем выполняется с использованием таких инструментов, как имитатор набора команд (ISS), который позволяет интегрировать и моделировать выбранную базовую модель процессора (рисунок 1). Эта среда также обеспечивает стандартные функции ввода / вывода и доступ к файловой системе хоста. Стандартные инструменты интегрированной среды разработки (IDE), такие как Eclipse, затем можно использовать для управления выполнением кода, взаимодействуя через отладчик GNU GDB.

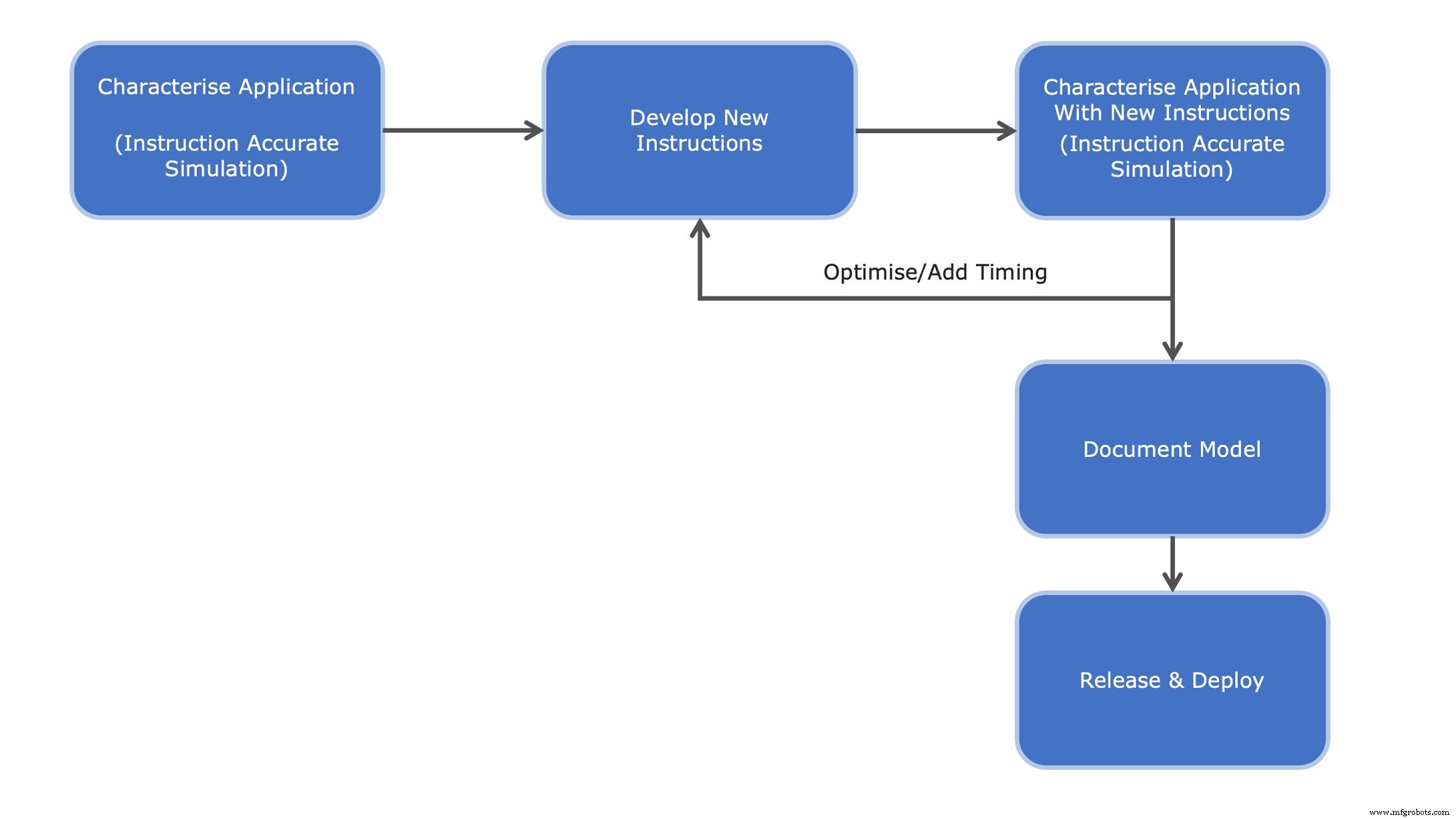

Отсюда, в процессе профилирования и анализа, кандидаты в инструкции идентифицируются, разрабатываются и моделируются. Используя исходный код приложения в качестве базовой функциональной модели, полученное улучшение можно быстро протестировать, проверить и сравнить производительность. Эта быстрая итерация профилирования и анализа позволяет быстро выбирать и оптимизировать инструкции, которые стоит реализовать. Документация может быть создана на основе модели и составляет основу функциональной спецификации для разработки логики передачи регистров (RTL) и оптимизированной модели.

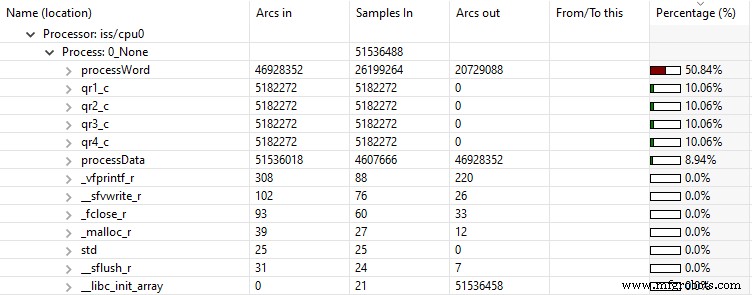

Например, алгоритм шифрования, такой как ChaCha20, может иметь решающее значение для конкретного приложения. Доступный исходный код может быть скомпилирован для «ванильной» базы RV32IM, выполнен, а затем проанализирован с расчетным временем цикла команд с использованием базового профилирования блоков, чтобы определить, сколько времени было потрачено на какие разделы кода. Ядро алгоритма ChaCha20 интенсивно использует инструкции XOR и вращения, известные как четвертьраунды (рисунок 2). Результаты блочного профилирования сразу показывают, что большая часть времени выполнения тратится на эти функции.

Графическую визуализацию этих горячих точек можно также создать с помощью инструмента проверки, анализа и профилирования (VAP). Вместо текстового вывода время выполнения предоставляется в виде дерева сворачиваемой статистики, помогая лучше визуализировать горячие точки с высокой долей выполненных инструкций. Это можно увидеть на рисунке 3, где функция processWord () реализует алгоритм ChaCha20, вызывая по очереди четыре qrx_c функции для реализации требуемых функций четверть раунда.

Просматривая ассемблерный код, сгенерированный компилятором, и / или запустив базовое профилирование блоков, можно затем определить, какие инструкции и комбинации инструкций использовались для реализации алгоритма. Отсюда следующий шаг - определить, какие пользовательские инструкции в рамках спецификаций ISA потенциально могут увеличить скорость выполнения.

Определение потенциальных улучшений, которые может дать RISC-V

Алгоритм ChaCha20 интенсивно использует XOR в сочетании с поворотом влево на 7, 8, 12 и 16 бит. Использование доступных инструкций базовой спецификации RV32IM показывает, что для этого требуется инструкция XOR, за которой следует инструкция сдвига влево. Это означает, что есть потенциал для оптимизации этих двух шагов в четыре специальные инструкции, которые реализуют XOR вместе с 7, 8, 12 или 16 битами левого вращения.

Будучи архитектурой загрузки-хранилища, любые пользовательские инструкции должны предполагать, что данные, которыми нужно манипулировать, уже находятся в одном из 32-битных регистров этого RISC-V. Это сразу определяет, что потребуется инструкция R-типа (регистр), которая может быть расположена в custom-1 расшифровать пробел (рисунок 4).

ISA предоставляет четкую структуру для таких инструкций. Следуя этим правилам, мы можем быстро определить, как кодировать наши новые инструкции. Младшие 7 битов определены как код операции которому присваивается значение, которое отмечает его как настраиваемую инструкцию в custom-1 декодировать пространство. Это в отличие от OP или OP-IMM коды операций, которые используются для существующих инструкций XOR и сдвига влево соответственно.

ISA предоставляет четкую структуру для таких инструкций. Следуя этим правилам, мы можем быстро определить, как кодировать наши новые инструкции. Младшие 7 битов определены как код операции которому присваивается значение, которое отмечает его как настраиваемую инструкцию в custom-1 декодировать пространство. Это в отличие от OP или OP-IMM коды операций, которые используются для существующих инструкций XOR и сдвига влево соответственно.

В определении ISA зарезервированы три предопределенных блока битов для задания двух исходных регистров и целевого регистра для результата. Остается блок битов, известный как funct3 . Эти три бита предоставляют нам место для кодирования восьми возможных инструкций, четыре из которых будут использоваться в этом примере.

Не требуя подробной аппаратной реализации RTL для этих инструкций, их можно смоделировать в среде ISS, чтобы увидеть, принесут ли они какую-либо пользу для решения стоящей перед ними задачи. Четыре новые инструкции смоделированы с использованием интерфейса прикладного программирования (API) VMI открытых виртуальных платформ (OVP). Это позволяет разработчику быстро итерировать дизайн инструкций, обеспечивающих оптимальный желаемый результат, на основе новых инструкций для целевого приложения. Только после того, как это будет достигнуто, необходимо выделить ресурсы на реализацию RTL.

Для первоначальной функциональной оценки инструкций есть два возможных подхода. Первый - вызвать исходную версию алгоритма C / C ++, привязав новые инструкции к этой функции (рисунок 5a). Второй - реализовать их как инструкции морфинга VMI, которые создают такое же поведение (рисунок 5b). Это более эффективный подход, и это рекомендуемый подход.

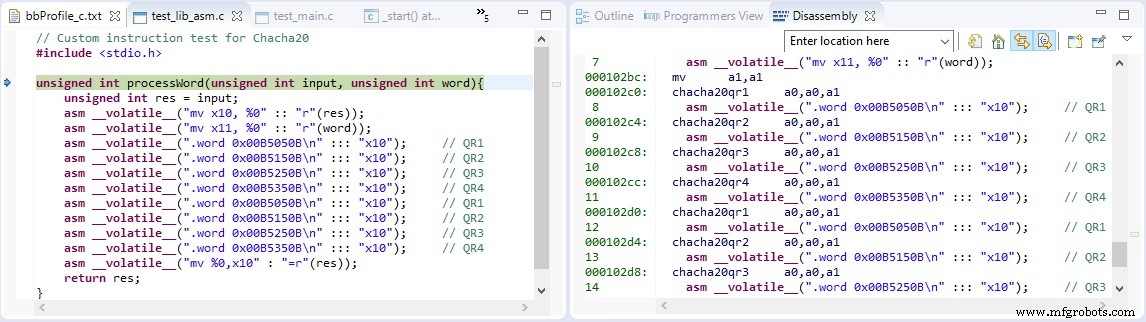

Конечно, простое существование новых инструкций не означает, что компилятор может немедленно их использовать. Следовательно, исходное приложение C / C ++ необходимо переписать с использованием встроенного ассемблера и скомпилировать кросс-компиляцию, чтобы использовать новые инструкции. Поскольку профилирование и анализ инструкций-кандидатов могут быть итеративной задачей, подход, основанный на встроенных функциях, обеспечивает наиболее эффективный способ адаптации исходного приложения C для использования новых пользовательских инструкций.

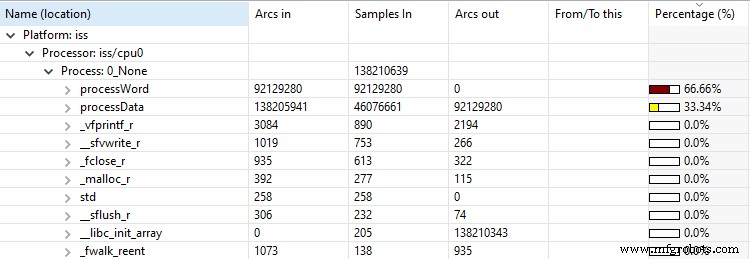

Базовая реализация RISC-V, загруженная в симулятор, также должна быть осведомлена о новых инструкциях, чтобы извлечь из них пользу. Это достигается включением их в модель перед повторным запуском моделирования. В этом конкретном примере повторение профилирования указывает на меньшее общее время, затрачиваемое на выполнение алгоритма (рисунок 6). Инструмент профилирования VAP Imperas показывает, что processWord () функция, использующая специальные встроенные инструкции, теперь составляет 66% от общего выполнения алгоритма, но общее время выполнения алгоритма значительно сокращается (рисунок 6b).

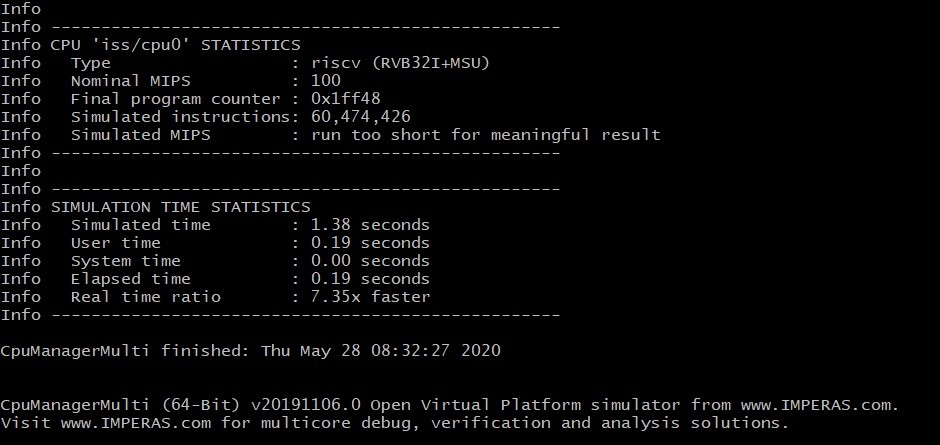

Результаты с исходной реализацией C

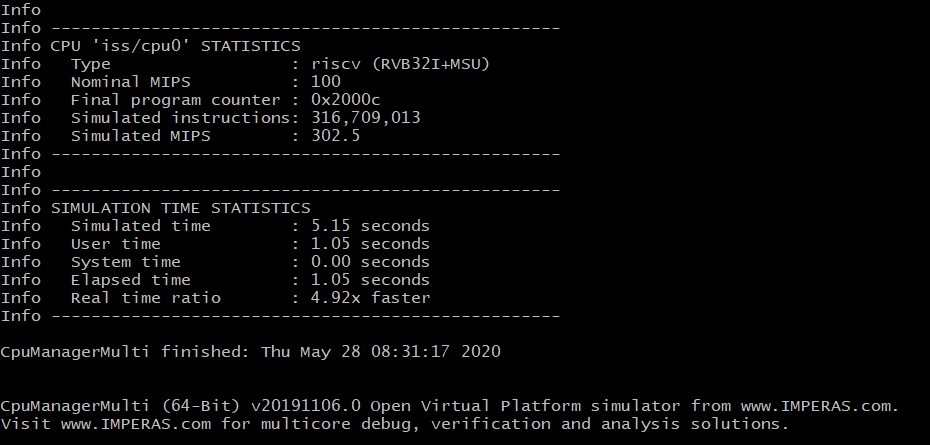

Информация Смоделированные инструкции:316 709 013

Информация Время моделирования:5,15 секунды

Результаты с пользовательскими инструкциями

Информация Смоделированные инструкции:60 474 426

Информация Время моделирования:1,38 секунды

После определения правильной функциональности модель дополнительно уточняется, объявляя время выполнения для каждой инструкции в циклах процессора. Затем можно использовать дополнительные раунды моделирования для определения любого улучшения производительности, даже с учетом состояний ожидания, связанных с доступом к памяти, которые могут произойти в возможной аппаратной реализации.

Благодаря тесной интеграции с общими IDE с открытым исходным кодом и инструментами GDB, полная отладка решения может быть проведена в сочетании с оптимизированным дизайном RISC-V до передачи проекта аппаратной реализации (рисунок 7).

Переход от моделирования к реализации

После определения потенциального улучшения производительности следующий шаг требует реализации четырех новых инструкций в RTL. Благодаря проделанной предварительной работе, это становится функциональной спецификацией, которая определяет требования, а также может использоваться как часть плана проверочного тестирования RTL в качестве золотой эталонной модели. Хотя использование встроенных функций в приложении C помогло профилированию и анализу пользовательских инструкций, этот подход также может быть использован для будущей разработки производственного кода или может быть рассмотрен для потенциальных улучшений цепочки инструментов компилятора.

Другая важная задача - документация - тоже несложный процесс. Все модели быстрых процессоров на открытых виртуальных платформах (OVP) включают документацию, которая может быть расширена, чтобы охватить функциональность изменений и модификаций. Следуя данному шаблону, можно объявлять и описывать новые инструкции, позволяя сообществу разработчиков обнаруживать их возможности и использовать их. Затем документация преобразуется в файл TeX, из которого может быть создан PDF-файл (рисунок 8).

Резюме

Благодаря свободе открытого ISA RISC-V, в дополнение к стандартным опциям и функциям, определенным в спецификации, пользователи могут разрабатывать дополнительные пользовательские расширения и инструкции. В самом простом виде он позволяет создавать новые и креативные бизнес-модели, включая коммерческие реализации и реализации с открытым исходным кодом, а также дает более широкую свободу в изучении дополнительных функций, выходящих за рамки традиционных традиционных подходов.

Однако истинная ценность заключается в том, чтобы взять полноценное, задокументированное и поддерживаемое базовое ядро и модифицировать его для удовлетворения конкретных потребностей приложения. Путем тщательного анализа приложений, профилирования кода и моделирования могут быть достигнуты значительные улучшения производительности, которые не могли быть реализованы с помощью фиксированных ISA. Все это можно разработать и профилировать с реальными рабочими нагрузками приложений до того, как приступить к детальной реализации оборудования.

Встроенный

- Профилирование распределенных приложений с помощью Perf

- Краткое руководство по 3D-печати с использованием струйной печати под переплет

- Microchip:масштабирование космических приложений с помощью COTS-устойчивых к радиации микроконтроллеров с ядром

- Renesas:микроконтроллеры RX72M с поддержкой EtherCAT для промышленных приложений

- Axiomtek:встроенная система со встроенным управляемым переключателем PoE уровня 2

- Изменение затрат с существующими поставщиками:руководство

- Фрезерно-фрезерный станок с ЧПУ по дереву - с потрясающими приложениями

- Начало работы с ИИ в страховании:вводное руководство

- 5 реальных приложений ИИ в медицине (с примерами)

- Руководство по нестандартным тормозным колодкам и колодкам для высокоскоростных железных дорог