Оптимизация программирования безконденсаторной 1T DRAM на основе TFET с двумя затворами

Аннотация

Большой объем конденсатора и более высокий ток утечки транзистора стали неотъемлемыми недостатками традиционной динамической памяти с произвольным доступом (DRAM) с одним транзистором (1T) и одним конденсатором (1C). В последнее время в ячейке DRAM применяется туннельный полевой транзистор (TFET) из-за низкого тока в закрытом состоянии и высокой степени переключения. Ячейка DRAM TFET (DG-TFET) с двойным затвором и безконденсаторной структурой имеет превосходные характеристики - более высокое время удерживания (RT) и слабую температурную зависимость. Но производительность ячейки TFET DRAM чувствительна к условиям программирования. В этой статье руководство по оптимизации программирования подробно обсуждается с использованием инструмента моделирования - Silvaco Atlas. Операции записи и чтения DG-TFET DRAM зависят от межполосного туннелирования (BTBT). Во время операции записи дыры, поступающие от BTBT, управляемые Gate2, сохраняются в потенциальной яме под Gate2. На затвор 2 подается небольшое отрицательное напряжение, чтобы удерживать дырки в течение длительного времени во время удержания «1». BTBT, управляемый Gate1, в основном влияет на ток чтения. Используя условия оптимизированного программирования, DG-TFET DRAM получает более высокий коэффициент тока чтения «1» к показанию «0» (10 7 ) и RT более 2 с. Более высокое RT снижает частоту обновления и динамическое энергопотребление DRAM.

Фон

Динамическая память с произвольным доступом (DRAM) стала неотъемлемой ячейкой памяти в мобильной и вычислительной системе [1,2,3]. Из-за уменьшения геометрических размеров устройства большой объем конденсатора является неотъемлемым недостатком традиционной ячейки DRAM с одним транзистором (1T) и одним конденсатором (1C), что ограничивает ее крупномасштабное применение. Бесконденсаторная ячейка DRAM 1T на основе транзистора с плавающим затвором продемонстрировала потенциальное преимущество по сравнению с традиционной DRAM 1T-1C для упаковки памяти с высокой плотностью [4]. В транзисторе с плавающим затвором заряды в области подложки сохраняются в области с плавающим затвором посредством туннелирования Фаулера-Нордхейма. И операция чтения зависит от термоэлектронной эмиссии [5, 6], которая такая же, как у полевого транзистора металл-оксид-полупроводник (MOSFET). В результате ток чтения DRAM с транзистором с плавающим затвором сильно зависит от температуры. Кроме того, термоэлектронная эмиссия вызывает подпороговое колебание (SS) транзистора выше 60 мВ / дек, что делает большой ток утечки и потребляемую мощность серьезными проблемами [7,8,9].

В последнее время туннельный полевой транзистор (TFET) рассматривается как многообещающий кандидат для будущих маломощных электрических устройств [10,11,12]. Основным механизмом проводимости TFET является межзонное туннелирование (BTBT) вместо термоэлектронной эмиссии, что дает ему несколько преимуществ, таких как SS менее 60 мВ / дек, низкий ток утечки в закрытом состоянии и слабая температурная зависимость. [13, 14]. До сих пор большое количество исследовательских работ по TFET в основном сосредоточено на изучении производительности устройства с одним TFET, а некоторые простые схемы состоят из TFET. Однако высокий я на / Я выкл TFET позволяет ему служить ячейке DRAM [15]. В частности, низкий ток утечки в закрытом состоянии может снизить ток считывания «0» и потребляемую мощность ячейки DRAM. Исследователи разработали DRAM с двойным затвором TFET (DG-TFET) с безконденсаторной структурой [16]. В DG-TFET DRAM накопление заряда во время операции записи основано на BTBT между каналом и стоком, которое в основном создается Gate2. В то же время туннелирование электронов способствует накоплению дырок в области канала под Gate2. Gate1 в основном отвечает за операцию чтения. Ток чтения DGTFET DRAM в основном зависит от BTBT между исходной областью и областью канала. Некоторые исследовательские группы продемонстрировали, что ток чтения DG-TFET DRAM имеет слабую зависимость от температуры. И DG-TFET DRAM может получить время удерживания выше целевого (64 мс) [17]. Но текущее отношение чтения «1» к чтению «0» и RT не является оптимальным значением из-за неоптимизированного условия программирования.

Производительность TFET DRAM, особенно текущее отношение чтения «1» к чтению «0», сильно зависит от условий программирования. Gate2 в основном влияет на BTBT во время операции записи, которая доминирует в области хранения зарядов и потенциальной яме под Gate2. Gate1 управляет BTBT во время операции чтения, что в основном влияет на ток считывания «1». Правильные смещения как Gate1, так и Gate2 могут заставить DGTFET DRAM получить более высокий коэффициент тока. Существует немного литературы, изучающей влияние условий программирования на ток чтения. В этой статье предлагается подробное руководство по оптимизации программирования, включая операции записи, удержания и чтения. Применяя условия оптимизированного программирования, DG-TFET DRAM получает оптимальную производительность - коэффициент тока чтения до 10 7 и RT более 2 с. А при использовании оптимизированного программного напряжения ток считывания «0» намного ниже, чем указано в справочнике [16, 18], что помогает снизить энергопотребление.

Методы

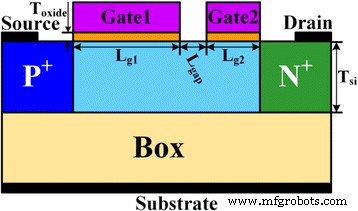

Структура DG-TFET, исследованная в этой статье, проиллюстрирована на рис. 1. Концентрация легирования как P + источник и N + сток 1 × 10 20 / см 3 . Собственный канал разделен на два сегмента:Gate1 и Gate 2, и есть небольшой промежуток между Gate1 и Gate2. Gate1 и Gate2 равны N + поликремний и P + поликремний соответственно. Знак P + Polysilicon Gate2 может создавать, а также поддерживать физическую емкость для хранения заряда и заменять традиционную DRAM на основе TFET, в которой используется P + Карманный регион в качестве области хранения. В то время как для N + поликремний Gate1, концентрация дырок в области перекрытия между Gate1 и Gate2 мала, что полезно для операции считывания. Таким образом, P + polysilicon Gate2 имеет более глубокую область хранения, которая может способствовать более длительному хранению, в то время как N + поликремний Gate1 выбран для управления механизмом туннелирования во время операции чтения [18].

Схема ячейки DG-TFET DRAM. На этом рисунке показана схема ячейки DRAM с двойным затвором TFET (DGTFET), включая Gate1, Gate2, исток, сток и канал. В этом дизайне область истока и область стока - P + допинг и N + допинг соответственно. Gate1 и Gate2 равны N + поликремний и P + поликремний соответственно

Подробные параметры устройства при моделировании следующие:толщина объемного кремния ( T si ) составляет 20 нм; длины Gate1 (Lg 1 ) и Gate2 (Lg 2 ) равны 400 нм и 200 нм соответственно; длина зазора ( L пробел ) между Gate1 и Gate2 составляет 50 нм; толщина оксида затвора (HfO 2 ) ( Т оксид ) составляет 3 нм. Оптимизированные условия программирования показаны в таблице 1. Рекомендации по оптимизации условий программирования будут подробно обсуждаться в следующих разделах.

Весь анализ проводится в инструменте Silvaco-Atlas с использованием нелокальной модели BTBT [19]. Нелокальный BTBT учитывает нелокальную генерацию электронов и дырок, поэтому он может более точно моделировать процесс туннелирования. Параметры модели туннелирования откалиброваны по экспериментальным данным в справочнике [20]. Кроме того, также используются физические модели, включая рекомбинацию Шокли-Рида-Холла, статистику Ферми, а также легирование и подвижность, зависящую от электрического поля. Согласно подходам [16,18] времена жизни электронов и дырок устанавливаются равными 100 нс. Температура по умолчанию - 300 К.

Результаты и обсуждение

Принцип работы ячейки DG-TFET DRAM отличается от принципа работы традиционной DRAM. И операции записи, и чтения основаны на BTBT, но каждая из них выполняет свою функцию. BTBT во время записи «1» приводит к тому, что дыры сохраняются в потенциальной яме под затвором 2, что может повысить ток считывания «1». Во время операции чтения ток стока в основном зависит от BTBT возле истока. Кроме того, эти два шлюза также действуют как разные роли:Gate1 и Gate2 в основном определяют операцию чтения и операцию записи соответственно.

Операция записи

Во время записи «1» Gate2 с отрицательным смещением будет увеличивать энергетическую полосу канала под Gate2, что уменьшает ширину барьера и создает BTBT между каналом и стоком. И это отрицательное смещение затвора 2 также вызывает глубокую потенциальную яму под затвором 2. Из-за туннелирования электронов из канала в сток область канала под затвором 2 полностью истощена, и в этой потенциальной яме накапливается много дырок. Во время записи «0» Gate2 с положительным смещением заставляет дырки вытесняться из потенциальной ямы, которая рекомбинирует на стороне стока [21].

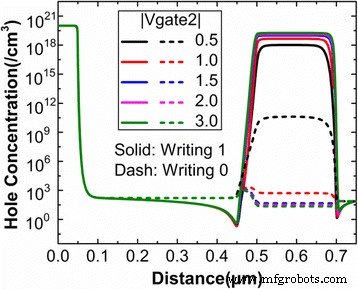

Как правило, абсолютное значение напряжения затвора 2 остается неизменным при записи «1» и записи «0». На рисунке 2 показано изменение концентрации дырок в зависимости от напряжения Gate2 после операции записи. Когда напряжение затвора 2 составляет 0,5 В, концентрация дырок после записи «0» выше из-за наличия потенциальной ямы, которая губительна для состояния «0». Когда абсолютное значение напряжения затвора 2 выше 1 В, концентрация дырок после записи «0» и записи «1» не имеет очевидных изменений. Это предполагает, что BTBT насыщается для записи «1» и что все накопленные дыры во время записи «1» вытесняются из потенциальной ямы после записи «0». И разница в концентрации дырок между записью «1» и записью «0» очень очевидна, что помогает различать состояние «1» и состояние «0».

Концентрации дырок на поверхности канала после операции записи. На этом рисунке показаны изменения концентрации дырок при разных напряжениях Gate2. Линия разреза берется на поверхности устройства от области истока до области стока. На этом рисунке сплошная линия и пунктирная линия представляют концентрацию дырок после записи «1» и записи «0» соответственно

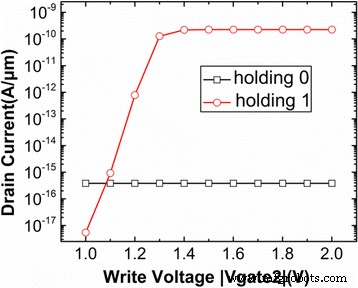

Но смещение Gate2 во время операции записи не может определяться только концентрацией дырок. Рисунок 3 показывает, что смещение затвора 2 во время операции записи оказывает значительное влияние на ток стока после операции удержания. Набор напряжения программирования во время операции удержания будет обсуждаться в следующем разделе. Рисунок 3 показывает, что ток стока после операции удержания не имеет очевидных изменений, когда абсолютное значение напряжения записи выше 1,3 В. Следовательно, -1,3 и 1,3 В считаются оптимальным напряжением затвора 2 во время записи «1» и написание «0» соответственно.

Слейте ток из DG-TFET, удерживая «0» и удерживая «1». На этом рисунке показано изменение тока стока после удержания «0» и удержания «1» по отношению к напряжению записи

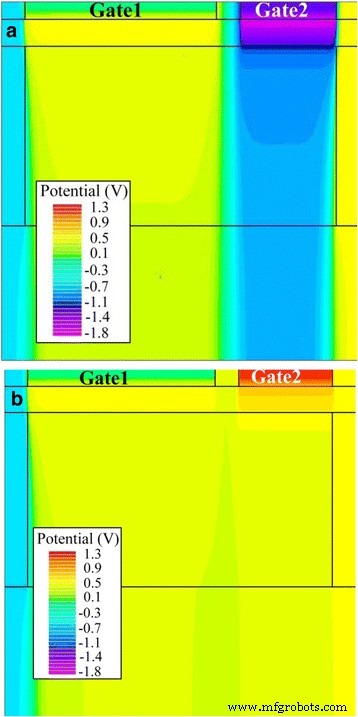

На рис. 4a, b, соответственно, показан контур потенциала после записи «1» и записи «0», когда абсолютное значение записывающего напряжения составляет 1,3 В. Очевидно, что очень глубокая потенциальная яма создается в области канала под затвором 2 после записи « 1 ”, как показано на рис. 4а. Накопленные дыры сохраняются в этой потенциальной яме при записи «1». Однако накопившиеся дырки ускользают из этой потенциальной ямы во время записи «0».

Возможные контуры после a написание «1» и b запись «0», когда абсолютное значение напряжения затвора 2 составляет 1,3 В. a , b Потенциальные контуры после записи «1» и записи «0» соответственно. Контуры потенциала на этом рисунке извлечены, когда абсолютное значение напряжения затвора 2 установлено на 1,3 В

Операция приостановки

Процесс удержания в основном используется для изменения удержания обвинений. Обычно нулевое смещение используется во время операции удержания, чтобы снизить энергопотребление [22]. Во время операции выдержки накопленные дыры в потенциальной яме постепенно рекомбинируются из-за уменьшения глубины потенциальной ямы. Следовательно, основная цель оптимизации операции удержания - избежать рекомбинации дырок во время удержания «1». В этой конструкции небольшое отрицательное смещение применяется к затвору 2, чтобы удерживать дырки в потенциальной яме после удержания «1», тогда как потенциальная яма очищается от дырок после удержания «0».

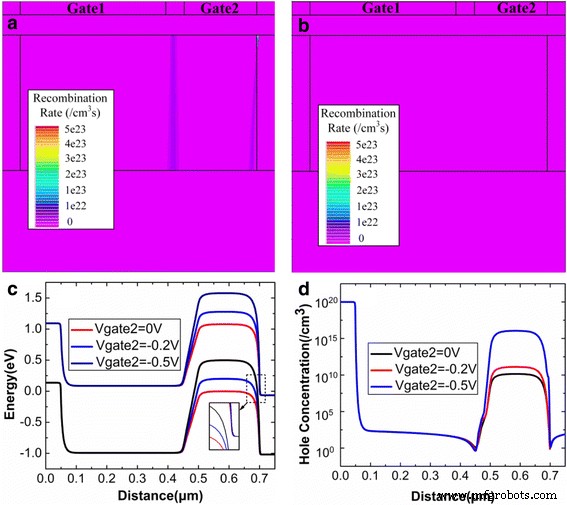

При более отрицательном напряжении Gate2 (-0,5 В) во время операции удержания рекомбинация дырок устраняется после удержания «1», как показано на рис. 5a, b. Устранение рекомбинации дырок способствует сохранению дырок во время удержания «1». На затвор 2 применяется небольшое отрицательное смещение, чтобы увеличить глубину потенциальной ямы и удерживать дыры в течение длительного времени, что выгодно для времени удерживания DGTFET DRAM. Во время удержания «0» отрицательное смещение затвора 2 может подтянуть энергетическую полосу области канала под затвором 2, что может предотвратить попадание электронов из BTBT между истоком и каналом в сторону стока. Следовательно, Gate2 с отрицательным знаком может уменьшить ток считывания «0». Однако затвор 2 с более отрицательным напряжением (-0,5 В) уменьшает расстояние туннелирования около стороны стока, как показано на рис. 5c. Это уменьшенное расстояние туннелирования приводит к тому, что BTBT приближается к стороне стока во время удержания «0», что способствует накоплению дырок в потенциальной яме во время удержания «0», как показано на рис. 5d. Таким образом, более отрицательное напряжение затвора 2 (-0,5 В) во время удержания «0» ухудшит состояние «0». Следовательно, чтобы исключить рекомбинацию дырок и BTBT во время удержания «1» и удержания «0», соответственно, -0,2 В рассматривается как оптимальное смещение затвора 2 во время операции удержания.

Скорость рекомбинации в ячейке DG-TFET DRAM после удержания «1», когда напряжение Gate2 равно a 0 В и b −0,5 В; c диаграмма энергетических зон и d концентрация дырок после удержания «0». а , b Скорость рекомбинации после удержания «1», когда напряжение Gate2 установлено на 0 В и -0,5 В соответственно. c Энергетический диапазон устройства от области истока до области стока. г Концентрация дырок в устройстве после отверстия «0». Энергетическая полоса и концентрация дырок извлекаются на 3 нм ниже оксида затвора

Операция чтения

Впоследствии также исследуется оптимизация операции чтения. Операция чтения сильно зависит от BTBT между P + источник и канал. Во время считывания «1» Gate1 в основном способствует BTBT на стороне истока, тогда как Gate2 с высоким напряжением снижает энергетический барьер, который препятствует потоку электронов из канала в сток. Но во время чтения «0» необходимо, чтобы Gate2 с небольшим напряжением был в состоянии предотвратить утечку электронов из канала в сток. Следовательно, оптимизация напряжений Gate1 и Gate2 очень важна для операции чтения.

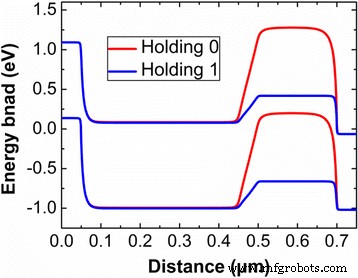

На рис. 6 показаны диаграммы различных энергетических зон после удерживания «1» и «0». Такие же напряжения применяются на сторонах затвора при чтении «1» и «0». Поскольку при считывании будут использоваться положительные смещения затвора, диапазон энергий будет записываться при чтении «1» или «0». Энергетический диапазон канала под Gate2 после удержания «0» выше, чем после удерживания «1», и этот энергетический диапазон также выше при считывании «0» по сравнению с таковым при считывании «1». Более высокая энергия канала под затвором 2 создаст эффективный барьер, препятствующий течению электронов в сторону стока, что уменьшит ток считывания «0».

Диаграмма энергетического диапазона после a удерживая «1» и b удерживая «0». а , b Энергетический диапазон устройства после удерживания «1» и «0» соответственно. Энергетическая полоса извлекается на 3 нм ниже оксида затвора

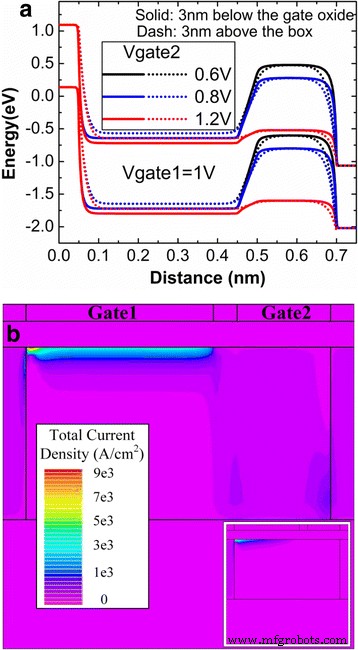

Во время операции считывания смещение стока устанавливается равным 1 В, так что ток стока может быть считан в DG-TFET. Во-первых, поддерживая напряжение Gate1 равным 1 В, измените смещение Gate2, чтобы выбрать оптимальное напряжение Gate2. Поскольку напряжение затвора 2 в основном влияет на ток считывания «0», оптимизация напряжения затвора 2 анализируется механизмом считывания «0». На рис. 7а показано изменение энергетического диапазона в зависимости от напряжения на затворе 2 после считывания «0». Когда напряжение затвора 2 ниже (0,6 или 0,8 В), канал под затвором 2 полностью истощается. Но когда напряжение затвора 2 повышается до 1,2 В, энергетическая полоса понижающего напряжения канала под затвором 2 не может создать эффективный барьер, препятствующий течению электронов в сторону стока. На рисунке 7b и на вставке соответственно показана общая плотность тока после считывания «0», когда напряжение затвора 2 составляет 1 В и 0,8 В. Очевидная плотность тока может быть четко обнаружена в области канала под затвором 2, когда напряжение затвора 2 равно 1 В, что будет вызывают ток более высокого показания «0». Таким образом, 0,8 В считается оптимальным напряжением Gate2 для процесса чтения.

а Диаграмма энергетического диапазона и b общая плотность тока после считывания «0». а , b Энергетический диапазон и общая плотность тока после считывания «0» соответственно. Энергетическая полоса извлекается на 3 нм ниже оксида затвора

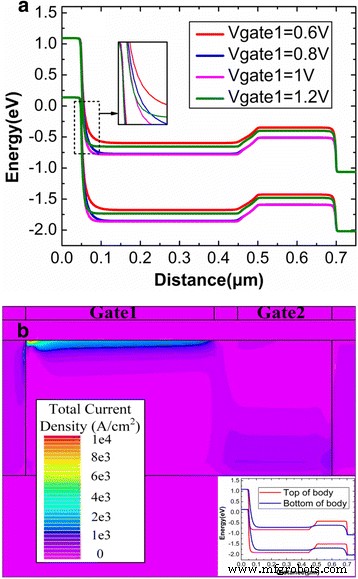

Наконец, также проводится оптимизация смещения Gate1. На рис. 8а показано изменение верхней полосы энергий в зависимости от напряжения на затворе Gate1. Ширина барьера BTBT на стороне источника постепенно уменьшается с увеличением напряжения Gate1, но эта тенденция к снижению начинает насыщаться, когда напряжение Gate1 выше 1 В. А напряжение Gate1 1 В не может оказать серьезного влияния на показание «0». », Что было продемонстрировано на рис. 7b. Следовательно, 1 В считается оптимальным смещением Gate1 во время операции чтения.

а Диаграмма энергетического диапазона и b общая плотность тока после считывания «1». а , b Энергетическая полоса и общая плотность тока после считывания «1» соответственно. Энергетическая полоса извлекается на 3 нм ниже оксида затвора

Согласно приведенному выше анализу глубокая потенциальная яма формируется только в верхней части канала под затвором 2 после записи «1». Следовательно, в области канала под Gate2 полоса энергии в верхней части канала намного выше, чем в нижней части канала. Это демонстрирует, что наверху канала под Gate2 будет барьер во время считывания «1». На вставке к рис. 8b показана энергетическая полоса как вверху, так и внизу канала после считывания «1». Можно четко определить, что между воротами 1 и 2 в верхней части канала существует более высокий барьер канала, но этот барьер не существует в нижней части канала. Следовательно, во время считывания «1» путь проводимости находится вверху канала под затвором 1 и внизу канала под затвором 2, что может быть ясно продемонстрировано плотностью тока на рис. 8.

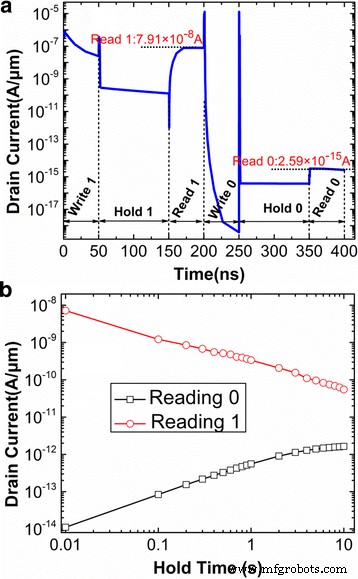

При применении вышеупомянутого оптимизированного условия программирования переходная характеристика ячейки DG-TFET DRAM показана на рисунке 9. Время записи и чтения установлено на 50 нс, а время удержания установлено на 100 нс. На рис. 9a текущее отношение значения «1» к значению «0» составляет 10 7 . , что намного больше 10 2 ~ 10 3 по ссылке [16, 18, 23]. Кроме того, когда время удержания увеличивается до 10 с, коэффициент тока все еще превышает 10. В [16], когда время удержания увеличивается до 2 с, коэффициент тока составляет всего около 10. Следовательно, RT DG-TFET DRAM с оптимизированным условием программирования превышает 2 с. Таким образом, оптимизированное условие программирования заставляет ячейку DG-TFET DRAM получить не только более высокий коэффициент тока чтения, но и большее RT. Более того, ток считывания «0» при оптимизированном программном напряжении намного меньше, чем в справочнике [16, 18, 22, 23], что позволяет использовать его для приложений с более низким энергопотреблением.

а Переходные токи стока в последовательности срабатывания; б изменение считываемого тока в зависимости от времени выдержки. а Переходный ток ячейки DGTFET DRAM во время операций записи, удержания и чтения. б Варианты чтения «1» и «0» тока с разным временем выдержки

Выводы

Подробное руководство по оптимизации условий программирования для DG-TFET DRAM предлагается в этой статье с использованием инструмента моделирования Silvaco-Atlas. Во время записи «1» затвор 2 с отрицательным напряжением (-1,3 В) создает потенциальную яму, а BTBT между каналом и стоком заставляет дырки накапливаться в этой потенциальной яме. Во время записи «0» Gate2 с положительным напряжением (1,3 В) заставляет дырки выходить из потенциальной ямы. Для операции удержания небольшое отрицательное напряжение (-0,2 В) прикладывается к затвору 2 для удержания отверстий, что может улучшить ток считывания «1». После удержания «0» барьер канала под затвором 2 может сопротивляться электронам, движущимся к стороне стока, чтобы уменьшить ток считывания «0». Для оптимизации операции чтения большее напряжение Gate1 (1 В) в основном используется для увеличения BTBT на стороне истока во время считывания «1», тогда как соответствующее напряжение Gate2 (0,8 В) используется для сопротивления электронам, движущимся к стоку во время чтения. «0». Условия оптимизированного программирования заставляют DG-TFET DRAM получить более высокий коэффициент тока (10 7 ) от значения «1» до значения «0» и времени удерживания более 2 с. А чрезвычайно низкий ток считывания «0» помогает снизить энергопотребление.

Наноматериалы

- Преимущества удаленного мониторинга, удаленного программирования и профилактического обслуживания

- Решение проблем многоядерного программирования и отладки

- Макетирование и программирование ATmega328P и ATtiny45 в Atmel Studio 7

- Использование технологий на основе Интернета вещей на строительной площадке

- Биометрическая система безопасности на основе сердцебиения человека

- Комментарий:понимание методов программирования роботов

- Процесс проектирования и внедрения автоматизации производства

- Заполните пустое поле Упражнение по программированию ЧПУ Несколько дуг

- Заполните пустое упражнение по фрезерованию с ЧПУ

- Заполните пустое упражнение по программированию ЧПУ