Интегрированная RRAM 4T SRAM с самоторможением резистивной коммутационной нагрузки с помощью логического процесса Pure CMOS

Аннотация

В этой статье описывается новая полностью совместимая с логикой энергонезависимая статическая память с произвольным доступом (NV-SRAM) с полной логической совместимостью, в которой реализован механизм самоограничения хранения данных для приложений маломощной / высокоскоростной SRAM. Благодаря компактной площади ячеек и полной логической совместимости эта новая NV-SRAM включает в себя две STI-ReRAM, встроенные в 4T SRAM. Данные могут быть прочитаны / записаны через энергозависимую структуру с перекрестными парами для поддержания высокой скорости доступа. Данные могут быть энергонезависимо сохранены в новой ячейке SRAM с помощью уникальной операции самоторможения нагрузки на резистивную память с произвольным доступом (RRAM), что обеспечивает нулевую статическую мощность во время удержания данных.

Фон

В последние годы были разработаны различные маломощные статические запоминающие устройства с произвольным доступом для удовлетворения потребностей в вычислительных системах на портативных устройствах и приложениях IOT [1,2,3,4,5,6]. По мере того, как технология CMOS масштабируется до нанометрового режима, ток утечки в закрытом состоянии резко возрастает, что приводит к ухудшению статического энергопотребления энергозависимых модулей памяти [7, 8]. Статическое энергопотребление, вызванное током утечки в наноразмерных транзисторах, стало одной из ключевых проблем для развития маломощных SRAM. [9,10,11]. За прошедшие годы были предложены различные структуры ячеек или методы работы [12,13,14,15,16] для минимизации энергопотребления в SRAM. Некоторые из недавно предложенных ячеек включают в себя элементы энергонезависимой памяти, такие как резистивная память с произвольным доступом (RRAM) и магниторезистивная память с произвольным доступом (MRAM) [17,18,19,20], для достижения мощности удержания нуля при сохранении низкой производительности. мощность и быстрая скорость доступа при обработке изменчивых данных. Однако добавление энергонезависимых запоминающих элементов к логическим массивам SRAM обычно требует дополнительных уровней и / или процессов к стандартным логическим платформам [21,22,23]. Это неизбежно увеличит сложность процесса их разработки. Кроме того, эти внутренние RRAM и MRAM требуют большой соединительной структуры, состоящей из нескольких наборов переходных отверстий и металлов для ячеек SRAM. Эти мостовые структуры увеличивают паразитную емкость узла хранения данных SRAM, влияя на скорость доступа этих энергонезависимых ячеек SRAM [24, 25]. В нашей предыдущей работе [26] впервые была предложена новая NV-SRAM 4T с нулевой статической мощностью с RRAM STI-sidewall, расположенными рядом с плавающими узлами хранения 4T SRAM. В этом письме эта NV-SRAM 4T2R с энергонезависимым хранилищем данных, нулевым удержанием мощности и высокой скоростью доступа будет дополнительно проанализирована и оптимизирована для встроенных приложений NVM.

Методы

Структура ячейки STI-ReRAM

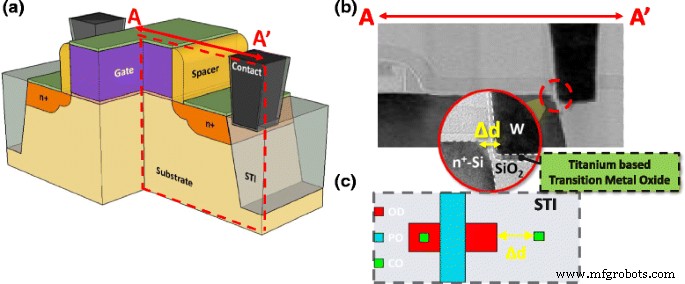

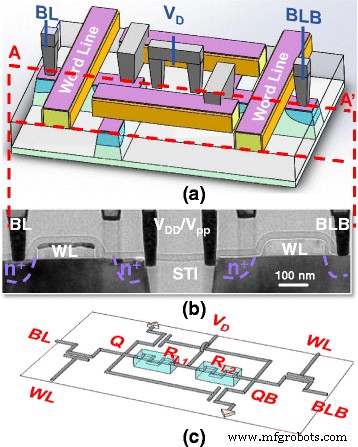

В структуре 3D STI-RRAM на рис. 1a резистивный накопительный узел состоит из оксида переходного металла (TMO) между двумя электродами, областью N + и вольфрамовой пробкой с левой и правой стороны соответственно. Как показано на изображении ПЭМ на рис. 1b и компоновке на рис. 1с, поместив контакт в область STI на надлежащем расстоянии от области N +, оставшийся SiO 2 и барьерный слой под вольфрамовой пробкой становятся пленкой TMO и обладают резистивным качеством переключения.

а Трехмерное изображение ячейки 1T1R с STI-ReRAM рядом с переходом n +. б Соответствующее электронно-микроскопическое изображение резистивного накопительного узла, состоящего из оксидов переходных металлов, образованного между специально размещенным контактом и областью n + выбранного транзистора. c Макет

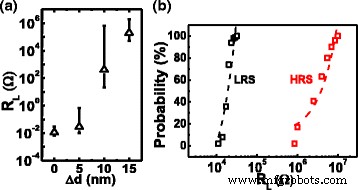

Толщиной TMO можно управлять, выбирая надлежащее расстояние Δd между контактом и областью диффузии N +. На основании измерения на рис. 2а, существует положительная корреляция между начальным уровнем сопротивления и протянутым расстоянием Δd, определяемым масками, определяющими области STI и контакта, соответственно. Для следующего исследования RRAM с Δd, равным 10 нм, выбран из-за его более низкого напряжения формирования и предпочтительного R L распределение как в состоянии с низким сопротивлением (LRS), так и в состоянии с высоким сопротивлением (HRS), как показано на рис. 2b. При правильном управлении напряжением Wordline (WL) во время операций набора / формирования установленный ток может быть локально ограничен транзистором выбора, что обеспечивает более высокие показатели износостойкости.

а Измеренное начальное сопротивление образцов STI-RRAM с разным △ d. б Суммарная вероятность сопротивления нагрузки после сброса / установки STI-RRAM в состояниях высокого и низкого сопротивления

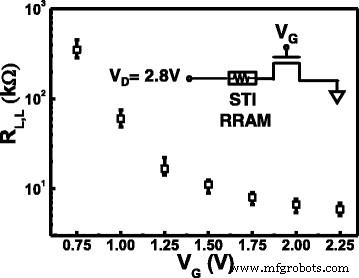

Данные на рис. 3 также показывают, что уровень тока считывания в LRS можно хорошо контролировать с помощью напряжения затвора V G . Во время формирования на V D =2,8 В, транзистор выбора ограничивает максимальный ток, проходящий через STI-RRAM после того, как устройство настроено на LRS. Последующий уровень сопротивления состояния LRS обратно пропорционален локально ограниченному току, который был обнаружен в различных устройствах RRAM на основе TaO [27, 28].

Корреляция между уровнями сопротивления нагрузке, R L, L , и приложенное напряжение затвора во время установки. Данные показывают, что разные R L, L можно получить, установив другой уровень выбранного напряжения затвора

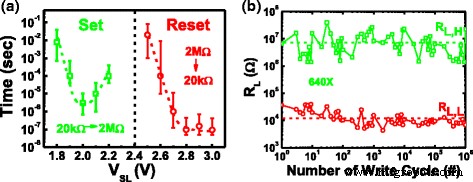

Чтобы гарантировать резистивную коммутационную характеристику STI-RRAM, проверяются время до установки и время до сброса, как показано на рис. 4a. Операции установки и сброса могут быть оптимизированы, когда V SL =2 и 2,8 В соответственно. Результаты испытаний на выносливость RRAM приведены на рис. 4b. При использовании алгоритма пошагового программирования импульсов окно чтения может оставаться стабильным после 1 миллиона циклов.

а Суммарное время установки и время сброса по сравнению с V PP . б Результат одного миллиона циклов испытаний на износостойкость STI-RRAM с использованием алгоритма пошагового импульсного программирования

Концепция энергонезависимой SRAM

Трехмерная иллюстрация на фиг. 5 показывает недавно предложенную структуру ячеек nv-SRAM 4T2R и соответствующее изображение ПЭМ в поперечном сечении вдоль линии разреза AA ’. Два модуля STI-RRAM служат как узлами энергонезависимой памяти, так и нагрузочными резисторами, которые зажаты между диффузионными областями Q и QB N +, а контакт плотно прилегает к краям STI с правильной конструкцией разнесения. На TEM-изображении показан хорошо сформированный STI-RRAM как с левой, так и с правой стороны области изоляции, и в результате получается довольно компактная ячейка с близко расположенными узлами энергонезависимой памяти на том же уровне, что и транзисторы.

а Трехмерная иллюстрация предлагаемой структуры ячеек nv-SRAM 4T2R и b Соответствующее поперечное сечение ПЭМ-изображение. c Принципиальная схема ячейки SRAM показана с двумя резисторами RRAM в качестве устройств загрузки

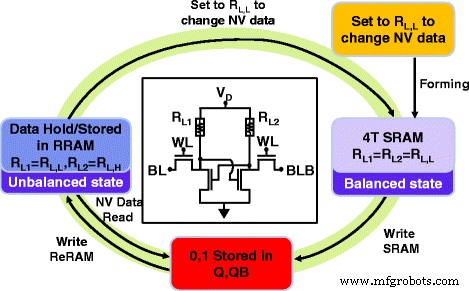

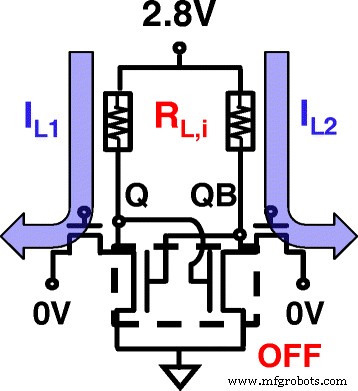

Предлагаемый 4T nv-SRAM может работать в энергонезависимом и энергонезависимом режимах. Его четыре различных состояния и схема работы показаны на рис. 6.

Принципиальная схема ячейки NV-SRAM и соответствующая блок-схема переключения между энергозависимыми и энергонезависимыми операциями SRAM

В исходном состоянии STI-RRAM обычно имеет уровень сопротивления 10 8 . Ω, а пленка TMO цела. Посредством операции формирования бланкета ячейки nv-SRAM могут быть инициализированы одновременно в блочном режиме в V D =2,8 В. Оба R L1 и R L2 (сопротивление нагрузки слева и справа соответственно) инициализируются на R L, L . Финальный R L, L Уровень 20 ~ 370 кОм можно контролировать, подав различное напряжение WL во время операции формовки. Затем ячейка достигает состояния баланса, что означает, что два нагрузочных резистора находятся в одинаковом состоянии. В этом состоянии эта ячейка теперь может функционировать как типичная SRAM 4T2R, обрабатывая энергозависимые данные обычным способом, сохраняя данные в перекрестно-связанной защелке.

Чтобы хранить данные в энергонезависимой памяти, дополнительные фиксированные данные могут быть сохранены в RRAM с помощью механизма самоторможения, унаследованного в этой ячейке. Когда данные успешно сохранены в паре RRAM, можно отключить питание для постоянного хранения данных. Чтобы получить доступ к сохраненному состоянию, просто повторно примените V DD в массив. Энергонезависимые данные будут автоматически восстановлены в узлах Q и QB, и к ним можно будет получить доступ в обычном режиме чтения SRAM. Наконец, чтобы обновить энергонезависимые данные, к массивам SRAM применяется операция бланкетного набора, чтобы массив вернулся в свое состояние баланса.

Результаты и обсуждение

Электрический анализ

Условия работы для переходов между различными стадиями приведены в Таблице 1.

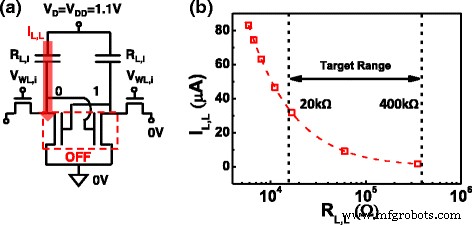

Разные R L, L уровень может быть получен установкой другого напряжения WL во время инициализации блока или массива. Учитывая стабильность и рабочее напряжение, R L, L Уровень в диапазоне от 20 до 400 кОм в первую очередь рассматривается в данном исследовании. При соответствующем напряжении WL от 0,75 до 1,25 В результирующее сопротивление нагрузки уменьшается довольно линейно, как показано на рис. 3. Как и ожидалось, более низкие R L, L уровень приведет к более высокому току в режиме ожидания, см. рис. 7. Однако R L, L должен оставаться достаточно низким, чтобы обеспечить большое окно увеличения данных между двумя состояниями сопротивления. Для дальнейшей оптимизации целевых R L, L необходимо учитывать окно статических, динамических и энергонезависимых данных. , который задается условием инициализации.

а Ячейка SRAM 4T2R в состоянии удержания. б Как и ожидалось, уровень сопротивления нагрузке, I L, L во время удержания можно эффективно снизить, выбрав более высокое значение R L, L

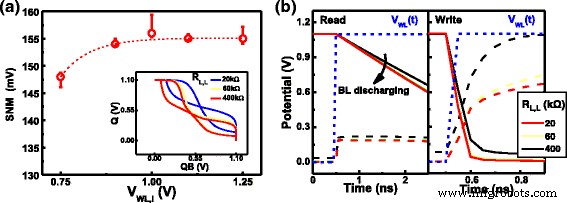

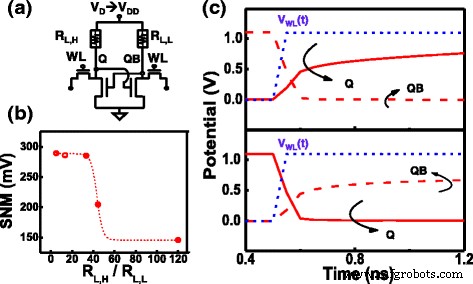

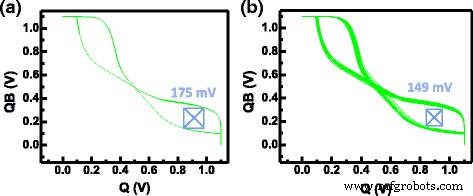

Сначала исследуются статические и динамические характеристики NV-SRAM в состоянии баланса с учетом ячеек, инициализированных при различных условиях. На рис. 8 представлен запас статического шума (SNM), полученный с помощью нескольких кривых «бабочка» ячеек, инициализированных различным напряжением WL. Данные показывают, что R L, L Уровень имеет минимальное влияние на предел чтения сбалансированных ячеек, когда резисторы нагрузки находятся в пределах целевого диапазона. Распределение SNM нескольких ячеек в состояниях баланса при различных условиях инициализации показано на рис. 8a. В целом SNM остаются довольно стабильными от ячейки к ячейке, в то время как разумный запас по чтению может быть установлен при напряжении WL ниже V DD , что может быть полезно для приложений с низким энергопотреблением. Чтобы исследовать динамические характеристики чтения и записи этой ячейки в сбалансированном состоянии, переходная характеристика записи «1» и «0» суммирована на рис. 8b. Установлено, что более высокие R L, L снижает скорость подтягивания к узлам Q, QB, что может немного увеличить переходное время во время операций чтения и записи. Однако скорость отклика все еще находится в ожидаемом диапазоне. Приведенные выше данные предполагают, что в состоянии балансировки эта nv-SRAM 4T2R может обрабатывать изменчивые данные как обычные SRAM.

а Запас статического шума чтения (SNM) предлагаемых ячеек SRAM с различным напряжением WL во время инициализации. Разумный SNM может поддерживаться в довольно большом диапазоне R L, L от 20 до 400 кОм. б Характеристики динамического чтения и записи ячейки в условиях сбалансированной нагрузки показывают хорошее время отклика в течение наносекунд. Высшее R L, L немного снижает скорость подтягивания во время операции записи

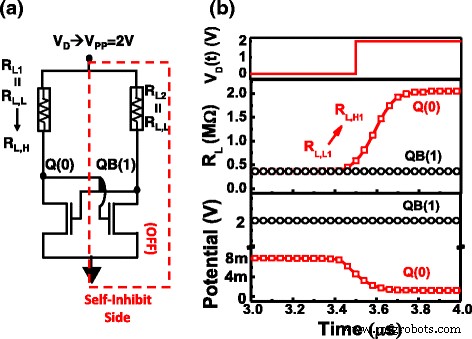

Для хранения данных в паре STI-RRAM эта ячейка обеспечивает самоселективный сброс только одного из RRAM в паре нагрузочного резистора, что позволяет записывать данные в энергонезависимом режиме, применяя более высокое значение V pp напряжение на узел питания на ячеечный блок равномерно. После того, как данные защелки сохранены в узлах Q и QB, энергонезависимая запись достигается с помощью механизма самоблокировки в структуре перекрестной связи с RRAM, как показано на рис. 9a. Только одна сторона RRAM с низким напряжением в узле Q будет сброшена на R L, H . Ток на другой ветви почти равен нулю, поскольку понижающий транзистор отключен низким V Q . .

а Иллюстрация механизма самоблокировки во время записи энергонезависимых данных путем сброса одной стороны двух RRAM. б Динамическое изменение R L и Q, QB потенциал подтверждают самоблокирующуюся запись данных защелки в RRAM

Данные хранятся в паре RRAM как V PP на питающий узел подается импульс. При записи энергонезависимых данных динамическое переключение R L и переходная характеристика потенциала Q, QB показаны на рис. 9b. Данные измерений показали, что для успешного сброса STI-RRAM выборочно на одной стороне импульс 300 нс при V pp =2 В достаточно. Чтобы гарантировать, что энергозависимая работа все еще не затронута, когда ячейки находятся в несбалансированном состоянии, как показано на рис. 10a, распределение SNM ячеек с разными R L, H / R L, L отношения суммированы на рис. 10b. Обнаружено, что низкое отношение сопротивлений между состояниями не ухудшает удерживающий SNM. Чтобы гарантировать, что ячейка с несбалансированной нагрузкой, характерна динамическая запись данных в такую ячейку. Данные показывают, что оба состояния могут быть успешно записаны, преодолевая начальное соотношение сопротивления дисбаланса 2 M / 400 кОм, как показано на рис. 10c.

а Поперечная конструкция при неуравновешенной нагрузке. б Запас статического шума при различных напряжениях WL во время инициализации. c Динамическая запись для двух разных состояний данных. Дисбаланс R L, L =400 кОм также можно записать

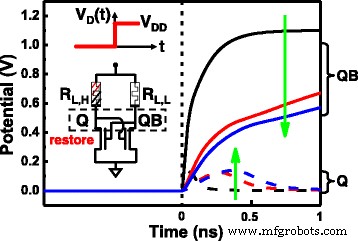

Чтобы загрузить изменчивые данные обратно, ранее сохраненные в RRAM, можно просто применить V DD к узлу источника питания, нагрузка дисбаланса в RRAM автоматически восстанавливается на узлах-защелках Q и QB, как показано на рис. 11.

Восстановление энергонезависимых данных, хранящихся в Q и QB, из состояния несбалансированной нагрузки RRAM. Потенциал узлов Q и QB может быть восстановлен после возобновления подачи питания в течение наносекунд

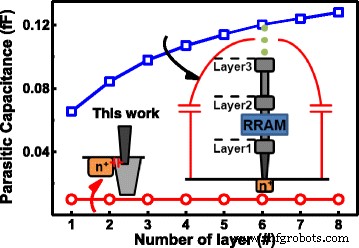

Паразитарный эффект и сравнение

Благодаря включению полностью совместимой с логикой STI-RRAM в эту новую ячейку SRAM, эта ячейка может быть легко реализована с помощью большинства стандартных логических процессов без добавления слоев маскировки, а также этапов процесса. Эта функция может значительно улучшить его приложения и гибкость в различных IP-модулях энергонезависимой памяти, необходимых во многих системах IC. Кроме того, предлагаемая nv-SRAM 4T2R имеет гораздо меньшую паразитную емкость по сравнению с другими ранее описанными NV-SRAM [29,30,31], для которых требуются энергонезависимые компоненты внутренней линии (BEOL). Чтобы соединить узел Q и QB с поверхности Si с этими BEOL RRAM или MRAM, необходимы несколько стопок металла и промежуточных слоев. Эти большие мостиковые структуры приводят к значительному паразитному влиянию RC. Большая паразитная емкость, представленная внутренним узлам внутри ячеек SRAM, может критически повлиять на время отклика устройств.

Чтобы сравнить паразитное влияние на них, nv-SRAM исследуются на основе оценки моделирования после компоновки. Предполагая, что все ячейки реализованы по одной и той же стандартной технологии CMOS, паразитная емкость на узлах защелки увеличивается по мере увеличения количества металлических слоев для ячеек, требующих больших мостиковых структур. Для новой nv-SRAM, использующей STI-RRAM, наблюдается очень небольшое увеличение общей емкости на фиксированных узлах. Кроме того, он не зависит от количества металлических слоев, адаптированных в конкретной схеме. Для дальнейшего исследования влияния паразитной емкости на скорость SRAM моделируемый динамический отклик ячеек SRAM, предложенный в [29,30,31], и результаты этой работы сравниваются на рис. 12.

Паразитная емкость на узлах защелки ячеек NV-SRAM из ссылки [30] и из этой работы, основанной на технологии КМОП 40 нм, обнаружено значительное увеличение паразитной емкости по мере увеличения количества металлических слоев

Значительно меньшая паразитная емкость этой встроенной NV-SRAM может привести к более быстрому времени отклика во время операции динамического чтения в ячейке SRAM. Это предотвращает влияние большой внутренней емкости соединительного моста на время отклика логического массива SRAM.

В таблице 2 сравниваются ключевые характеристики ранее описанных энергонезависимых SRAM, встроенных в внутренние RRAM или MRAM, и этой работы. Несмотря на более высокое напряжение переключения состояний, nv-SRAM на основе STI-RRAM имеет гораздо меньшую паразитную емкость на внутренних фиксированных узлах внутри ячеек SRAM и полную логическую совместимость.

Ухудшение запаса статического шума, вызванное изменением

Для обеспечения стабильного SNM с ячейками, подверженными изменениям процесса, колебаниям уровней сопротивления RRAM и порогового напряжения транзистора, V T , рассматриваются в следующих исследованиях:несовпадения в V T Известно, что с помощью масштабируемых технологий вызывает сдвиг SNM в SRAM [32, 33]. Кроме того, это также может вызвать различный установленный ток согласования, что, в свою очередь, может привести к увеличению вариации уровня сопротивления двух R L, L . Как показано на рис. 13, разные V T привести к разному току соответствия инициализации в ячейке STI-RRAM, что приведет к дальнейшему несоответствию в R L, L . Чтобы проанализировать влияние V T вариация на SNM, мы предполагаем V T быть гауссовой случайной величиной со средним значением и вариацией на основе предыдущих отчетов [34]. При моделировании Монте-Карло распределение кривых «бабочка», подверженных изменениям R L, L суммированы на рис. 14а. Когда обе вариации в R L, L и VT, наблюдается значительное сужение окна SNM, как показано на рис. 14b. Повышенная изменчивость NV-SRAM должна быть рассмотрена в будущих исследованиях.

V T вариации приводят к различному соответствию инициализации I L, 1 и я L, 2

Кривые «бабочка» по результатам моделирования методом Монте-Карло, сравнивающие деградацию SNM, вызванную a вариация в R L, L после инициализации и b вариации в обоих R L, L и V T

Выводы

Новая энергонезависимая SRAM на основе 4T2R STI-RRAM, полностью логически совместимая с процессом логики CMOS, была успешно продемонстрирована в процессе чистой логики CMOS на технологическом узле 40 нм без дополнительных масок или шагов. Эта ячейка nv-SRAM имеет механизм самоторможения, самовосстановления для энергонезависимых данных, небольшую паразитную емкость на узлах защелки и нулевую статическую мощность во время удержания данных. Эти превосходные характеристики делают NV-SRAM на основе STI-RRAM многообещающим решением для приложений энергонезависимой памяти с низким энергопотреблением / высокой скоростью работы логики в будущем.

Наноматериалы

- Введение в цифровые интегральные схемы

- Интегральные схемы

- Цифровая логика с обратной связью

- Схемы переключения диодов

- Мощность в резистивных и реактивных цепях переменного тока

- Практическая коррекция коэффициента мощности

- Модель удержания TaO / HfO x и TaO / AlO x RRAM с характеристиками самовосстанавливающегося переключателя

- Характеристики биполярного резистивного переключения устройств RRAM с трехслойной структурой HfO2 / TiO2 / HfO2 на по…

- Резистивная память ZrO2 / ZrO2 - x / ZrO2 без соблюдения нормативных требований с управляемым межфазным режимом перек…

- Механизм проводимости и повышение выносливости в RRAM на основе HfO2 с лечением нитридом