Проектирование и исследование печатной платы высокоскоростной карты паролей на основе PCIE

В настоящее время быстрое развитие интернет-технологий свидетельствует о массовом применении электронной почты, онлайн-платежей и личного общения. На этом фоне информационная безопасность стала важной темой исследований во всем мире. Технология PKI (инфраструктура открытых ключей) обеспечивает безопасность с использованием теории и технологии открытых ключей. Технология PCIE (Peripheral Component Interface Express) получила широкое применение в высокоскоростных устройствах в качестве стандарта шины ввода-вывода третьего поколения, использующего последовательную передачу данных и технологию двухточечного соединения. В области проектирования цифровых систем относительно высокая тактовая частота приводит к некоторым проблемам с точки зрения целостности сигнала, целостности питания и перекрестных помех, а традиционная конструкция печатной платы не отвечает требованиям стабильности системы.

В этой статье предлагается схема проектирования печатной платы на высокоскоростной карте паролей на основе PCIE с учетом преимуществ высокоскоростной последовательной передачи данных PCIE.

Общая схема дизайна

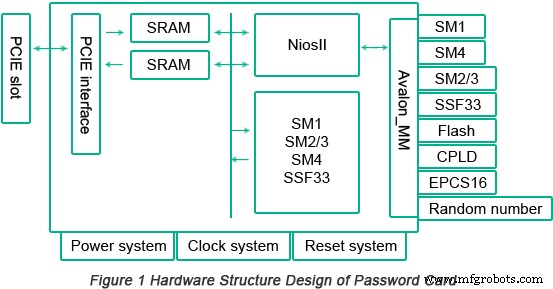

Чип FPGA EP4CGX50CF23C6N, принадлежащий Cyclone IV GX, разработанный Altera, применяется в этой конструкции, интегрируя хардкорный модуль PCIE IP и реализуя конструкцию с 4 картами паролей для высокоскоростной передачи данных. Четыре типа микросхем, микросхема 1, микросхема 2, микросхема 3 и микросхема 4, способны соответственно реализовывать алгоритмы SM1, SM2/SM3, SM4 и SSF33 и реализовывать функции инициализации карты паролей, администрирования секретных ключей, резервного копирования и восстановления, а также полномочий. управление. Карты паролей применяются в ПК, подключаются к основной плате ПК через слот PCIE и контролируются ПК. Hardcore IP в FPGA применяется для реализации PCIE, что приводит к связи между ядром PCIE и кешем SRAM и модулем управления. В качестве центра управления NiosII реализует функцию программного обеспечения карты паролей. Между тем, дополнительная микросхема пароля обеспечивает связь между каждым интерфейсным модулем и картой пароля. Аппаратная структура карты паролей показана на рисунке 1 ниже.

Проектирование высокоскоростной печатной платы

• Стек и компоновка

Конструкция стека является наиболее серьезной проблемой, которую следует учитывать, и разумная конструкция стека может подавлять излучение EMI (электромагнитных помех), сводя к минимуму переходное напряжение на плоскости питания или слое земли и экранируя электромагнитное поле сигнала и мощности. Как правило, в высокоскоростных цифровых схемах применяются многослойные платы и несколько мощностей. Конструкция стека печатных плат реализуется на основе комплексных элементов, включая тактовую частоту схемы, стоимость изготовления печатной платы, плотность контактов, срок изготовления и надежность. Кроме того, слои многослойной доски должны быть симметричными, а количество досок должно быть четным, поскольку асимметричная конструкция укладки приведет к короблению досок. Карта паролей, разработанная в этой статье, подключается к ПК через слот PCIE, а размер и форма печатной платы фиксированы:высота около 67 мм и длина около 174 мм, конфигурация интерфейса PCIE X4 внизу. В результате высокой плотности компонентов и толстой трассировки количество слоев печатной платы составляет 6 слоев с распределением сигнальный слой, уровень мощности, уровень сигнала, уровень мощности, слой земли, уровень сигнала. Эта конструкция содержит 3 уровня сигнала, 1 уровень заземления и 2 уровня мощности, обеспечивая среду, необходимую для обеспечения целостности сигнала.

После определения компоновки печатных плат следует реализовать группы компонентов и компоновку. Во-первых, положение компонентов должно быть запрограммировано в соответствии с размерами и рисунком печатной платы, принимая во внимание линейное соединение, функциональное разделение и отделку между компонентами. Затем компоненты должны быть разумно распределены в соответствии с различными классами напряжения компонентов, чтобы сделать провода напряжения как можно короче, что способно уменьшить помехи шума питания и повысить стабильность питания. При размещении микросхемы следует обращать внимание на взаимосвязь между ее вспомогательной схемой и ее микросхемой, а также на размещение кварцевого генератора за тактовыми выводами. Компоненты с высоким уровнем шума следует избегать размещения вокруг кварцевого генератора и должны находиться рядом с его компонентами возбуждения. Кроме того, необходимо учитывать размещение каждого контакта питания и сигнальных контактов чипа, а также их положение и направление, отрегулированное на основе подключенных линий. Поскольку соотношение длины и ширины карты паролей составляет более 2:1 при фиксированных положениях слота PCIE, загрузочных отверстий и индикаторного светодиода, размещение компонентов для фиксированных компонентов должно быть рассмотрено в первую очередь при размещении компонентов. Кроме того, из-за большого количества соединительных линий между компонентом и FPGA компоновка компонентов должна быть реализована с FPGA в качестве центра перед расположением других компонентов, чтобы верхнее и нижнее пространство печатной платы можно было эффективно использовать для чтобы оставить достаточно места между компонентами и компонентами и позиционирующими отверстиями.

• Мощный дизайн

В конструкции высокоскоростной печатной платы проектирование системы питания напрямую связано с успехом всей системы. Шум, создаваемый питанием и заземлением, должен быть сведен к минимуму, чтобы обеспечить надежность продукции. Применение схемы распределения мощности в методе слоев связано с тем, что мощность распределяется через металл по всему слою, уменьшая силовое сопротивление и шум и повышая надежность. Поскольку печатная плата касается нескольких мощностей, следует применять конструкцию с несколькими уровнями мощности, способную устранить общедоступные помехи от связи импеданса в виде шумовой петли. Применение развязывающей емкости способно решить проблему целостности питания, так как конденсатор можно разместить только на нижнем или верхнем слое печатной платы, исходя из чего провода, соединяющие развязывающие конденсаторы, должны быть короткими и широкими. По материалу чипа можно рассчитать ток, проходящий через линии электропередач, и определить ширину выводов. Чем шире провода, тем больший ток они могут нести. Экспериментальная формула представлена следующим образом:W(ширина линии:мм) ≥ L(мм/А) x I(ток:А)

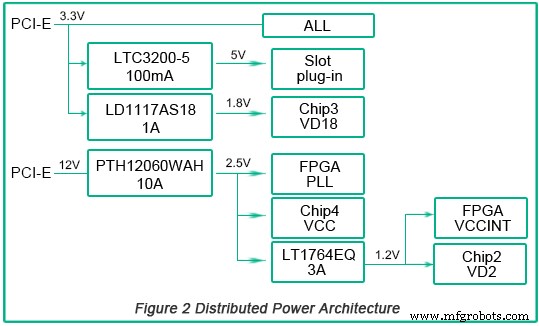

Несколько источников питания на печатной плате получают один или два типа питания от платы питания с помощью задней платы, а затем мощность преобразуется в другую мощность, необходимую компонентам. Преобразование мощности разделено на две архитектуры:централизованную архитектуру питания и архитектуру распределенного питания. Первый относится к мощности, поставляемой независимым источником, а затем преобразуется во все виды требуемой мощности, в то время как последний относится к многоступенчатому преобразованию энергии. Поскольку архитектура централизованного питания имеет недостатки, связанные с высокой стоимостью и большой площадью печатной платы, в этой конструкции применяется архитектура распределенного питания. Криптографическая карта касается 6 мощностей, включая 12В, 3,3В, 5В, 2,5В, 1,2В и 1,8В. Эта конструкция начинается с питания 3,3 В и 12 В в слоте PCIE, а затем питание 3,3 В способно генерировать питание 5 В и питание 1,8 В через микросхему преобразования напряжения, обеспечивая питание для подключаемого модуля и микросхемы 3. Затем питание 12 В преобразуется в питание 2,5 В для питания FPGA и чипа 4. Наконец, питание 2,5 В преобразуется в питание 1,2 В для питания FPGA и чипа 2. Архитектура распределенного питания криптографической карты показана на рисунке 2 ниже.

• Конструкция со сквозным отверстием

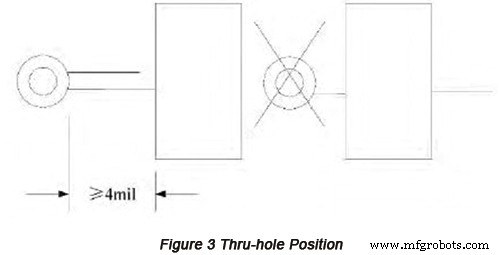

В процессе проектирования топологии многослойных печатных плат высокой плотности необходимо применять сквозные отверстия, передающие сигнал от одного слоя к другому для обеспечения электрической связи между слоями. Расположение сквозных отверстий должно быть выполнено с особой тщательностью. Сквозные отверстия не должны размещаться на площадке, и для соединения может применяться одна печатная линия, в противном случае могут возникнуть проблемы, такие как надгробный камень и недостаточное количество припоя. Паяльная маска должна быть нанесена на контактную площадку для сквозных отверстий с расстоянием, равным 4 милам, а сквозные отверстия не должны располагаться в центре контактной площадки для компонентов чипа на стороне пайки. Расположение сквозных отверстий показано на рисунке 3 ниже.

Кроме того, положение сквозного отверстия не должно быть слишком близко к золоту, сторона вставки которого должна иметь фаску. Для того, чтобы печатные платы вставлялись в разъем PCIE, на двух боковых краях вставной платы может быть предусмотрена фаска (1~1,5)x45°.

• Высокоскоростная маршрутизация сигнала

В процессе маршрутизации распределение должно быть разумно скорректировано, чтобы свести соединительные линии к минимуму, чтобы можно было уменьшить перекрестные помехи. В процессе маршрутизации высокоскоростных цифровых сигналов сигнальный уровень вблизи маршрутизации с несколькими уровнями мощности должен находиться далеко от эталонной поверхности мощности, чтобы избежать генерации обратного пути сигнальным током.

Поскольку частота высокоскоростного тактового сигнала относительно высока, джиттер, дрейф и деформация сильно влияют на систему, поэтому конструкция высокоскоростной печатной платы требует небольших помех сигнальных волн. Поэтому в первую очередь следует рассмотреть проблему распределения и маршрутизации часов. Маршрутизация должна быть реализована на высокоскоростных тактовых сигналах, а трассировка основных линий тактовых сигналов должна быть как можно короче, прямой и свободной от сквозных отверстий и частей питания, чтобы предотвратить перекрестные помехи между тактовыми импульсами и питанием. Когда несколько тактовых импульсов с разными частотами применяются на одной и той же печатной плате, две линии тактовых импульсов с разными частотами не должны поддерживаться параллельно. Однако для нескольких компонентов, использующих тактовые сигналы с одинаковой частотой, сеть может быть распределена по типу паука, типу дерева и типу ветвей.

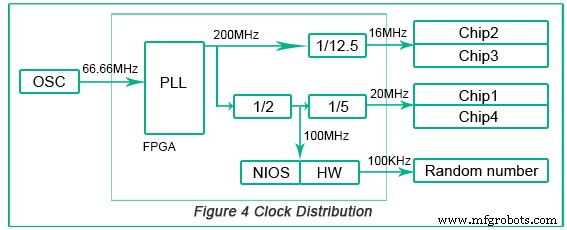

В высокоскоростной криптографической карте FPGA получает тактовую частоту 66,66 МГц через кварцевый генератор на печатной плате. После зацикливания со встроенными блокировками внутри FPGA генерируется базовая тактовая частота 200 МГц в качестве интерфейса для микросхемы 2 и микросхемы 3 для управления тактовой частотой. Затем обеспечивается тактовая частота 100 МГц после внутренней схемы деления частоты в виде программного ядра NiosII и рабочих тактовых импульсов аппаратной схемы внутри FPGA. Разделенная частота 16 МГц — это рабочие часы для микросхемы 2 и микросхемы 3, а разделенная частота 20 МГц — рабочие часы для микросхемы 1 и микросхемы 4. Распределение часов показано на рисунке 4 ниже.

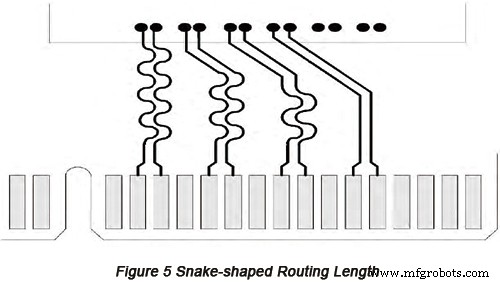

Высокоскоростная передача сигнала между слотом PCIE и ПК осуществляется с помощью высокоскоростной криптографической карты по пути дифференциальной маршрутизации пар, чтобы избежать проблем с целостностью сигнала. Вообще говоря, заземляющие провода не размещаются между сигналами дифференциальной пары, иначе эффект связи между сигналами дифференциальной пары будет разрушен. После разводки сигналов дифференциальной пары вокруг высокоскоростных сигналов печатной платы размещается медь, а свободное пространство полностью заполняется заземляющими проводами для повышения устойчивости схемы к электромагнитным помехам. Ключом к разводке печатных плат является сохранение симметрии дифференциальных пар. Если длина дифференциальных пар несовместима, это повлияет на точность чтения и записи данных из-за снижения скорости передачи данных. Чтобы обеспечить достоверность считывания данных системой в течение одного и того же периода, разница задержек между дифференциальными сигналами должна поддерживаться в пределах разрешенной категории, а длина маршрутизации должна быть строго одинаковой. Следовательно, для решения этой проблемы можно применить змеевидную маршрутизацию, отрегулировав временную задержку. В этой конструкции связь осуществляется ПК через PCIE и криптографическую карту, а передача и прием высокоскоростных сигналов осуществляется дифференциальными парными сигналами с длиной маршрутизации печатной платы, контролируемой в пределах 25 мил. Диаграмма соответствия змеевидной длины маршрутизации показана на рис. 5.

Полезные ресурсы

• Как проектировать высококачественные печатные платы

• Элементы дизайна печатных плат, влияющие на производство поверхностного монтажа

• Исследования по проектированию высокоскоростных печатных плат во встраиваемых прикладных системах

• Дифференциальная изометрическая обработка и Проверка с помощью моделирования высокоскоростного проектирования печатных плат

• Полнофункциональная услуга по изготовлению печатных плат от PCBCart — несколько дополнительных опций

• Усовершенствованная услуга по сборке печатных плат от PCBCart — начиная с 1 шт.

Промышленные технологии

- Материалы и дизайн печатных плат для высокого напряжения

- Возможности гибкого и жесткого изгиба при проектировании печатных плат

- Шаги и процесс Обучение защите проекта печатной платы

- Руководство от схемы до проектирования печатной платы на основе Altium Designer

- Неудачи и решения при проектировании радиочастотных печатных плат

- 3 метода разводки на печатной плате Проектирование высокоскоростной сигнальной цепи

- Советы по быстрой компоновке

- Расчет внутреннего рассеивания тепла печатной платы на основе тепловой модели

- Обсуждение питания и заземления в электромагнитной совместимости печатных плат

- Дифференциальная изометрическая обработка и имитационная проверка проектирования высокоскоростной печатн…