Оптимизация проектирования спейсеров для безконденсаторной DRAM на основе туннельного транзистора с двумя затворами

Аннотация

DRAM на основе туннельного полевого транзистора с двойным затвором (DGTFET) имеет преимущества безконденсаторной структуры и большого времени удерживания. В этой статье оптимизация проектирования спейсеров для DGTFET DRAM систематически исследуется с помощью инструмента Silvaco-Atlas с целью дальнейшего улучшения его производительности, включая снижение тока считывания «0» и увеличение времени удерживания. Результаты моделирования показывают, что прокладки на сторонах истока и стока должны применять диэлектрики с низким k и высоким k соответственно, что может повысить ток считывания «1» и уменьшить ток считывания «0». Применяя эту оптимизированную конструкцию спейсера, DGTFET DRAM получает оптимальную производительность - чрезвычайно низкий ток считывания «0» (10 −14 А / мкм) и большое время удерживания (10 с), что снижает статическое энергопотребление и динамическую частоту обновления. А ток низкого показания «0» также увеличивает его коэффициент текущей ликвидности (10 7 ) от значения «1» до значения «0». Кроме того, анализ масштабируемости показывает присущий ей недостаток, который предлагает дальнейшее направление исследования DGTFET DRAM.

Фон

Из-за уменьшения геометрии устройства динамическая память с произвольным доступом (DRAM) 1 транзистор (1T) –1 конденсатор (1C) столкнулась с трудностями при уменьшении масштаба, поскольку конденсатору трудно уменьшить свой размер [1,2,3] . Индустрия памяти предложила некоторые эффективные методы упаковки памяти с более высокой плотностью, такие как новые материалы и новые конструкции устройств [4, 5]. ОЗУ 1T с безконденсаторной структурой впервые было сообщено в начале 90-х годов [6, 7], и оно привлекает все большее внимание. В 1T DRAM состояние 1 (хранение носителя) достигается четырьмя способами:ударной ионизацией [8], биполярным переходным транзистором [9], межполосным туннелированием (BTBT) [10] и туннелированием затвора [11].

Туннельный полевой транзистор (TFET) на основе BTBT рассматривается как потенциальная альтернатива MOSFET из-за более высокого коэффициента переключения и чрезвычайно низкого тока в закрытом состоянии [12,13,14]. Преимущества TFET - низкий ток в закрытом состоянии и слабая температурная зависимость - чрезвычайно полезны для DRAM. В частности, низкий ток в закрытом состоянии может снизить считываемый ток «0» и статическое энергопотребление. В настоящее время некоторые группы работают над исследованием TFET DRAM [15,16,17,18,19,20]. Сообщается, что TFET DRAM имеет низкое значение тока «0» и высокое время удерживания (RT). Среди этих TFET DRAM наиболее заметной является DRAM с двойным затвором TFET (DGTFET) [19, 20]. В DGTFET DRAM операции записи и чтения основаны на BTBT. Исследования показывают, что ток чтения «0» DGTFET DRAM может достигать 1 нА / мкм, что намного меньше, чем у традиционной 1T1C DRAM. И RT 2 с намного превосходит целевое значение 64 мс, которое обычно устанавливается для времени динамического обновления в вычислительной системе [21]. RT DGTFET DRAM по-прежнему превышает 300 мс при повышении температуры до 85 ° C, что позволяет использовать его в суровых условиях. Кроме того, в DGTFET DRAM отказ от конденсатора большего размера также демонстрирует его конкурентоспособность в упаковке с высокой плотностью. Эти преимущества полностью указывают на необходимость изучения DGTFET DRAM. Хотя эти исследования продемонстрировали, что DGTFET имеет более высокую производительность, чем обычная DRAM 1T1C, результаты (RT и ток считывания «0») не оптимальны из-за того, что конфигурация устройства DGTFET не оптимизирована.

В этой статье конструкция проставки DGTFET оптимизирована для обеспечения оптимальной производительности DGTFET. В TFET прокладочные диэлектрики оказывают сильное влияние на BTBT [22, 23]. В DGTFET прокладки на сторонах истока и стока закрыты для туннельных переходов, поэтому они сильно влияют на производительность DGTFET DRAM. В этой статье систематически анализируется влияние диэлектрика спейсера (диэлектрика с низким или высоким k) в каждом спейсере на DGTFET DRAM и предлагается оптимизированная конструкция спейсера. За счет оптимизации конструкции спейсера ток считывания «0» понижен до 10 −14 А / мкм, а RT может достигать 10 с. Наконец, в этой работе также обсуждается масштабируемость DGTFET DRAM с оптимизированной конструкцией спейсера.

Структура устройства и метод моделирования

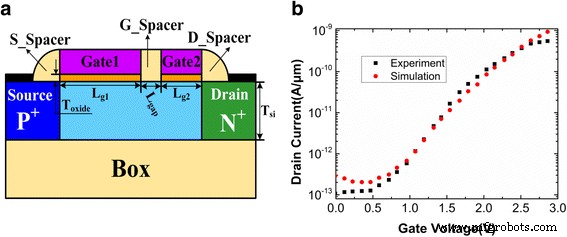

DGTFET с конфигурацией P-I-N показан на рис. 1a. Области истока и стока - P + допинг (10 20 / см 3 ) и N + допинг (10 20 / см 3 ), соответственно. Внутренняя область канала разделена на две части:область Gate1 с N + поликремний и область Gate2 с символом P + поликремний. Между воротами Gate1 и Gate2 небольшой промежуток. Знак P + Polysilicon Gate2 может создавать, а также поддерживать физическую емкость для хранения заряда и заменять традиционную DRAM на основе TFET, в которой используется P + Карманный регион в качестве области хранения. В то время как для N + поликремний Gate1, концентрация дырок в области перекрытия между Gate1 и Gate2 мала, что полезно для операции считывания. Таким образом, P + polysilicon Gate2 предназначен для создания более глубокой области хранения, которая может способствовать более длительному времени хранения, в то время как N + поликремний Gate1 выбран для управления механизмом туннелирования во время операции чтения [20]. На рис. 1a S_Spacer и D_Spacer относятся к распоркам на сторонах истока и стока соответственно. G_spacer относится к разделителю между Gate1 и Gate2. Материал прокладок по умолчанию - SiO 2 . . Параметры устройства по умолчанию следующие:толщина кремниевой пленки (T si ) составляет 20 нм, длина Gate1 (L g1 ) составляет 400 нм, длина Gate2 (L g2 ) составляет 200 нм, длина зазора затвора (L gap ) составляет 50 нм, а толщина оксида затвора HfO 2 (Т оксид ) составляет 3 нм.

а Схема ячейки памяти DRAM с двойным затвором TFET (DGTFET). б Сравнение моделируемой передаточной характеристики с экспериментальными результатами для КНИ ТФЭТ [25]

Моделирование DGTFET DRAM выполняется в Silvaco Atlas с использованием нелокальной модели BTBT. Модель нелокального BTBT-туннелирования учитывает пространственное изменение энергетических зон и генерацию / рекомбинацию носителей противоположного типа [24]. Параметры модели туннелирования откалиброваны согласно экспериментальным результатам КНИ ТФЭТ [25]. Масса туннеля электрона и дырки установлена равной 0,22 м 0 и 0,52 м 0 , соответственно, где m 0 - масса покоя электрона. Смоделированная передаточная характеристика SOI TFET согласуется с экспериментальными результатами, как показано на рис. 1b, который подтверждает модели, примененные в этой статье. Из-за сильного легирования в областях истока и стока также учитываются модель сужения запрещенной зоны и статистика Ферми-Дирака. Кроме того, также применяются модели рекомбинации Шокли-Рида-Холла, а также легирования и подвижности, зависящей от электрического поля. Все параметры модели согласуются с [19, 20]. Поскольку время жизни несущей определяет генерацию / рекомбинацию несущей во время операции удержания, это влияет на RT DRAM DGTFTET. В соответствии с различными временами жизни носителей, варьирующимися от 1 мкс до 10 нс в [26, 27, 28], время жизни электронов и дырок установлено на 100 нс. Соотношение Шарфеттера и модели Шенка используются для включения легирования и температурной зависимости срока службы соответственно.

Результаты и обсуждение

Механизм работы

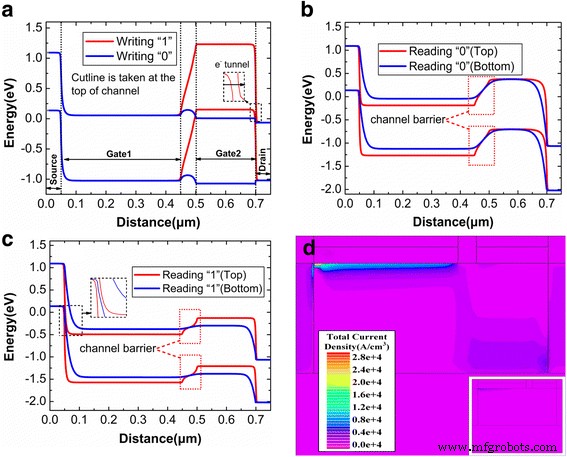

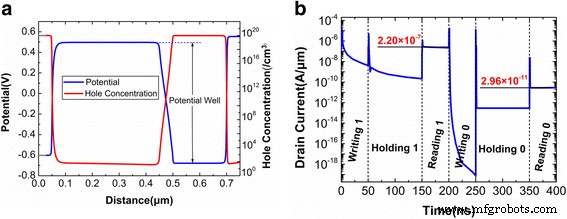

В DGTFET DRAM операциями записи и чтения управляет BTBT на переходах туннелирования стока и истока, соответственно. На рисунке 2 показаны энергетические диапазоны во время различных операций. Как показано на рис. 2a, во время записи «1» затвор 2 с отрицательным смещением значительно увеличивает энергетическую полосу канала под затвором 2, так что на стороне стока создается чрезвычайно маленький туннельный барьер. Таким образом, электроны туннелируют в сторону стока, и дырки накапливаются в глубокой потенциальной яме (1,2 В), как показано на рис. 3а. Во время записи «0» затвор 2 с положительным смещением заставляет дырки выталкиваться из этой потенциальной ямы и рекомбинировать на стороне стока [29]. На рис. 2б, в показаны энергетические зоны после считывания «1» и «0» соответственно. На рисунке 2b показано, что существует барьер канала между Gate1 и Gate2, но его не существует в нижней части канала. Кроме того, расстояние туннелирования со стороны источника меньше в верхней части канала. Это демонстрирует, что наклонный путь проводимости (от переднего интерфейса для Gate1 к заднему интерфейсу для Gate2) образуется во время считывания «1», что также может быть продемонстрировано плотностью тока на рис. 2d. Во время считывания «0» на рис. 2c можно найти очевидный барьер канала, который ограничивает ток считывания «0». Вставка на рис. 2d показывает, что электроны, туннелирующие из области источника, не могут пересечь этот барьер канала, чтобы сформировать ток с более высоким показанием «0».

Энергетические диапазоны от источника до стока. а Энергетические диапазоны после записи «1» с отрицательным смещением Gate2 и после записи «0» с положительным смещением Gate2. б Полосы энергии вверху и внизу канала после чтения «1». c Полосы энергии вверху и внизу канала после чтения «0». г Общая плотность тока после считывания «1»

а Потенциал и концентрация дырок на поверхности канала после записи «1». б Переходная характеристика тока стока для DGTFET DRAM, представленная в таблице 1

Правильное условие программирования важно для DGTFET DRAM. Большее отрицательное смещение должно быть применено к Gate2, чтобы насыщенный BTBT индуцировался во время записи «1». Во время удержания «1» на затвор 2 прикладывается небольшое отрицательное смещение для удержания дыр в потенциальной яме в течение длительного времени. Для операций чтения более высокое смещение Gate1 усиливает BTBT во время считывания «1», но это вредно для считывания тока «0». Gate2 с соответствующим смещением не только может увеличить ток считывания «1», но также может ослабить ток считывания «0». При применении условия оптимизированного программирования в таблице 1 переходная характеристика DGTFET DRAM с параметрами по умолчанию показана на рисунке 3b. Время записи и чтения, а также время удержания установлены на 50 нс и 100 нс соответственно. Полученное текущее отношение чтения «1» к значению «0» составляет около 10 4 . , что аналогично [17, 19, 20].

Влияние разделительных диэлектриков

В DGTFET DRAM использование диэлектриков low-k или high-k в трех прокладках (S_Spacer, G_Spacer и D_Spacer) будет влиять на его производительность. В этой конструкции диэлектрики с низким и высоким k выбирают SiO 2 и HfO 2 , соответственно. Если каждая прокладка использует SiO 2 или HfO 2 , всего будет восемь комбинаций дистанционной инженерии. Для более полного анализа, характеристики производительности DGTFET DRAM с каждой комбинацией, включая чтение «1» ( I 1 ) и «0» ( I 0 ) токи, а также коэффициент тока ( I 1 / Я 0 ), извлекаются из переходных характеристик, как показано в таблице 2. Для оценки RT эти параметры также извлекаются, когда время выдержки увеличивается до 2 с, что будет обсуждаться в следующих разделах. В таблице 2 буквы «S» и «H» обозначают SiO 2 . и HfO 2 соответственно, и три буквы каждого сокращения соответственно представляют S_Spacer, G_Spacer и D_Spacer.

Из Таблицы 2 можно выбрать оптимальную конструкцию распорки. Я 1 примерно 10 −7 А / мкм и 10 −9 А / мкм, когда SiO 2 и HfO 2 используются в S_Spacer соответственно. Когда D_Spacer применяет HfO 2 , Я 0 низкий до примерно 10 -14 А / мкм. Следовательно, оптимальная конфигурация разделителя DGTFET DRAM заключается в использовании диэлектриков с низким и высоким k со стороны истока и стока. Конкретные причины будут систематически анализироваться в следующих разделах.

Воздействие S_Spacer Dielectric

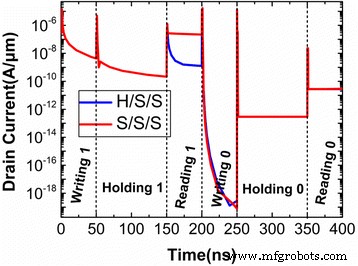

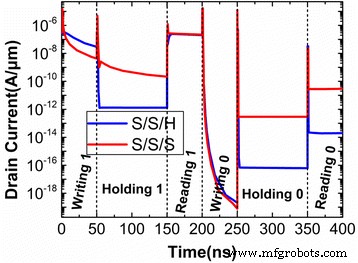

Чтобы проанализировать влияние S_Spacer, переходные характеристики токов стока для H / S / S и S / S / S сравниваются на рис. 4. Можно заметить, что значение тока «1» улучшается примерно на два. порядков, когда SiO 2 выбран в качестве диэлектрика S_Spacer.

Переходные характеристики дренажных токов для H / S / S и S / S / S, работающих в таблице 1

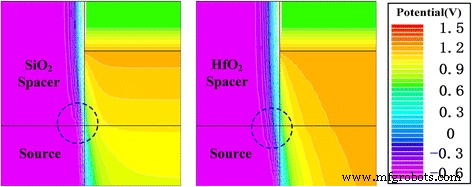

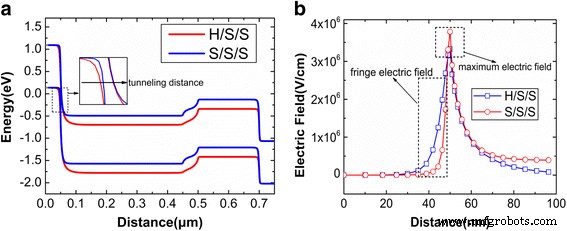

На рисунке 5 показаны потенциальные контуры S / S / S и H / S / S. В туннельном переходе источника область истощения поверхности H / S / S, очевидно, расширена по сравнению с областью S / S / S, как показано в круге на рис. 5. Расширенная область обеднения поверхности увеличивает ширину туннельного барьера. На рис. 6а показаны энергетические зоны после считывания «1». Как показано в увеличенной области этого рисунка, расстояние туннелирования (см. Стрелки) H / S / S, очевидно, больше, чем у S / S / S, что вызвано расширенной областью истощения поверхности. Кроме того, после считывания «1» электрическое поле в верхней части туннельного перехода источника показано на рис. 6б. Можно обнаружить, что краевое электрическое поле H / S / S больше, чем у S / S / S, что является основной причиной расширения области обеднения поверхности. Одним словом, S_Spacer с высоким k (HfO 2 ) диэлектрик генерирует большее пограничное электрическое поле, так что область обеднения поверхности в туннельном переходе источника расширяется, что увеличивает расстояние туннелирования электронов и снижает ток считывания «1». Кроме того, из рис. 6b также можно найти, что максимальное электрическое поле S / S / S больше, чем у H / S / S. Экспоненциальная связь между скоростью BTBT и электрическим полем делает туннельный ток в S / S / S намного больше, чем в H / S / S [30]. Следовательно, S_Spacer с диэлектриком с низким k (SiO 2 ) благоприятно влияет на значение тока "1".

Возможные контуры S / S / S (слева) и H / S / S (справа) после чтения «1»

а Диапазон энергий от истока до стока и b электрическое поле в верхней части туннельного перехода источника

На рис. 6а диэлектрик S_Spacer также влияет на энергетический диапазон области канала. На рис. 6b электрическое поле S / S / S больше в области канала, поэтому его потенциал канала меньше, чем у H / S / S. В результате более высокий уровень энергии можно найти в S / S / S. Но это не может повлиять на туннельный барьер и ток считывания «1».

Воздействие диэлектрика D_Spacer

Впоследствии D_Spacer также исследуется в этой статье. Сохранение постоянных S_Spacer и G_Spacer (SiO 2 используется в этих двух прокладках), различные переходные токи стока, вызванные различными диэлектриками D_Spacer, показаны на рис. 7. Помимо считывания «1» и записи «0», другие операции имеют очевидную зависимость от диэлектрика D_Spacer. Это связано с тем, что D_Spacer находится далеко от пути проводимости со значением «1» (нижняя часть канала под Gate2). Из предыдущего рабочего механизма можно понять, что операциями записи и удержания управляет Gate2, поэтому диэлектрик D_Spacer может оказывать влияние на эти две операции.

Переходные характеристики стоков стока для S / S / H и S / S / S, работающих в таблице 1

Во время операции удержания отверстия, накопленные во время записи «1», удаляются из потенциальной ямы и повторно объединяются на стороне стока. Таким образом, ток удержания «1» в основном возникает из-за рекомбинационного тока SRH. Из-за большей управляемости Gate2 по каналу в S / S / S, S / S / S имеет большую скорость рекомбинации и удерживающий ток «1». Но он намного меньше, чем ток BTBT при чтении «1», поэтому более высокий ток удержания «1» не может быть отражен в чтении тока «1».

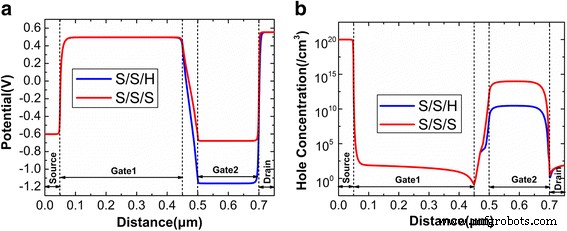

При записи «1» диэлектрик D_Spacer существенно влияет на глубину потенциальной ямы. Потенциальный контур на рис. 8а показывает, что D_Spacer с HfO 2 диэлектрик создает более глубокую потенциальную яму. Это означает, что эффективный BTBT между стоком и каналом распространяется в более глубокую область канала. Следовательно, ток записи «1» S / S / H выше, чем у S / S / S. Во время удержания «0», хотя небольшое отрицательное смещение (-0,2 В) применяется к затвору 2, оно также может увеличивать энергетическую полосу канала под затвором 2, что вызывает BTBT на стороне стока. Из предыдущего анализа можно было узнать, что D_Spacer с SiO 2 диэлектрик увеличивает BTBT в туннельном переходе стока во время удержания «0», что может быть продемонстрировано более высокой концентрацией дырок для S / S / S, как показано на рис. 8b. Следовательно, D_Spacer с SiO 2 диэлектрик приводит к более высокому удерживающему току «0».

а Возможный контур после написания «1». б Концентрация лунок после удержания «0»

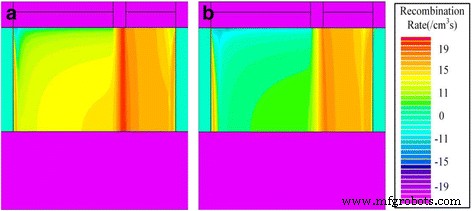

Во время считывания «0», поскольку барьер канала между затвором 1 и затвор 2 предотвращает протекание электронов в сторону стока, разница в считывании тока «0» для S / S / H и S / S / S в основном вызвана током рекомбинации. . Чем больше дырок накапливается во время удержания «0» для S / S / S, поэтому полоса падающей энергии делает скорость рекомбинации S / S / S больше, чем у S / H / S во время считывания «0», как показано на рис. 9. В результате, когда D_Spacer с использованием SiO 2 , более высокий ток считывания «0» следует отнести к более высокому току рекомбинации, который вызван большим количеством дырок, накопленных во время удержания «0».

Скорость рекомбинации a S / S / S и b S / S / H после чтения «0»

Таким образом, оптимальная конструкция разделителя для DGTFET DRAM заключается в том, что в разделителях на стороне истока и стока должны применяться диэлектрики с низким k и высоким k соответственно. Из Таблицы 2 видно, что G_Spacer не влияет на DGTFET DRAM, когда другие спейсеры остаются неизменными. Это потому, что BTBT, доминирующие в операциях записи и чтения, свободны от влияния G_Spacer.

Срок хранения

Как объяснялось ранее, рекомбинация и генерация дырок во время удержания «1» и «0» ухудшают состояние «1» и «0» соответственно. В результате необходимо изучить снижение производительности DGTFET DRAM при более длительном времени удержания. В таблице 2 I 1 и я 0 сильно ухудшаются с увеличением времени выдержки. На всех устройствах я 1 / Я 0 все еще больше 10 4 для устройства с оптимальной конструкцией проставки (S / S / H и S / H / H), когда время выдержки увеличивается до 2 с.

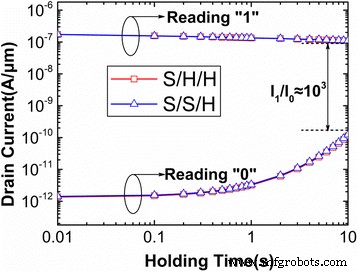

Как правило, время выдержки, необходимое для уменьшения максимального запаса чувствительности (разница между I 1 и я 0 ) на 50% оценивается как RT. В этой конструкции более строгий RT определяется как максимальное время выдержки, когда I 1 / Я 0 больше 10 3 . На рисунке 10 показано изменение тока считывания в зависимости от времени удержания для S / S / H и S / H / H. Можно обнаружить, что коэффициент текущей ликвидности S / H / S и S / H / H достигает 10 3 . при увеличении времени выдержки до 10 с. В результате RT DGTFET DRAM с оптимальной конструкцией спейсера может достигать 10 с. Это намного выше целевого значения 64 мс. В таблице 3 сравниваются рабочие характеристики в этой работе с таковыми в [17,18,19,20]. В [19, 20] коэффициент текущей ликвидности составляет всего 10 2 , а RT намного меньше 10 с. Кроме того, ток отсчета «0» в этой работе на два порядка ниже, чем в [19, 20]. Результаты экспериментов с FD-SOI TFET DRAM также показывают, что их показания по току «0» и RT ниже, чем в этой работе. Эти превосходные характеристики показывают, что DGTFET заменяет DRAM с низким энергопотреблением. Оптимизация конструкции спейсера позволяет DGTFET DRAM получать низкий ток считывания «0» и высокое RT, что помогает снизить статическое и динамическое энергопотребление.

Изменение считываемого тока в зависимости от времени удержания для S / S / H и S / H / H

Масштабируемость DGTFET DRAM

Хотя DGTFET DRAM решает проблему плотности ячеек памяти за счет исключения конденсатора большого размера, необходимо изучить его масштабируемость. Цель масштабируемости - поддерживать RT выше 2 с. Таблица 4 извлекает рабочие характеристики S / S / H с уменьшением на L g1 , L g2 , и L пробел . В Таблице 4 три цифры каждого сокращения представляют L g1 , L пробел , и L g2 .

Из таблицы 4 видно, что I 1 резко уменьшается, когда L g1 уменьшается до 100 нм с 200 нм. Масштабирование L g1 за пределами 100 нм сужает барьер, индуцированный n-типом, что приводит к снижению управляемости затвора и ухудшению I 1 . Я 0 значительно увеличивается с уменьшением L g1 и L g2 . Уменьшение L g2 уменьшает ширину барьера канала между Gate1 и Gate2, что способствует тому, что часть электронов пересекает барьер с образованием более высокого I 0 . Кроме того, постоянное уменьшение L g1 ослабляет способность Gate1 ограничивать туннелирование электронов на поверхности канала во время считывания «0». В таблице 4 L пробел не оказывает очевидного влияния на Я 1 , но я 0 немного увеличивается с уменьшением L пробел . Уменьшение L пробел менее 20 нм допускает более высокое туннелирование к Gate2, тем самым ухудшая состояние «0», таким образом, сокращая время удерживания.

Чтобы гарантировать, что Я 1 / Я 0 и время удерживания больше 10 2 и 2 с соответственно минимальное значение L g1 , L g2 , и L пробел рассматриваются как 200, 150 и 20 нм соответственно. Этот минимальный размер устройства немного меньше, чем в [17,18,19,20], как показано в таблице 3. Однако минимальный размер DGTFET DRAM по-прежнему больше, чем размер узла 1T1C DRAM размером 20 нм / 18 нм [31 ], что является неотъемлемым недостатком DGTFET DRAM. Но его преимущества, заключающиеся в отсутствии конденсатора, малой мощности и высоком RT, нельзя игнорировать с помощью оптимизации проектирования прокладок. Уменьшение размера DGTFET DRAM сверх 100 нм будет в центре нашей работы в будущем.

Выводы

В этой статье с помощью инструмента Silvaco-Atlas изучается оптимизация проектирования спейсеров для DGTFET DRAM. Прокладки на сторонах истока и стока оказывают основное влияние на производительность DGTFET DRAM. Увеличенное краевое электрическое поле от источника-спейсера с HfO 2 делает область истощения поверхности расширенной в туннельном переходе источника, что снижает ток считывания «1». Когда SiO 2 Если в прокладке стока используется диэлектрик, чем сильнее BTBT, тем больше дырок образуется при удерживании «0», что увеличивает рекомбинационный ток при считывании «0». Следовательно, оптимальная конструкция разделителя состоит в том, чтобы в разделителях стока и истока использовались диэлектрики с низким k и высоким k соответственно. Благодаря оптимизации конструкции спейсера DGTFET DRAM получает заметные преимущества - чрезвычайно низкий ток считывания «0» и более высокое время удерживания (10 с) по сравнению с другими подобными работами. Кроме того, анализ масштабируемости показывает, что минимальный размер устройства по-прежнему больше, чем у последнего 20-нм / 18-нм узла 1T1C DRAM. Этот присущий недостаток указывает на то, что уменьшение размера DGTFET DRAM сверх 100 нм будет в центре внимания нашей работы над DGTFET DRAM в будущем.

Сокращения

- DGTFET:

-

Полевой туннельный транзистор с двойным затвором

- DRAM:

-

Динамическая память с произвольным доступом

Наноматериалы

- Однопереходный транзистор (UJT)

- Идеи проектов на основе датчиков для студентов последних курсов инженерного факультета

- Принципы проектирования надежности для инженера-технолога

- Ученые IBM изобрели термометр для наномасштаба

- Значение облачного разделения файлов и управления файлами для 3D-печати

- Оптимизация высокоотражающей тонкой пленки для полноугольных микро-светодиодов

- Лучший уровень для оптимизации и организации умной фабрики

- Как найти индивидуальные инженерные решения, которые вам нужны

- Недостаток разнообразия может быть причиной растущего разрыва в отраслевых навыках

- Спасибо за воспоминания!