Двоичный сумматор

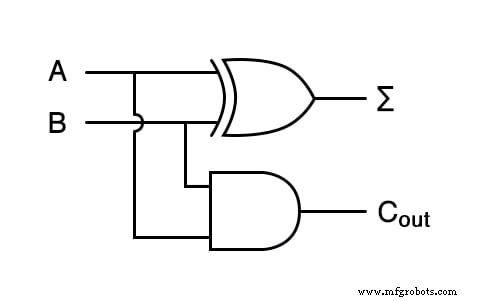

Предположим, мы хотим создать устройство, которое могло бы складывать два двоичных разряда вместе. Такое устройство известно как полусумматор, и его схема затвора выглядит так:

Символ Σ представляет собой "сумму" на выходе полусумматора, наименее значимый бит суммы (LSB). C вне представляет собой выход «переноса» полусумматора, старший значащий бит суммы (MSB).

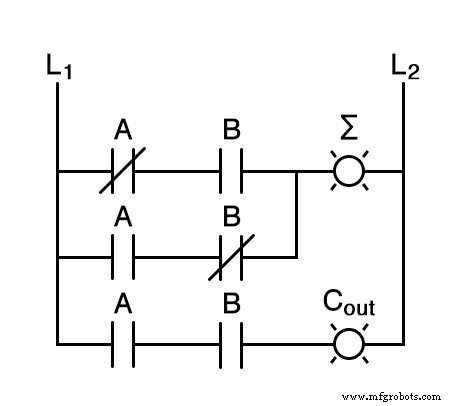

Если бы мы реализовали эту же функцию в релейной (релейной) логике, это выглядело бы так:

Любая схема способна складывать две двоичные цифры вместе. Математические «правила» сложения битов являются неотъемлемой частью аппаратной логики схем.

Если бы мы хотели выполнить другую арифметическую операцию с двоичными битами, такую как умножение, нам пришлось бы построить другую схему. Вышеупомянутые схемы будут выполнять только одну функцию:складывать два двоичных бита вместе. Чтобы заставить их делать что-то еще, потребовалось бы переподключение и, возможно, другие компоненты.

В этом смысле цифровые арифметические схемы мало чем отличаются от аналоговых арифметических схем (операционные усилители):они делают именно то, для чего они запрограммированы, не больше и не меньше. Однако мы не ограничены проектированием цифровых компьютерных схем таким образом.

Можно встроить математические «правила» для любой арифметической операции в виде цифровых данных, а не в жестких соединениях между вентилями. Результатом стала беспрецедентная гибкость в эксплуатации, что привело к появлению совершенно нового типа цифрового устройства: программируемого компьютера . .

Хотя эта глава ни в коем случае не является исчерпывающей, она дает уникальный и интересный взгляд на природу программируемых компьютерных устройств, начиная с двух устройств, которые часто упускаются из виду во вводных учебниках: справочные таблицы памяти и конечные автоматы .

СВЯЗАННЫЙ РАБОЧИЙ ЛИСТ:

- Рабочий лист двоичных математических схем

Промышленные технологии