Ключ к инновациям в материалах до 7 нм и выше

По мере того, как наша группа исследователей полупроводников в Олбани, штат Нью-Йорк, продолжает масштабировать технологию CMOS для будущих узлов - до 10 нм, 7 нм и выше - сопротивление канала транзистора, которое определяет ток и то, как мы подключаемся к нему, продолжает играть все более важную роль в общая производительность чипа. Таким образом, для обеспечения конкурентоспособности данной будущей полупроводниковой технологии разработка материалов канала для снижения сопротивления канала транзистора является критически важной областью исследования. Вот почему мы изучаем кремний-германий (SiGe) - элементы, необходимые для достижения преимуществ в области энергопотребления, о которых говорилось в прошлогоднем анонсе 7-нм чипа.

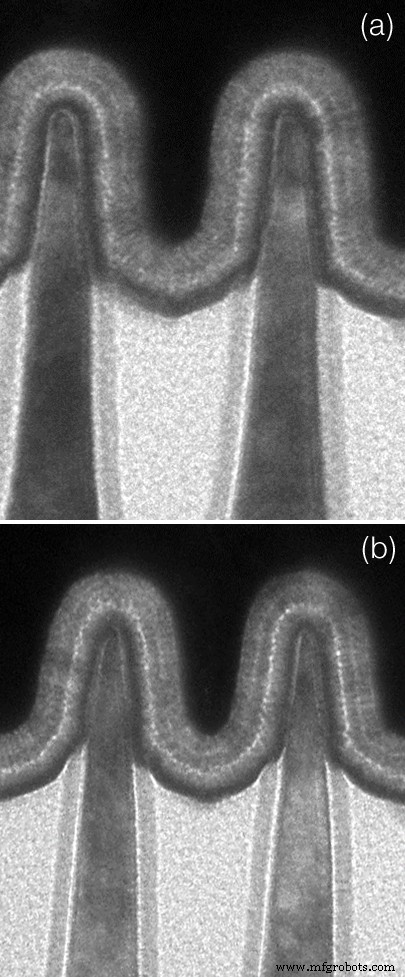

Симметричный Si Профили FinFET (a) и SiGe FinFET (b) на длине волны 10 нм, сделанные IBM Research в Нанотехнологическом комплексе SUNY Polytechnic в Олбани, штат Нью-Йорк. Это показывает, что SiGe Fin может обеспечивать лучшие электрические свойства, чем Si Fin.

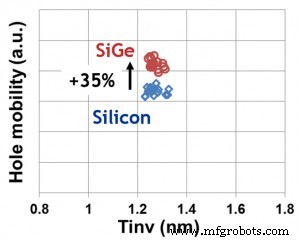

Сегодняшние 14-нм чипы на основе FinFET * используют только кремниевые каналы (кремний нестабилен за пределами этого масштаба). В качестве альтернативы, технология FinFET на основе SiGe продемонстрировала повышение производительности за счет основных правил 10-нанометровой технологии (отраслевые стандарты), предоставив элегантные решения для жизнеспособного варианта технологии CMOS. Одним из этих элегантных решений SiGe FinFET является возможность использования как маломощных, так и высокопроизводительных устройств на одном кристалле - без потери производительности или вариативности одного типа устройств по сравнению с другим.

Технология SiGe FinFET также обеспечивает превосходную электрическую надежность по сравнению с Si FinFET. И это приводит к более высокой стабильности производительности на уровне кристалла, чем Si FinFET на протяжении всего срока службы кристалла. Это означает, что идентичный процесс интеграции подходит как для разработки суперкомпьютеров, так и для мобильных устройств.

SiGe раздвигает границы масштабирования микросхемы, изменяя способ прохождения тока через канал транзистора. Оказывается, что, добавляя более крупные атомы германия к кристаллу, состоящему из более мелких атомов кремния, в кристалле возникает рассогласование решеток, вызывая напряжение в канале транзистора. Эта деформация позволяет пропускать через канал больше тока при более низких напряжениях. Таким образом, используя SiGe в качестве материала канала, мы можем наметить дорожную карту для меньших размеров, сохраняя при этом баланс между мощностью и производительностью.

SiGe для будущих узлов:решение проблем, связанных с производством 10- и 7-нм чипов

Сохранение деформации на протяжении всего процесса интеграции, а также контроль дефектов - две из основных технических проблем при производстве SiGe FinFET на узле 10 нм и ниже. Каналы транзистора могут потерять напряжение во время процессов термического отжига, которые активируют легирующие примеси и стабилизируют целостность транзистора; или во время процессов углубления истока / стока, которые образуют однородное соединение от верха ребра к низу ребра; или даже рисунок ребра в определенных конструкциях, который требует коротких ребер .

Контроль дефектов также имеет решающее значение при массовом производстве КМОП-технологий. Из-за несоответствия решеток между каналом SiGe и его кремниевой подложкой сложно поддерживать требуемый уровень дефектов технологичности по всей пластине. Но с нашим продвинутым эпитаксиальным (кристаллическим) управлением ростом, инновационной технологической интеграцией модуля Fin и проектированием источника / стока мы разработали решения, обеспечивающие деформацию канала на протяжении всего процесса интеграции, при этом сохраняя низкий уровень дефектности в наших 10- и 7-нанометровых испытаниях. узлов.

С этим всесторонним технико-экономическим обоснованием технологии SiGe FinFET при основных правилах 10-нм технологии мы теперь работаем с разработчиками и производителями микросхем над массовым производством технологии SiGe FinFET. Я ожидаю, что наша технология SiGe FinFET заменит кремниевый FinFET в следующем поколении узлов технологии CMOS для вычислительных целей, включая суперкомпьютеры и мобильные устройства. Их также можно использовать в приложениях «больше, чем Мур», например, в облачных и когнитивных вычислениях, где крайне желательны низкое энергопотребление и низкое энергопотребление, например в приложениях в облаке и когнитивных вычислениях.

Дополнительная литература

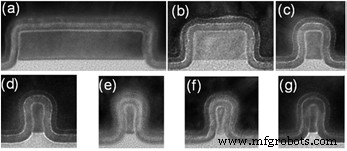

Поперечные разделы ребер и стопка ворот для ребер шириной от 87 нм (a) до 3 нм (g) для более высокого содержания Ge для SiGe Fin.

На симпозиуме IEEE в этом году по технологии СБИС (очень крупномасштабная интеграция) наши команды представили ряд новых устройств, материалов и инноваций в области интеграции, основанных на использовании SiGe с основными правилами 10-нм, а также в качестве пути к решению проблемы масштабирования. и проблемы производительности 7-нм тестового узла, который мы изготовили в прошлом году.

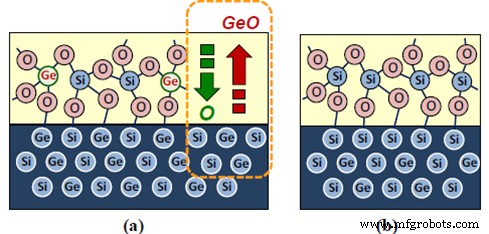

Наши презентации касались важнейших технических характеристик и фундаментальных инноваций в процессах контроля дефектов; инновации в стеке ворот и межфазном слое, подходящем для SiGe FIN; а также передовые методы контакта на платформе SiGe FinFET, о которых сообщается в исследовательском документе T2.2 на конференции VLSI. В исследовательском документе T4.3 описан изобретенный процесс селективного поглощения оксида германия для создания прочного межфазного слоя для канала SiGe.

Понятная мобильность преимущество SiGe Fin по сравнению с Si Fin, что приводит к увеличению производительности на уровне микросхемы.

На VLSI также было представлено наше исследование, проведенное доктором Пуйя Хашеми и посвященное расширению технологии SiGe FinFET для будущих узлов с более высокой производительностью. В исследовательской статье T9.3 мы сообщили о возможности достижения более высоких характеристик при более высоком содержании Ge и меньшей ширине ребер, а также о дальнейшем масштабировании стека затворов. Участники Симпозиума СБИС могут найти эти технические документы на сайте СБИС. Вы также можете присоединиться к их группе Linkedin для получения дополнительной информации.

T2.2: Технология FINFET с высокопроизводительным SiGe-каналом для 10 нм и выше

T4.3: Селективный GeO x -Очистка от межфазного слоя на Si 1-x Ge x Канал для высокой мобильности Si / Si 1-x Ge x Приложение CMOS

T9.3: Замена напряженных SiGe FinFET-транзисторов с высоким K / металлическим затвором и высоким содержанием Ge, с высокой подвижностью отверстий, отличным твердым покрытием и надежностью при агрессивном EOT ~ 7Å и уменьшенными размерами до ширины ребра менее 4 нм

T7.2: Контакты Ti и NiPt / Ti Liner Silicide для передовых технологий

Схема предлагаемый в изобретении процесс селективного поглощения GeOx (а) и межфазный слой без GeOx (b) с каналом SiGe.

* -FinFET относится к архитектуре транзистора, которая поднимает канал транзистора так, чтобы он выглядел как плавники)

Дечао Гуо (Dechao Guo) - научный сотрудник, главный изобретатель и руководитель отдела усовершенствованного проектирования и интеграции устройств в IBM Research.

Наноматериалы

- В облако бесконечности и дальше

- IBM на SPIE:семь достижений в области создания микросхем, превышающих 7 нм

- IoT Beyond PoC:изменение мышления

- Технология цифровых двойников:за рамками ракетостроения

- Машинное зрение - ключ к Индустрии 4.0 и IoT

- Технологическая корпорация штата Миссури запускает инициативу в области предпринимательства и инноваций в …

- Как Интернет вещей и промышленная автоматизация стимулируют инновации

- Сотрудничество имеет ключевое значение для передовых производственных и технологических (AMT) компаний Европ…

- AMRC внедряет инновации в технологии и экономику замкнутого цикла

- ABB Robotics:технологические инновации и исследования и разработки в области робототехники