Как создать вектор сигнала в VHDL:std_logic_vector

std_logic_vector тип может использоваться для создания сигнальных шин в VHDL. std_logic является наиболее часто используемым типом в VHDL, а std_logic_vector является его версией массива.

В то время как std_logic отлично подходит для моделирования значения, которое может передаваться по одному проводу, но не очень практично для реализации наборов проводов, идущих к компонентам или от них. std_logic_vector является составным типом, что означает, что это набор подэлементов. Сигналы или переменные std_logic_vector тип может содержать произвольное количество std_logic элементы.

Эта запись в блоге является частью серии учебных пособий по основам VHDL.

Синтаксис объявления std_logic_vector сигналов:signal <name> : std_logic_vector(<lsb> to <msb>) := <initial_value>;

илиsignal <name> : std_logic_vector(<msb> downto <lsb>) := <initial_value>;

где <name> это произвольное имя сигнала и <initial_value> является необязательным начальным значением. <lsb> — это индекс младшего значащего бита, а <msb> индекс старшего бита.

to или downto указывает направление диапазона шины, в основном его порядок байтов. Хотя оба варианта работают одинаково хорошо, разработчик VHDL чаще всего объявляет векторы с помощью downto. . Поэтому я рекомендую всегда использовать downto когда вы объявляете битовые векторы, чтобы избежать путаницы.

Код VHDL для объявления векторного сигнала, который может содержать байт:signal MySlv : std_logic_vector(7 downto 0);

Код VHDL для объявления векторного сигнала, который может содержать один бит:signal MySlv : std_logic_vector(0 downto 0);

Код VHDL для объявления векторного сигнала, который может содержать нулевые биты (пустой диапазон ):signal MySlv : std_logic_vector(-1 downto 0);

Упражнение

В этом видеоуроке мы узнаем, как объявить std_logic_vector сигналов и присвоить им начальные значения. Мы также узнаем, как перебирать биты в векторе с помощью цикла For-Loop для создания регистра сдвига. :

Окончательный код, который мы создали в этом руководстве:

library ieee;

use ieee.std_logic_1164.all;

entity T11_StdLogicVectorTb is

end entity;

architecture sim of T11_StdLogicVectorTb is

signal Slv1 : std_logic_vector(7 downto 0);

signal Slv2 : std_logic_vector(7 downto 0) := (others => '0');

signal Slv3 : std_logic_vector(7 downto 0) := (others => '1');

signal Slv4 : std_logic_vector(7 downto 0) := x"AA";

signal Slv5 : std_logic_vector(0 to 7) := "10101010";

signal Slv6 : std_logic_vector(7 downto 0) := "00000001";

begin

-- Shift register

process is

begin

wait for 10 ns;

for i in Slv6'left downto Slv6'right + 1 loop

Slv6(i) <= Slv6(i-1);

end loop;

Slv6(Slv6'right) <= Slv6(Slv6'left);

end process;

end architecture;

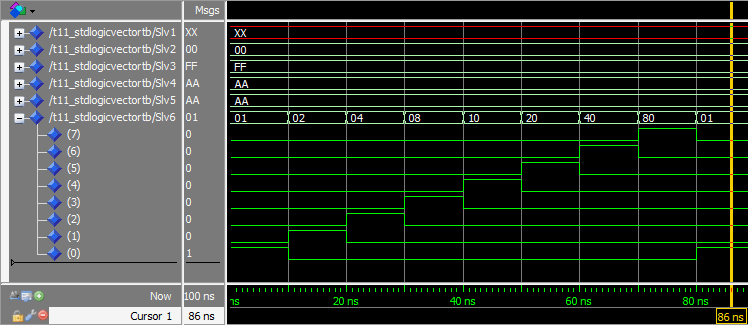

Окно сигнала в ModelSim после того, как мы нажали кнопку «Выполнить» и увеличили временную шкалу:

Анализ

В этом упражнении мы объявили шесть std_logic_vector шины, каждая из которых имеет длину восемь бит (один байт).

Сигнал Slv1 был объявлен без начального значения. Шина видна со значением XX на снимке экрана сигнала. Это связано с тем, что значение, отображаемое на шине, представлено в шестнадцатеричном формате, а XX указывает на нешестнадцатеричное значение. Но когда мы расширили шину в сигнале, мы увидели, что отдельные биты действительно были буквами U.

Сигнал Slv2 был объявлен с использованием начального значения всех 0. Вместо указания точного значения для каждого бита мы использовали (other => '0') вместо первоначального значения. Это известно как агрегат назначение. Важная часть заключается в том, что он установит все биты в векторе на то, что вы укажете, независимо от его длины.

Сигнал Slv3 был объявлен с использованием агрегатного присваивания, чтобы дать всем битам начальное значение 1. Мы можем видеть FF, отображаемый для этого сигнала в форме волны, которая является шестнадцатеричной для восьми единиц.

Сигнал Slv4 был объявлен с начальным значением, указанным в шестнадцатеричном формате, AA. Каждая шестнадцатеричная цифра имеет длину 4 бита, поэтому мы должны предоставить две цифры (AA) для нашего вектора длиной 8 бит.

Сигнал Slv5 объявляет точно такое же начальное значение, как Slv4 , но теперь мы указали его как двоичное значение 10101010. Из формы сигнала видно, что оба сигнала имеют шестнадцатеричное значение AA.

Сигнал Slv6 был объявлен с начальным значением всех нулей, кроме самого правого бита, который был '1' . Мы использовали процесс для создания сдвигового регистра от этого сигнала. Сдвиговый регистр, как следует из названия, сдвигает содержимое вектора на одну позицию влево каждые 10 наносекунд.

Наш процесс просыпается каждые 10 нс, и цикл For-Loop сдвигает все биты в векторе на одну позицию влево. Последний бит сдвигается обратно в первый индекс на Slv6(Slv6'right) <= Slv6(Slv6'left); утверждение. На осциллограмме мы видим '1' рябь по вектору.

Это визуализация того, как '1' распространяется через наш сдвиговый регистр:

С помощью 'left' и 'right атрибуты, мы сделали наш код более общим. Если мы изменим ширину Sig6 , процесс все равно будет работать. Хорошей практикой проектирования является использование атрибутов там, где это возможно, вместо жестко заданных значений.

Вам может быть интересно, есть ли еще атрибуты, которые вы можете использовать, и они есть. Я не буду больше говорить о них в этой серии руководств, поскольку считаю их расширенными функциями VHDL.

Вывод

- N-битные векторы должны быть объявлены с использованием

std_logic_vector(N-1 downto 0) - Вектор можно назначать целиком или к его битам можно обращаться по отдельности.

- Все биты в векторе можно обнулить с помощью агрегатного присваивания

(others => '0') - Код можно сделать более универсальным, используя такие атрибуты, как

'left. и'right

Пройдите базовый тест VHDL — часть 2 »

или

перейдите к следующему руководству »

VHDL

- Примеры преобразования VHDL

- Подписанный и неподписанный в VHDL

- Как создать список строк в VHDL

- Как создать управляемый Tcl тестовый стенд для модуля кодовой блокировки VHDL

- Как остановить симуляцию в тестовом стенде VHDL

- Как создать ШИМ-контроллер на VHDL

- Как генерировать случайные числа в VHDL

- Как создать кольцевой буфер FIFO в VHDL

- Как создать самопроверяющийся тестовый стенд

- Как создать связанный список в VHDL