Как создать параллельный оператор в VHDL

Параллельный оператор в VHDL — это назначение сигнала в архитектуре, но вне обычной конструкции процесса. Параллельный оператор также называется параллельным присваиванием или параллельным процессом.

Когда вы создаете параллельный оператор, вы фактически создаете процесс с определенными, четко определенными характеристиками. Параллельные операторы всегда эквивалентны процессу, использующему список чувствительности, где все сигналы справа от оператора присваивания сигнала находятся в списке чувствительности.

Эти процессы сокращенной записи полезны, когда вы хотите создать простую логику, которая приводит к назначению одного сигнала. Вместо того, чтобы вводить полную конструкцию процесса со списками чувствительности и всем остальным, вы можете просто назначить целевой сигнал непосредственно в архитектуре.

Эта запись в блоге является частью серии учебных пособий по основам VHDL.

При правильном использовании назначение кода будет довольно ясным. Нет необходимости создавать процесс для каждого бита, который вы хотите перевернуть.

Упражнение

В этом видео мы узнаем, как создать параллельный оператор:

Окончательный код, который мы создали в этом руководстве:

library ieee;

use ieee.std_logic_1164.all;

use ieee.numeric_std.all;

entity T13_ConcurrentProcsTb is

end entity;

architecture sim of T13_ConcurrentProcsTb is

signal Uns : unsigned(5 downto 0) := (others => '0');

signal Mul1 : unsigned(7 downto 0);

signal Mul2 : unsigned(7 downto 0);

signal Mul3 : unsigned(7 downto 0);

begin

process is

begin

Uns <= Uns + 1;

wait for 10 ns;

end process;

-- Process multiplying Uns by 4

process is

begin

Mul1 <= Uns & "00";

wait on Uns;

end process;

-- Equivalent process using sensitivity list

process(Uns) is

begin

Mul2 <= Uns & "00";

end process;

-- Equivalent process using a concurrent statement

Mul3 <= Uns & "00";

end architecture;

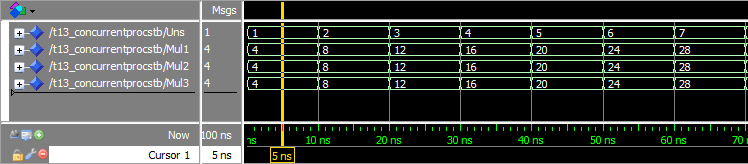

Окно сигнала в ModelSim после того, как мы нажали кнопку «Выполнить» и увеличили временную шкалу:

Анализ

Из формы волны видно, что Mul1 , Mul2 и Mul3 вести себя точно так же. Это связано с тем, что параллельный оператор и два созданных нами процесса эквивалентны.

Параллельный оператор работает так же, как процесс. Все сигналы справа от <= автоматически добавляются в список чувствительности. Это означает, что сигнал слева от <= будет обновляться всякий раз, когда изменяется один из оцениваемых сигналов.

В VHDL существует множество способов умножения чисел. В этом упражнении мы умножили Uns сигнал на 4, используя битовый сдвиг. Все наши сигналы имеют unsigned тип, что означает, что они интерпретируются числами. Добавление 0 справа от двоичного числа равносильно умножению его на 2.

Это иллюстрация того, что происходит с курсором на осциллограмме:

Вывод

- Параллельный оператор — это назначение сигнала непосредственно в области архитектуры.

- Параллельные операторы эквивалентны процессу со всеми оцениваемыми сигналами в списке конфиденциальности.

Перейти к следующему руководству »

VHDL

- Оператор процедуры — пример VHDL

- Как создать список строк в VHDL

- Как создать управляемый Tcl тестовый стенд для модуля кодовой блокировки VHDL

- Как остановить симуляцию в тестовом стенде VHDL

- Как создать ШИМ-контроллер на VHDL

- Как создать кольцевой буфер FIFO в VHDL

- Как создать самопроверяющийся тестовый стенд

- Как создать связанный список в VHDL

- Как использовать процедуру в процессе в VHDL

- Как использовать функцию в VHDL