Интерактивный тестовый стенд с использованием Tcl

Интерактивный испытательный стенд — это установка симулятора, при которой ввод данных в тестируемое устройство (ИУ) осуществляется оператором во время работы испытательного стенда. Чаще всего это будет означать, что вы вводите команды в консоли симулятора, чтобы предоставить тестируемому устройству стимул.

Хотя вы всегда должны создавать самопроверяющийся тестовый стенд, интерактивный тестовый стенд может быть хорошим дополнением. Легче проводить специальное тестирование с интерактивным тестовым стендом под рукой, чем менять код самопроверяющегося тестового стенда.

Часто в лаборатории вы обнаружите проблемы, которые захотите опробовать на тестовом стенде. С интерактивным тестовым стендом это может быть так же просто, как ввести входную последовательность, которая, как было замечено, воспроизвела нежелательное поведение в симуляторе.

Tcl взаимодействует с VHDL

Большинство симуляторов VHDL используют Tcl в качестве языка консоли. Симуляторы имеют набор команд, специфичных для конкретного поставщика, но хорошая новость заключается в том, что их можно рассматривать как любую другую команду Tcl. Вы можете использовать Tcl для создания сложных, в основном переносимых сценариев для управления и поддержки ваших тестовых стендов VHDL.

Изменение сигналов VHDL из Tcl

Для взаимодействия с VHDL нам нужно найти команду для изменения значения сигнала. В ModelSim это команда «force». Как указано в справочном документе по командам, краткий обзор команды:

force {<object_name> <value> [[@]<time_info>][, <value> [@]<time_info>]...

[-deposit | -drive | -freeze] [-cancel [@]<time_info>] [-repeat [@]<time_info>] Переключатель, который вы хотите использовать, — это флаг «-deposit». Это мгновенно изменяет значение сигнала VHDL, но позволяет другому драйверу VHDL или Tcl изменить его на что-то другое позднее.

Без учета параметров, которые мы не используем, упрощенный синопсис выглядит так:

force -deposit <signal_name> <value>

Триггер VHDL

Теперь, когда мы знаем, как управлять сигналами VHDL из Tcl, нам нужно создать какой-то процесс-приемник в нашем тестовом стенде VHDL. В приведенном ниже коде показан минимальный пример такого тестового стенда.

library ieee;

use ieee.std_logic_1164.all;

use ieee.numeric_std.all;

entity interactive is

end interactive;

architecture sim of interactive is

-- Controlled by Tcl

signal trigger : std_logic := '0';

begin

process is

begin

wait until trigger = '1';

report "Triggered!";

end process;

end architecture;

Процесс проснется, когда trigger сигнал меняется с чего-то на '1' . Он напечатает «Триггер!» в консоль, когда это происходит, что позволяет нам протестировать концепцию управления процессами VHDL из Tcl.

Я сделал только что это консоль ModelSim. Выданные команды, а также вывод можно просмотреть в расшифровке ниже.

VSIM 1> run 10 ns; VSIM 2> force -deposit /trigger '1' VSIM 3> run 0 ns; # ** Note: Triggered! # Time: 10 ns Iteration: 0 Instance: /interactive VSIM 4> force -deposit /trigger '0' VSIM 5> run 10 ns;

Я запустил тестовый стенд на 10 наносекунд после запуска симуляции.

Затем я заставил trigger сигнал на '1' . В следующей строке я жду 0 наносекунд. Целью этого является создание дельта-цикла. Я хочу, чтобы процесс запускался, но я не хочу, чтобы проходило время моделирования.

Наконец, я форсирую trigger сигнал обратно на '0' прежде чем продолжить тестирование.

Мы видим, что процесс VHDL проснулся после строки «run 0 ns» и распечатал «Triggered!» в консоль.

Чтение значений сигнала VHDL в tcl

Чтобы прочитать значения сигналов в ModelSim, вы можете использовать команду «исследовать». Мы можем, например, прочитать значение trigger сигнал с помощью этой команды в консоли ModelSim:

VSIM 6> examine /trigger # 0

Вы хотели бы присвоить значение переменной Tcl при использовании «исследовать» в сценарии. Давайте попробуем это в консоли ModelSim:

VSIM 7> set triggerVal [examine /trigger] # 0

Затем мы можем, например, распечатать переменную с помощью команды Tcl «puts»:

VSIM 8> puts "triggerVal: $triggerVal" # triggerVal: 0

Остановка симулятора после каждого теста

Самый простой способ запустить тест достаточно долго, чтобы тестируемое устройство среагировало, — это просто запустить симулятор на фиксированное значение времени. Например, если тестируемое устройство должно среагировать после двух тактовых циклов, а тактовый период равен 10 наносекундам, мы должны использовать команду «run 20 ns» в нашем скрипте Tcl.

Если DUT не имеет фиксированного времени реакции, можно использовать утверждение VHDL для остановки моделирования и передачи управления функции обратного вызова Tcl. В ModelSim это означало бы установку точки останова из вашего скрипта Tcl с помощью команды «когда»:

when [[-fast] [-id <id#>] [-label <label>] {<when_condition_expression>} {<command>}] Вы также должны определить функцию обратного вызова onBreak в Tcl, которая будет запускаться при достижении точки останова. Функция onBreak указана в справочнике по командам ModelSim.

Недостатки тестирования на основе Tcl

Существуют недостатки использования тестовых стендов, которые в значительной степени зависят от сценариев Tcl. Наиболее очевидными из них являются проблемы со скоростью и переносимостью.

Управляемые Tcl тестовые стенды работают, запуская и останавливая симулятор несколько раз для взаимодействия с кодом VHDL. Запуск и остановка симуляции для выполнения промежуточной функции Tcl занимает больше времени, чем непрерывная работа тестового стенда VHDL. Хотя Tcl является интерпретируемым языком, VHDL компилируется в симуляторе и работает намного быстрее, чем Tcl.

В то время как Tcl переносим на другие симуляторы, специфичные для симулятора команды, которые вам придется использовать, не являются переносимыми. Даже если вы найдете аналогичные команды в другом симуляторе, они могут работать по-другому. Поставщики симуляторов составляют собственный набор правил для поддерживаемых ими команд. Таким образом, тестовый стенд на основе Tcl следует считать менее переносимым, чем тестовый стенд на чистом VHDL.

Новый курс VHDL и FPGA

* Я создаю новый курс по VHDL и FPGA, который будет подробно изучать испытательные стенды. Вы узнаете, как создать дизайн FPGA с нуля. После прохождения курса вы узнаете, как создавать тестовые стенды с самопроверкой и как повторно использовать код для создания интерактивного тестового стенда.

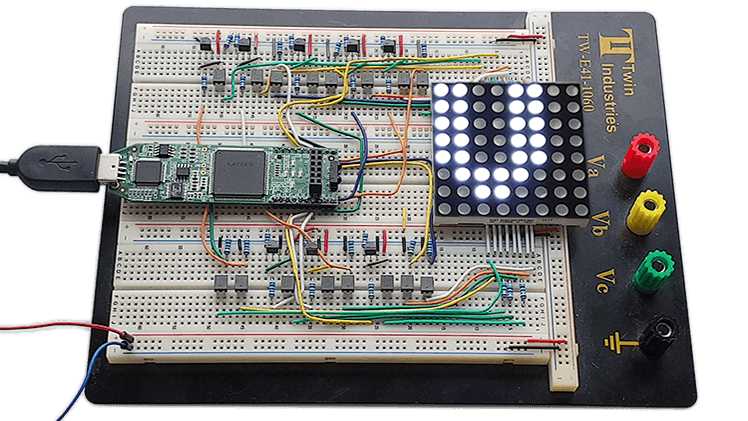

* Обновлено 12 октября 2020 г.: Я закончил курс. Нажмите на изображение ниже, чтобы узнать больше.

Продукт, который мы создадим, представляет собой модуль контроллера светодиодов с точечной матрицей. Мы будем использовать плату разработки Lattice iCEstick за 49 долларов. В конце реализуем дизайн на макетной плате. Вы сможете печатать на клавиатуре своего компьютера, а символы будут отображаться на матричном светодиодном экране, управляемом ПЛИС.

Узнайте больше о курсе Dot Matrix VHDL и FPGA здесь!

Открывается:

Подлежит решению .

VHDL

- Учебное пособие — Введение в VHDL

- Примеры преобразования VHDL

- Оператор процедуры — пример VHDL

- Записи — пример VHDL

- Подписанный и неподписанный в VHDL

- С# с использованием

- Как создать список строк в VHDL

- Как создать самопроверяющийся тестовый стенд

- Интерактивный лазерный проектор с использованием датчиков Zigbee

- Использование фрезерного станка в качестве токарного станка