Надежное и устойчивое к защелкам устройство LVTSCR со встроенным PMOSFET для защиты от электростатического разряда в процессе 28-нм CMOS

Аннотация

Предполагается, что низковольтный выпрямитель с кремниевым управлением (LVTSCR) обеспечит защиту от электростатического разряда (ESD) для низковольтной интегральной схемы. Однако он обычно уязвим для эффекта фиксации из-за чрезвычайно низкого напряжения удержания. В этой статье был предложен новый LVTSCR со встроенным дополнительным полевым МОП-транзистором p-типа под названием EP-LVTSCR, который был проверен на основе 28-нм CMOS-технологии. Предлагаемое устройство имеет более низкое напряжение срабатывания ~ 6,2 В и значительно более высокое удерживающее напряжение ~ 5,5 В с уменьшением тока отказа только на 23% при импульсном испытании линии передачи. Также показано, что EP-LVTSCR работает с более низким сопротивлением включения ~ 1,8 Ом, а также с надежным током утечки ~ 1,8 нА, измеренным при 3,63 В, что делает его пригодным для защиты от электростатических разрядов в CMOS 2,5 В / 3,3 В процессы. Кроме того, механизм срабатывания и характеристики проводимости предлагаемого устройства были исследованы и продемонстрированы с помощью моделирования TCAD.

Фон

В связи с постоянной миниатюризацией размеров элементов полупроводниковых устройств повреждение интегральных схем (IC), вызванное электростатическим разрядом (ESD), стало более серьезной проблемой. Более того, стоимость изготовления устройства защиты от электростатического разряда резко возросла из-за передового технологического процесса [1]. Таким образом, конструкции устройств защиты от электростатического разряда с высокой эффективностью и надежностью имеют большое значение.

Было проверено, что устройство с кремниевым выпрямителем (SCR) выдерживает высокий ток электростатического разряда при небольших размерах устройства из-за сильного положительного эффекта обратной связи в его паразитных транзисторах с биполярным переходом [2]. Но SCR обычно имеет высокое напряжение срабатывания ( V t1 ), которое превышает напряжение пробоя оксида затвора входного каскада в наноразмерной КМОП-технологии. Чтобы уменьшить V t1 SCR, модифицированный боковой SCR (MLSCR) был зарегистрирован для входной защиты от электростатического разряда путем вставки сильно легированного n + или p + области через границу n-ямы и p-ямы [3, 4]. Но напряжение срабатывания MLSCR все равно больше, чем напряжения пробоя выходных транзисторов в выходном буфере CMOS. Следовательно, он не может обеспечить эффективную выходную защиту от электростатического разряда в одиночку.

Для эффективной защиты выходного буфера CMOS был предложен триггер с низким напряжением (LVTSCR) путем вставки устройства NMOS с коротким каналом (PMOS) в традиционный SCR для реализации гораздо более низкого напряжения триггера [5,6,7] , что эквивалентно запускающему напряжению мгновенного возврата вставленного устройства NMOS (PMOS). Однако, как и традиционные устройства SCR и MLSCR, LVTSCR также подвержен риску защелкивания из-за чрезвычайно низкого напряжения удержания (V h ) около 2 В [8]. Такой эффект фиксации приведет к неисправности во время нормальной работы и постоянному высокому току, разрушающему ИС [9].

Есть несколько возможных методов улучшения V h LVTSCR [10,11,12,13,14,15]. Наиболее распространенным решением является расширение базовой области паразитных транзисторов с биполярным переходом (BJT) SCR для снижения эффективности инжекции их переходов эмиттер-база [10]. Принятие этого решения увеличит не только площадь расположения устройства, но и сопротивление включения ( R на ) тоже должно быть, что в дальнейшем приведет к резкому снижению его тока отказа ( I t2 ). Затем был предложен оптимизированный метод путем вставки области с плавающими лунками в LVTSCR с меньшими потерями на I t2 [11], но он также работает с большим R на ведет к чрезмерному напряжению проводимости, которое превышает напряжение пробоя оксида затвора, по сравнению с небольшим током, что снижает его эффективный ток защиты от электростатического разряда. Метод добавления дополнительных слоев N-LDD / P-HALO в LVTSCR также может повысить V h [12], в то время как такие устройства совместимы только для конкретного процесса и не могут широко использоваться в обычных процессах CMOS. Более того, LVTSCR (GGSCR), запускаемый через NMOS, был описан в [13], что увеличивает V h путем направления стока встроенного NMOS к аноду, но это может привести к повреждению встроенного NMOS до проведения SCR при слабом токе. В последнее время составные структуры LVTSCR с низким V t1 а также высокий V h были продемонстрированы в [14, 15]. Эти составные структуры разработаны с учетом высокой сложности и требований к площади, что ограничивает их применение в передовой КМОП-технологии с учетом затрат на проектирование. Следовательно, надежное, эффективное по площади и устойчивое к фиксации устройство защиты от электростатического разряда крайне желательно для усовершенствованной защиты технологического процесса от электростатического разряда.

В этой статье предлагается новая структура LVTSCR со встроенным PMOS-транзистором (EP-LVTSCR) для приложений с напряжением питания 2,5 В / 3,3 В. Предлагаемое устройство было изготовлено по технологии КМОП с длиной волны 28 нм, а его электрические характеристики проверены путем измерения импульса линии передачи (TLP). Физические механизмы предлагаемого устройства исследуются с помощью технологии компьютерного моделирования (TCAD). В результате предлагаемая структура обладает более высоким напряжением удержания, более низким напряжением срабатывания при более низком R на , и лишь небольшое уменьшение I t2 без дополнительных шагов процесса.

Методы

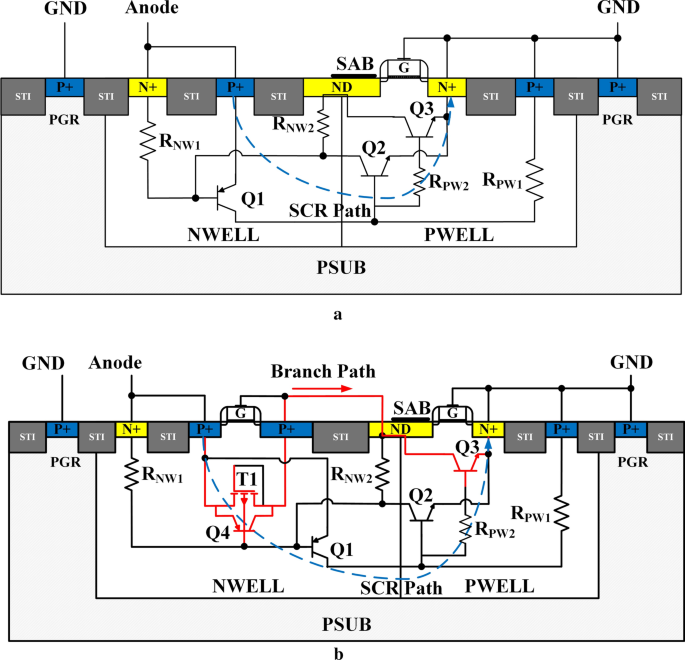

В этой статье изучались стандартный LVTSCR и предлагаемый EP-LVTSCR. Схематические виды в разрезе обычных LVTSCR и EP-LVTSCR показаны на рис. 1a, b, соответственно, тогда как их эквивалентные схемы изображены в структурах с паразитными транзисторами и резисторами в колодцах. В обоих устройствах слои силицидного блока (SAB) размещаются поверх частичной области ND, что вызывает балластные сопротивления, предотвращая образование силицидных слоев [16, 17]. В обычном LVTSCR транзистор NMOS вставлен в PWELL с настройкой стока (ND) через NWELL и PWELL, в то время как его исток и затвор соединены с землей (GND) вместе, что можно увидеть на рис. 1a. Во время стресса ESD будут постепенно включаться паразитные латеральные BJT p-n-p (Q1) и паразитные латеральные BJT n-p-n (Q2 и Q3). В таком состоянии транзисторы Q1 и Q2 соединены, образуя путь проводимости SCR, который будет преобладать над током разряда, где путь проводимости SCR обозначен пунктирной линией.

Вид в разрезе a обычный LVTSCR и b предлагаемый EP-LVTSCR

По сравнению с обычным LVTSCR, EP-LVTSCR имеет дополнительный транзистор PMOS (T1), встроенный в NWELL, поскольку его затвор и сток соединены с ND с помощью металла, который показан на рис. 1b. Когда на анод EP-LVTSCR подается импульс ESD, диод N + / NWELL / N + / PWELL / P + с обратным смещением будет проводить первым, если напряжение срабатывания выше, чем напряжение пробоя N + / PWELL. Затем дырки / электроны, генерируемые эффектом лавинного умножителя, будут течь к катоду / аноду, тем самым увеличивая плотность тока в NWELL / PWELL, и дополнительно повышая потенциал падения на NWELL / PWELL. После полного падения напряжения на R NW1 и R NW2 , что эквивалентно падению напряжения между истоком и затвором (- V GS ) T1, превышает его пороговое напряжение ( V th ) около 0,9 В, Т1 будет включен. Впоследствии паразитные боковые n – p – n транзисторы Q2 и Q3 будут срабатывать в зависимости от проводимости их переходов эмиттер – база. Замечено, что проведение T1 снизит R на через NWELL, и, таким образом, Q2 и Q3 могут срабатывать при более низких напряжениях. Поскольку ток продолжает расти, падение напряжения на R NW1 возрастает примерно до 0,7 В и включает Q1 и паразитный боковой p – n – p транзистор PMOS (Q4). Наконец, путь SCR включается против проводящего пути ответвления.

Несколько отчетов продемонстрировали, что удерживающее напряжение SCR в основном определяется разностью потенциалов в области истощения NWELL / PWELL V dep [18,19,20], что обратно пропорционально неосновным носителям (электронам / дыркам), инжектированным в обедненную область. В то время как путь ответвления EP-LVTSCR может извлекать дырки / электроны, инжектированные в область истощения из пути SCR, тем самым повышая V h EP-LVTSCR.

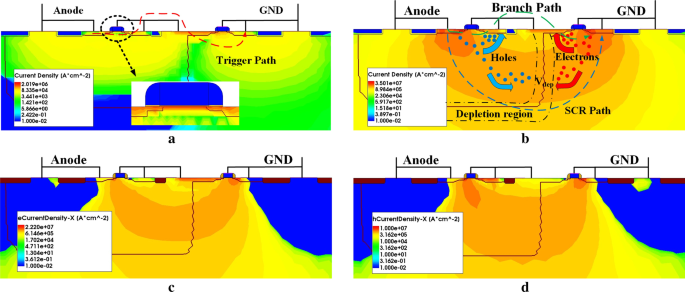

Чтобы дополнительно продемонстрировать физический механизм EP-LVTSCR, было выполнено моделирование TCAD, в котором были интегрированы физические модели, такие как подвижность, рекомбинация, термодинамика и эффективная собственная плотность, а также математические методы, такие как экстраполяция, RelErrcontrol и постоянный ток. вычисления были использованы. Моделирование тока электростатического разряда импульсами 1,2 А с временем нарастания 10 нс применялось к анодам EP-LVTSCR и обычного LVTSCR, соответственно, где подложка устройств рассматривалась как единственный теплоотвод, а температура окружающей среды была установлена равной 300 ° C. К.

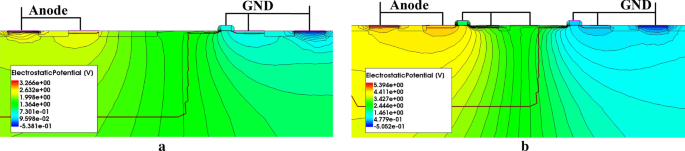

Результаты моделирования распределений полной плотности тока EP-LVTSCR при 500 пс и 5 нс показаны на рис. 2a, b, соответственно. При 500 пс распределение плотности тока концентрируется на транзисторах T1 и Q2, что указывает на то, что последовательность T1 / Q2 включена в качестве триггерного пути, показанного на рис. 2a. Когда время увеличивается до 5 нс, как путь SCR, так и путь ответвления прошли, как можно наблюдать на рис. 2b. В это время часть дырок / электронов, генерируемых P + / N +, извлекается из NWELL / PWELL, чтобы течь по пути ответвления, что иллюстрируется горизонтальными дырками и плотностью тока электронов в предлагаемой структуре, показанной на рис. 2c, d. . Далее, на рис. 3a, b сравниваются распределения электростатического потенциала обычных LVTSCR и EP-LVTSCR при 5 нс. Очевидно, потенциальный пик внутри EP-LVTSCR выше. Эти результаты моделирования являются прямым доказательством сделанного выше предположения о более высоком удерживающем напряжении EP-LVTSCR, возникающем в результате ветвления, показанного на рис. 1b.

Имитация TCAD a полное распределение плотности тока при t =500 пс, b общее распределение плотности тока при 5 нс, c горизонтальное распределение плотности тока электронов при 5 нс и d распределение плотности тока в горизонтальных отверстиях при 5 нс предлагаемого EP-LVTSCR при напряжении 1,2A-TLP

Распределение электростатического потенциала a , смоделированное с помощью TCAD предлагаемые EP-LVTSCR и b обычный LVTSCR в t =5 нс при напряжении 1,2A-TLP

Результаты и обсуждение

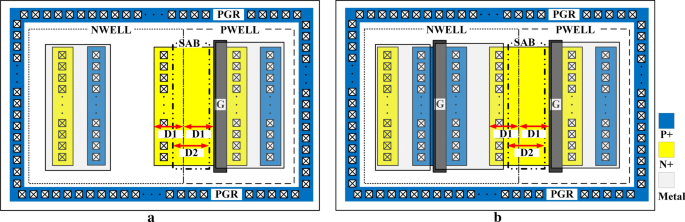

Обычные LVTSCR и EP-LVTSCR реализованы в 28-нм логическом КМОП-процессе 2,5 В / 3,3 В с той же шириной 40 мкм, и их топология компоновки показана на рис. 4a, b, соответственно. Чтобы избежать паразитных эффектов, связанных с подложкой, в обеих структурах используются защитные кольца P-типа (PGR), и каждый PGR подключен к GND [21]. Центральная ось ND выровнена с соединением NWELL / PWELL, а параметр D1 используется для описания половины длины ND, а D2 - это длина области SAB.

Топологии компоновки a обычный LVTSCR и b предлагаемый EP-LVTSCR

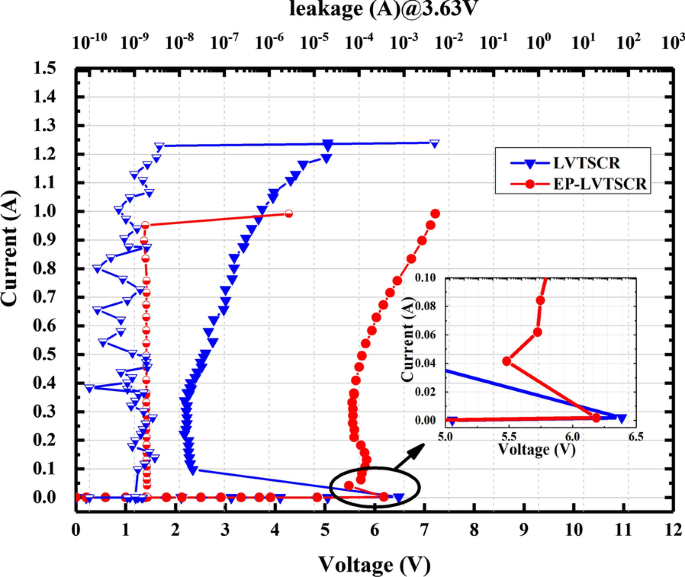

Характеристики ESD обычных LVTSCR и EP-LVTSCR измерялись с помощью тестера Hanwa TED-T5000 TLP с временем нарастания 10 нс и шириной импульса 100 нс, а токи утечки измерялись при смещении постоянного напряжения 3,63 В (1,1 * VDD) после каждого Стресс TLP. Измеренные ВАХ TLP и характеристики утечки EP-LVTSCR и LVTSCR показаны на рис. 5. Судя по всему, EP-LVTSCR имеет более высокое значение V h составляет 5,49 В по сравнению с обычным LVTSCR, равным 2,18 В. Хотя EP-LVTSCR значительно улучшает удерживающее напряжение, его I t2 просто уменьшился примерно на 0,29 А, что выгодно от ассистента пути тока ответвления. Кроме того, EP-LVTSCR также выполняет V t1 уменьшается с 6,49 до 6,18 В. Для вывода 2,5 В или 3,3 В в процессах 28-нм CMOS расчетное окно ESD находится в диапазоне от 3,63 до 9,4 В с учетом 10% запаса прочности. Таким образом, предлагаемый EP-LVTSCR можно использовать в качестве действительного решения защиты от электростатического разряда для портов ввода-вывода 2,5 В / 3,3 В, преодолев проблему фиксации в традиционной структуре типа LVTSCR.

Измеренные вольт-амперные характеристики TLP и токи утечки EP-LVTSCR и обычного LVTSCR с одинаковой площадью кристалла

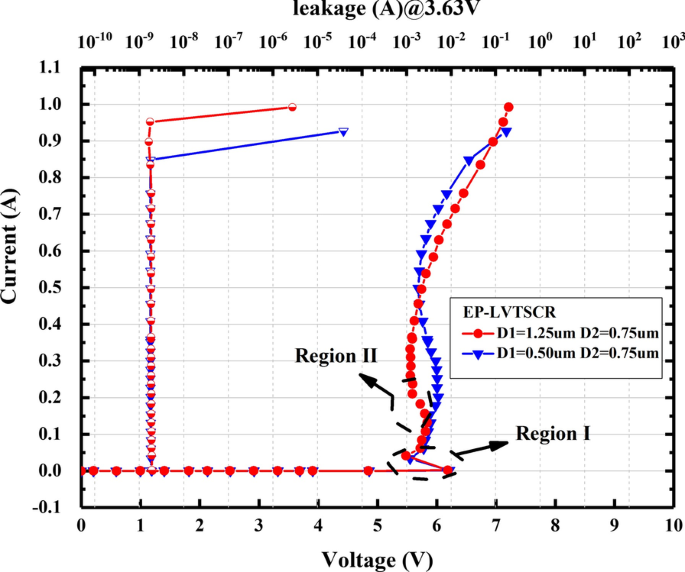

В этой статье электрические характеристики предлагаемой защиты от электростатического разряда были оптимизированы путем изменения проектных переменных D1 и D2. На рисунке 6 показаны результаты измерения TLP EP-LVTSCR с двумя разными D1. Замечено, что на ВАХ EP-LVTSCR показаны две области возврата из-за эффектов мульти-триггера во время включения устройств. Первая область мгновенного возврата I предполагает прохождение пути срабатывания триггера, которое показано на фиг. 2a, в то время как второе мгновенное возвращение области II индуцируется включением пути триггера. Когда D1 уменьшается с 1,25 до 0,5 мкм, I t2 уменьшается примерно на 0,1 А, а ток удержания во втором Snapback увеличивается примерно на 0,17 А. Это связано с тем, что сопротивление скважины R NW2 и R PW2 (Рис. 1) уменьшаются с уменьшением D1, следовательно, требуется больший ток для запуска и поддержания проведения SCR.

Измеренные ВАП I – V и токи утечки EP-LVTSCR с двумя разными D1

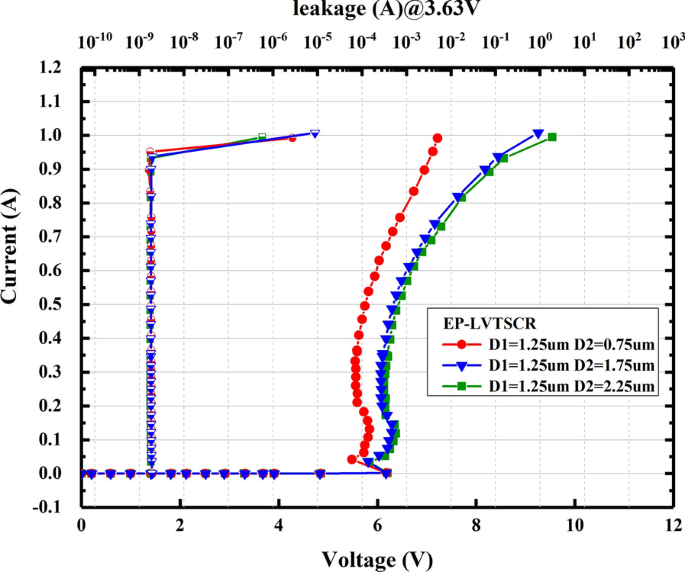

На рисунке 7 показаны результаты TLP I – V EP-LVTSCR с тремя различными D2. Когда D2 увеличивается с 0,75 до 2,25 мкм, балластное сопротивление ND постепенно увеличивается, что приводит к увеличению сопротивления пути ответвления и дальнейшему увеличению R на , что можно наблюдать по изменению наклона кривых ВАХ на рис. 7. В результате V h повышается с 5,5 до 5,8 В с увеличением D2 и без значительных изменений I t2 .

Измеренные ВАП I – V и токи утечки EP-LVTSCR с тремя различными D2

Выводы

Усовершенствованное устройство ESD под названием EP-LVTSCR было разработано и изготовлено по 28-нм технологии CMOS. Механизмы предлагаемых устройств были также продемонстрированы с помощью моделирования TCAD. По сравнению с обычным LVTSCR предлагаемый EP-LVTSCR имеет более низкое напряжение срабатывания 6,2 В и значительно более высокое напряжение удержания 5,5 В из-за улучшенного механизма запуска и эффекта проводимости ответвления. С таким большим увеличением V h ток отказа EP-LVTSCR снизился только примерно на 20%. Кроме того, предлагаемая структура работает с более низким сопротивлением при включении, а также с надежным током утечки около 2 нА при напряжении 3,63 В, поэтому она хорошо подходит для защиты контактов ввода / вывода 2,5 В / 3,3 В. Кроме того, ожидается, что EP-LVTSCR обеспечат защиту от электростатического разряда в цепях питания 5 В с выгодой за счет их регулируемых характеристик удерживающего напряжения.

Доступность данных и материалов

Все данные, полученные или проанализированные в ходе этого исследования, включены в эту опубликованную статью.

Сокращения

- ESD:

-

Электростатический разряд

- SCR:

-

Выпрямитель с кремниевым управлением

- MLSCR:

-

Модифицированный боковой SCR

- LVTSCR:

-

Стабилизатор низкого напряжения

- CMOS:

-

Дополнительный металлооксидный полупроводник

- IC:

-

Интегральные схемы

- V t1 :

-

Напряжение срабатывания

- V h :

-

Напряжение удержания

- BJT:

-

Биполярные переходные транзисторы

- R на :

-

Сопротивление включения

- I t2 :

-

Ток отказа

- TLP:

-

Линия передачи импульсов

- TCAD:

-

Технология автоматизированного проектирования

- SAB:

-

Силицидный блок

- V th :

-

Пороговое напряжение

- DC:

-

Постоянный ток

Наноматериалы

- Краткое описание технологии ИС для микроконтроллеров и встроенных систем

- Maxim:двойной приемопередатчик IO-Link с регулятором DC-DC и защитой от перенапряжения

- Встроенный дизайн с FPGA:процесс разработки

- TRS-STAR:надежные и безвентиляторные встраиваемые системы от avalue

- Разработка процесса нанесения покрытия погружением и оптимизация производительности для электрохромных ус…

- Интегрированная RRAM 4T SRAM с самоторможением резистивной коммутационной нагрузки с помощью логического процес…

- Новая кластерная микроструктура наноконусов с антиотражающими и супергидрофобными свойствами для фотоэлек…

- Многофункциональное устройство с переключаемыми функциями преобразования поглощения и поляризации в тераг…

- Автоматизация и кибербезопасность:полная защита для клиентов

- Материалы и дизайн печатных плат для высокого напряжения