Решения CXL 2.0 / PCIe 5.0 устраняют узкие места гетерогенных вычислений и данных

Полупроводниковый стартап Fabless Astera Labs анонсировал новые специализированные решения для подключения CXL 2.0 и PCIe 5.0, которые открывают доступ к гетерогенным вычислительным архитектурам и решают рабочие нагрузки, чувствительные к задержкам, в центре обработки данных. Компания заявила, что целью этих новых решений является устранение узких мест в производительности системы в приложениях, ориентированных на данные.

Распространение данных и внедрение специализированных рабочих нагрузок, таких как искусственный интеллект (AI) и машинное обучение (ML), требуют, чтобы специально разработанные ускорители работали бок о бок с процессорами общего назначения на одной материнской плате или в одной стойке, в то время как разделение общего пространства памяти. Межсоединение CXL 2.0 является ключом к реализации таких согласованных топологий системы кэширования.

Первым продуктом в новом портфеле Astera Labs является портфель интеллектуальных устройств восстановления времени Aries Compute Express Link (CXL 2.0) (PT5161LX, PT5081LX) для подключения CXL.io с малой задержкой, который активно тестируется для стратегических клиентов. Генеральный директор компании Джитендра Мохан сказал:«Благодаря нашему расширению экосистемы CXL, Astera Labs делает еще один гигантский скачок в предоставлении специализированных решений, открывающих доступ к сложным разнородным топологиям вычислений и составных систем дезагрегации».

Спецификация CXL 2.0 была выпущена консорциумом CXL в ноябре 2020 года. CXL - это открытое межсоединение отраслевого стандарта, предлагающее когерентность и семантику памяти с использованием высокой пропускной способности и связи с малой задержкой между хост-процессором и такими устройствами, как ускорители, буферы памяти и интеллектуальные устройства. Устройства ввода-вывода. Спецификация CXL 2.0 добавляет поддержку переключения для разветвления для подключения к большему количеству устройств; объединение памяти для повышения эффективности использования памяти и предоставления объема памяти по запросу; и поддержка постоянной памяти. Все это при сохранении инвестиций в промышленность за счет поддержки полной обратной совместимости с CXL 1.1 и 1.0.

Президент Консорциума CXL Барри МакОлифф сказал:«Будучи одним из первых членов Консорциума CXL, Astera Labs внесла свой вклад в развитие стандарта CXL. Приятно видеть, как на рынке появилась первая реализация микросхемы CXL для поддержки быстрорастущей экосистемы CXL ».

Новые решения PCIe 5.0 в сотрудничестве с Intel

Astera Labs также объявила о доступности нового режима с низкой задержкой в своем портфеле интеллектуальных ретаймеров Aries для подключения PCIe с масштабируемыми процессорами Intel Xeon. Эта разработка явилась результатом тесного сотрудничества с корпорацией Intel для дальнейшего уменьшения задержки в каналах PCIe до менее 10 нс и повышения производительности в рабочих нагрузках, ориентированных на данные. Astera Labs заявила, что это первый поставщик, продемонстрировавший надежную совместимость PCIe 5.0 с процессорами Intel Xeon Scalable под кодовым названием Sapphire Rapids.

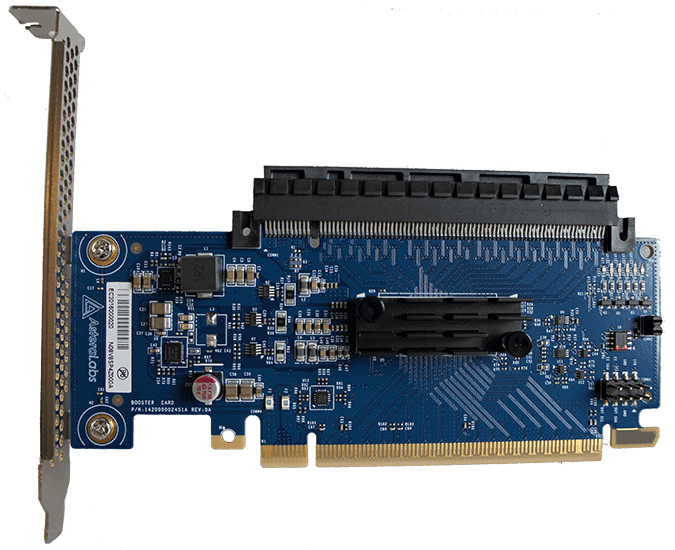

Одновременно с этим была выпущена новая plug-and-play карта расширения Smart retimer для приложений PCIe / CXL под названием Equinox. Карта и соответствующая специализированная прошивка, также разработанная в сотрудничестве с Intel, упростят разработку систем с поддержкой PCIe 5.0 с новейшими процессорами Intel Xeon Scalable. Это представляет собой переход Astera Labs к предложению простых в использовании плат plug-and-play для быстрого внедрения сложных топологий системы.

«PCIe Gen5 и CXL являются основополагающими технологиями для гетерогенных вычислительных нагрузок и архитектур центров обработки данных сегодня и завтра», - сказал Зейн Болл, корпоративный вице-президент и генеральный менеджер по проектированию и архитектуре центров обработки данных в Intel. «Корпорация Intel сотрудничает с лидерами экосистемы, такими как Astera Labs, для значительного уменьшения задержки при соединении PCIe и CXL на будущей платформе Intel Xeon Scalable под кодовым названием Sapphire Rapids и дополнительных платформах».

Связанное содержание:

- Повторная синхронизация USB4 через USB-C

- Создание высокопроизводительных межсоединений с использованием нескольких поколений PCIe.

- Xilinx нацелена на разгрузку центра обработки данных с помощью «компонуемого» оборудования.

- Как пограничные суперкомпьютеры преобразуют огромный поток данных

Встроенный

- Юридические проблемы в облачных вычислениях и их решения

- МОДУЛЬ ДАННЫХ:ориентированные на клиента решения для цифровых вывесок, представленные на ISE

- Микрочип:тактовые буферы соответствуют стандартам DB2000Q / QL плюс спецификации PCIe Gen 4 и 5 с низким уровнем джитте…

- Apacer:твердотельные накопители PCIe NVMe Gen3, следующий логический шаг для промышленного хранилища

- Swissbit:аппаратные решения безопасности для защиты данных и устройств

- TECHWAY:Платформа Kintex-7 FPGA PCIe для повышения скорости передачи данных с помощью 12 каналов HSS

- Стратегия армии и решения по техническому обслуживанию по состоянию

- Преимущества адаптации решений IIoT и анализа данных для EHS

- Борьба с наводнениями в городских районах с помощью сетевых решений IoT

- Как Интернет вещей трансформирует цепочку поставок:Часть 2, Будущие решения