Регистры сдвига:последовательный вход, последовательный выход

Регистры сдвига с последовательным входом и выходом задерживают данные на один такт для каждого этапа.

Они будут хранить немного данных для каждого регистра. Сдвиговый регистр с последовательным входом и выходом может иметь длину от 1 до 64 бит, а в случае каскадного подключения регистров или пакетов - больше.

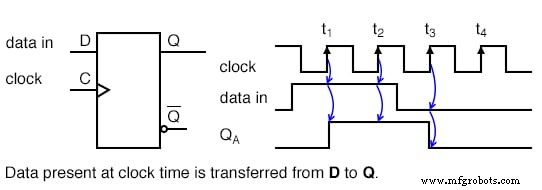

Ниже показан одноступенчатый регистр сдвига, принимающий данные, которые не синхронизированы с часами регистра.

«Данные в» в D штифт типа D FF (Flip-Flop) не меняет уровни, когда часы меняются с низкого на высокий.

Мы можем захотеть синхронизировать данные с общесистемными часами на печатной плате, чтобы повысить надежность цифровой логической схемы.

Очевидный момент (по сравнению с рисунком ниже), проиллюстрированный выше, заключается в том, что любые «данные в» присутствуют в D штифт типа D FF передается с D на выход Q по часам.

Поскольку в нашем примере сдвигового регистра используются элементы памяти с положительным фронтом, выходной сигнал Q следует за D вход, когда часы переходят с низкого на высокий, как показано стрелками вверх на диаграмме выше.

Нет сомнений в том, какой логический уровень присутствует в часах, потому что данные стабильны задолго до и после фронта тактового сигнала.

В многоступенчатых регистрах сдвига это случается редко. Но для начала это был простой пример. Нас интересует только положительный, от низкого к высокому, фронту тактового сигнала.

Падающий край можно игнорировать. Q очень легко увидеть следовать D в указанное выше время.

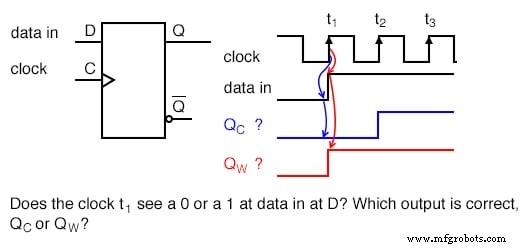

Сравните это с диаграммой ниже, где «входящие данные» меняются с положительным фронтом тактового сигнала.

Поскольку "данные в", кажется, изменяются в момент времени t 1 выше, что означает тип D FF видеть по часам?

Короткий упрощенный ответ заключается в том, что он видит данные, которые присутствовали в D до часов.

Это то, что передается в Q в часы t 1 . Правильная форма волны - Q C . В t 1 Q переходит в ноль, если он еще не равен нулю.

D регистр не видит единицу до момента t 2 , когда Q становится высоким.

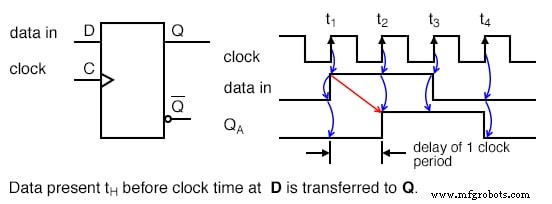

Поскольку данные, приведенные выше, присутствуют в D синхронизируется до Q по часам, а Q не может измениться до следующего времени, D FF задерживает данные на один тактовый период при условии, что данные уже синхронизированы с часами. Q A форма волны такая же, как «входящие данные» с задержкой в один такт.

Более подробно рассмотрим, что ввод типа D Flip-Flop видит, когда следует время.

См. Рисунок ниже. Поскольку "данные в", кажется, изменяются в часы (см. Выше), нам нужна дополнительная информация, чтобы определить, что D ФФ видит.

Если «данные на входе» поступают из другого каскада регистра сдвига, другой такой же тип D FF, мы можем сделать некоторые выводы на основании техпаспорта информация.

Производители цифровой логики предоставляют информацию о своих частях в таблицах данных, ранее доступных только в коллекции, называемой книгой данных .

Книги данных все еще доступны; тем не менее, веб-сайт производителя является современным источником.

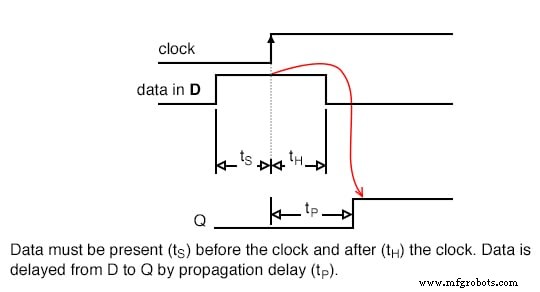

Следующие данные были извлечены из таблицы данных CD4006b для работы при 5 В DC , который служит примером для иллюстрации времени. [*]

- т S =100 нс

- т H =60 нс

- t P =200–400 нс тип. / Макс.

t S это время настройки , данные времени должны быть раньше времени часов. В этом случае данные должны быть представлены в D На 100 нс раньше времени.

Кроме того, данные должны храниться в течение времени удержания . t H =60 нс после времени часов. Эти два условия должны быть соблюдены, чтобы надежно синхронизировать данные из D . на Q триггера.

Нет проблем с соблюдением времени настройки 60 нс, поскольку данные в D был там в течение всего предыдущего периода тактов, если он поступает из другого каскада регистра сдвига.

Например, при тактовой частоте 1 МГц период тактовой частоты составляет 1000 мкс, много времени.

Фактически данные будут присутствовать за 1000 мкс перед тактовым сигналом, что намного больше минимально необходимого t S 60 нс.

Время выдержки t H =60 нс, потому что D, подключенный к Q другого каскада, не может изменяться быстрее, чем задержка распространения предыдущего каскада t P =200 нс.

Время удержания соблюдается до тех пор, пока задержка распространения предыдущего D FF больше времени удержания.

Данные в D управляемый другой стадией Q не будет изменяться быстрее 200 нс для CD4006b.

Подводя итог, выведите Q следует за входом D почти в тактовое время, если триггеры каскадно подключены к многоступенчатому регистру сдвига.

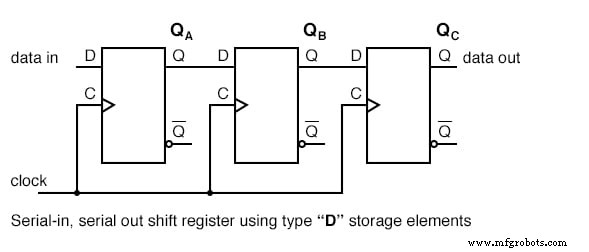

Три типа D Триггеры соединены каскадом от Q к D, а часы соединены параллельно, чтобы сформировать трехступенчатый регистр сдвига, описанный выше.

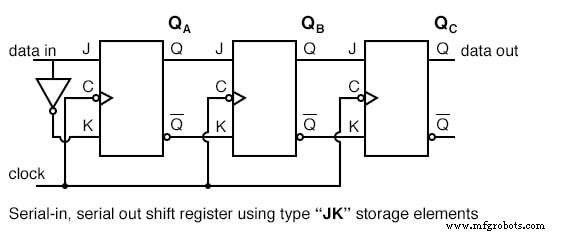

Введите JK . Flip Flopss каскадировал Q в J, Q ’в K с синхронизацией параллельно, чтобы получить альтернативную форму вышеописанного регистра сдвига.

Регистр сдвига с последовательным входом / последовательным выходом имеет вход синхронизации, вход данных и выход данных с последней ступени.

Как правило, другие выходы каскада недоступны. В противном случае это будет регистр сдвига с последовательным входом и параллельным выходом.

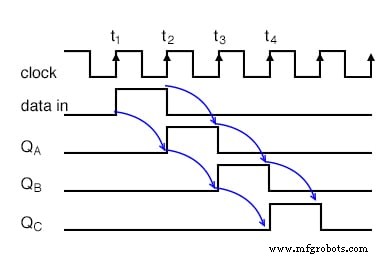

Приведенные ниже формы сигналов применимы к любой из двух предыдущих версий регистра сдвига с последовательным входом и выходом.

Три пары стрелок показывают, что трехступенчатый регистр сдвига временно хранит 3 бита данных и задерживает их на три тактовых периода от входа к выходу.

В часы t 1 «данные в» из 0 синхронизируется с D на Q всех трех этапов. В частности, D этапа A видит логику 0 , который синхронизируется с Q A где он остается до времени t 2 .

В часы t 2 «данные в» из 1 синхронизируется с D кому:Q A . На этапах Б и C , а 0 , поступающий с предыдущих этапов, синхронизируется с Q B и Q C .

В часы t 3 «данные в» из 0 синхронизируется с D кому:Q A . Q A понижается и остается на низком уровне в течение оставшихся часов из-за того, что "входящие данные" равны 0 . Q B становится высоко в t 3 из-за 1 с предыдущего этапа. Q C все еще остается низким после t 3 из-за низкого уровня на предыдущем этапе.

Q C наконец становится высоко в часы t 4 из-за высокой подачи D из предыдущего этапа Q B . На всех более ранних этапах есть 0 s переместился в них. И после следующего тактового импульса в t 5 , вся логика 1 s будет перемещен, заменен на 0 с

Устройства с последовательным входом и выходом

Мы более подробно рассмотрим следующие детали, доступные в виде интегральных схем, любезно предоставленные Texas Instruments.

Чтобы ознакомиться с полными техническими данными устройства, перейдите по ссылкам.

- CD4006b 18-битный регистр сдвига последовательного ввода / вывода

- CD4031b 64-битный регистр сдвига последовательного ввода / вывода

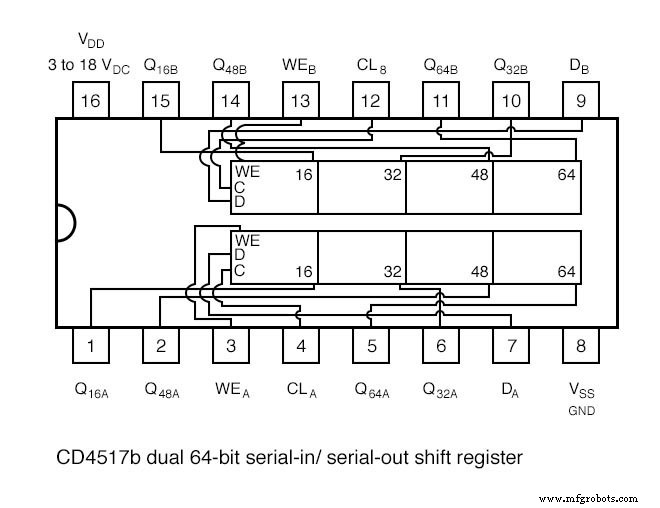

- CD4517b двойной 64-битный регистр сдвига для последовательного ввода / вывода

Следующие регистры сдвига для последовательного ввода / вывода - это CMOS серии 4000. (Комплементарный металл-оксид-полупроводник), детали семейства

Таким образом, они примут V DD , положительный источник питания от 3 до 15 вольт. V SS штифт заземлен.

Максимальная частота тактовой частоты сдвига, которая изменяется в зависимости от V DD , составляет несколько мегагерц.

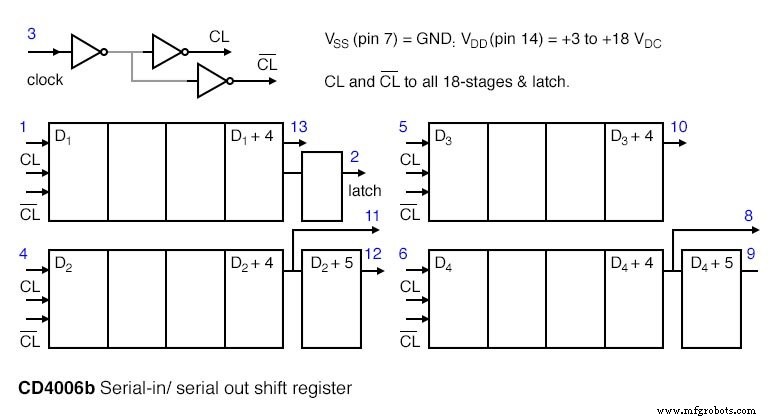

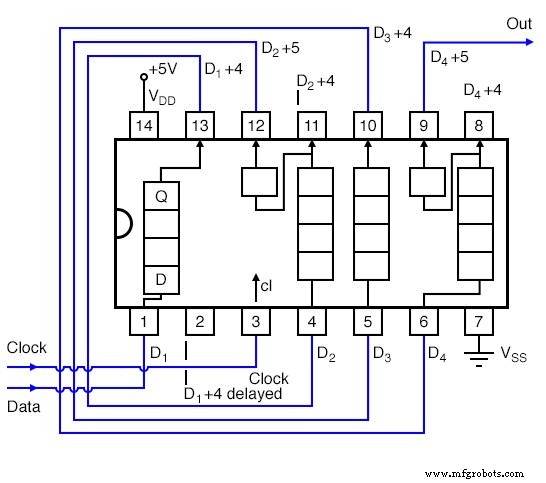

18-битный CD4006b состоит из двух 4-битных каскадов и еще двух 5-битных каскадов с 4-битным выходом.

Таким образом, 5-битные каскады могут использоваться как 4-битные регистры сдвига.

Чтобы получить полный 18-битный регистр сдвига, выход одного регистра сдвига должен быть каскадно подключен ко входу другого и так далее, пока все этапы не создадут один регистр сдвига, как показано ниже.

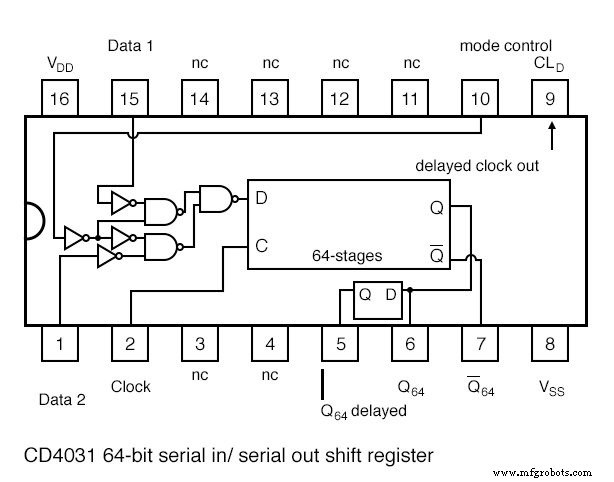

Ниже показан 64-разрядный регистр сдвига последовательного входа / выхода CD4031.

Некоторые контакты не подключены (nc). И Q, и Q ’доступны с 64-го этапа, фактически Q 64 и Q ’ 64 .

Также есть Q 64 «С задержкой» от половинной ступени, которая задерживается на половину такта. Основная особенность - это селектор данных, который находится на входе данных в регистр сдвига.

«Управление режимом» выбирает между двумя входами:данные 1 и данные 2. Если «управление режимом» имеет высокий уровень, данные будут выбраны из «данных 2» для ввода в регистр сдвига.

В случае низкого логического уровня «управление режимом» выбираются «данные 1». Примеры этого показаны на двух рисунках ниже.

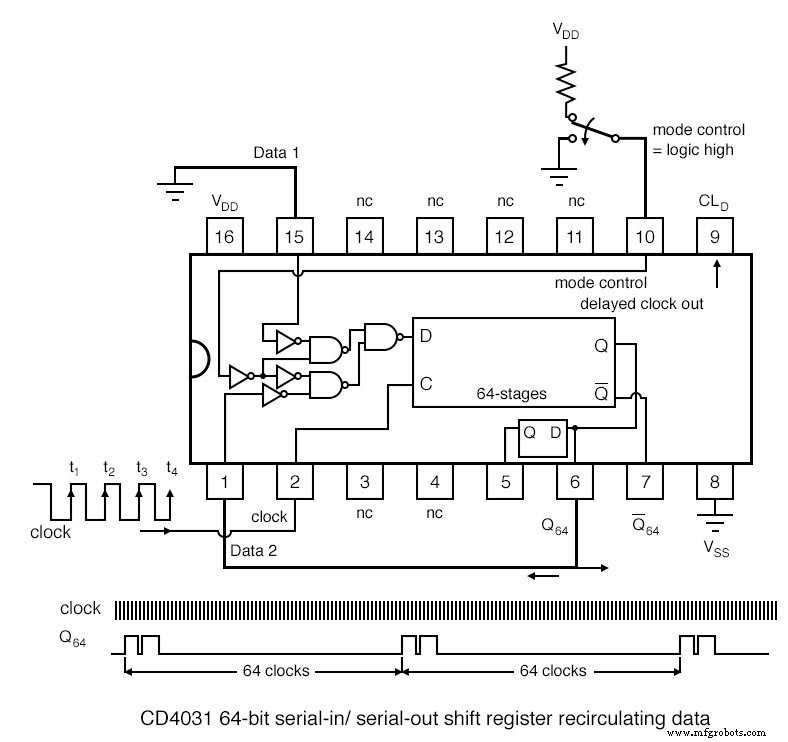

Приведенные выше «данные 2» подключены к Q 64 вывод сдвигового регистра. При высоком «управлении режимом» Q 64 выходной сигнал направляется обратно на вход данных переключателя D.

Данные будут рециркулироваться от вывода к вводу. Данные будут повторяться каждые 64 тактовых импульса, как показано выше.

Возникает вопрос:как этот шаблон данных вообще попал в сдвиговый регистр?

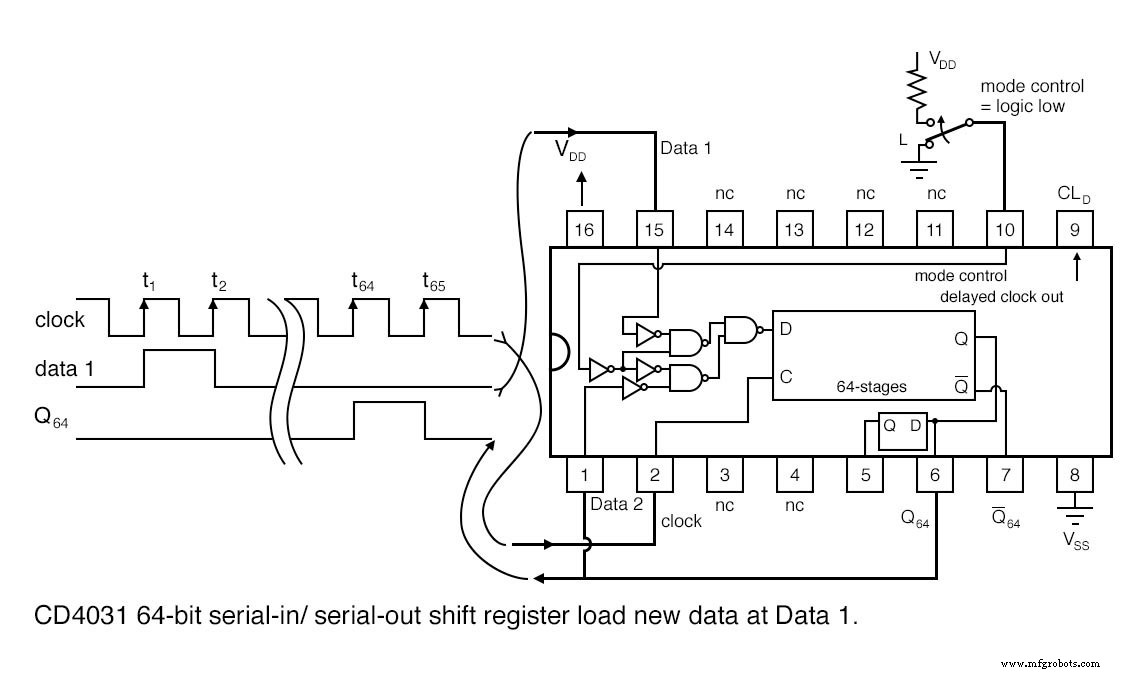

При низком уровне «управление режимом» CD4031 «данные 1» выбираются для ввода в устройство переключения передач.

Выход, Q 64 , не рециркулируется, потому что нижний элемент селектора данных отключен .

Под отключенным мы подразумеваем, что низкий логический уровень «выбор режима», дважды инвертированный в низкий уровень на нижнем логическом элементе И-НЕ, не позволяет ему передавать любой сигнал на нижнем выводе (данные 2) на выход затвора.

Таким образом, он отключен.

Сдвоенный 64-битный регистр сдвига CD4517b показан выше. Обратите внимание на отводы на 16-й, 32-й и 48-й ступенях.

Это означает, что регистры сдвига такой длины можно настроить с помощью одного из 64-битных устройств сдвига.

Конечно, 64-битные устройства сдвига могут быть включены в каскад, чтобы получить 80-битный, 96-битный, 112-битный или 128-битный регистр сдвига.

Часы CL A и CL B должны быть параллельны при каскадном соединении двух переключателей. МЫ B и МЫ B заземлены для нормального переключения передач.

Входными данными в регистры сдвига A и B являются D A и D B соответственно.

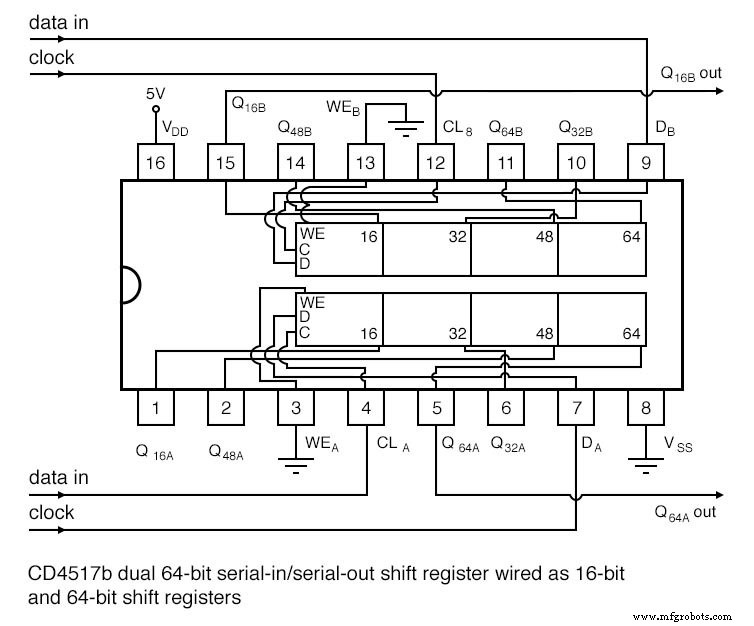

Предположим, нам нужен 16-битный регистр сдвига.

Можно ли это настроить с помощью CD4517b? Как насчет 64-сдвигового регистра из той же части?

Выше мы показываем CD4517b, подключенный как 16-битный регистр сдвига для секции B.

Часы для секции B - CL B . . Данные синхронизируются с CL B . И данные, задержанные на 16 тактов, снимаются с Q 16B . МЫ B , разрешение записи заземлено.

Выше мы также показываем тот же CD4517b, подключенный к 64-битному регистру сдвига для независимой секции A.

Часы для секции A - CL A . Данные поступают в CL A . Данные, задержанные 64-тактовыми импульсами, снимаются с Q 64A . МЫ A , разрешение записи для раздела A заземлено.

СВЯЗАННЫЕ РАБОЧИЕ ТАБЛИЦЫ:

- Таблица регистров сдвига

Промышленные технологии