Как сделать процессоры заслуживающими доверия

Современные интегральные схемы (ИС) предоставляют вычислительные возможности и возможности управления системой для обработки огромных объемов данных, принятия критически важных для безопасности решений в режиме реального времени и защиты конфиденциальных данных. Разработка специализированной интегральной схемы (ASIC) или системы на кристалле (SoC) с программируемой вентильной матрицей (FPGA) с нуля была бы чрезмерно дорогой и трудоемкой. Многие критически важные функции реализованы с использованием сторонней интеллектуальной собственности (IP). Ядра процессоров, например, поставляются специализированными организациями и обеспечивают гибкую программно-программируемую функцию через свою архитектуру набора команд (ISA), которая определяет интерфейс между оборудованием и программным обеспечением. Архитектура процессоров с открытым исходным кодом предоставляет возможность для более тщательного изучения и обеспечения строгой безопасности в системах, которые уже сталкиваются с изменчивой средой угроз. В этой статье описывается подход к обеспечению безопасности IP и SoC на основе ISA с открытым исходным кодом RISC-V.

RISC-V, изобретенный в Калифорнийском университете и управляемый некоммерческой организацией RISC-V Foundation, является первым ISA с открытым исходным кодом, который стал действительно жизнеспособным промышленным выбором для широкого спектра приложений.

RISC-V - это ISA с открытым исходным кодом, изобретенная в Калифорнийском университете и управляемая некоммерческой организацией RISC-V Foundation с более чем 300 членами, основанной в 2015 году. RISC-V - первая ISA с открытым исходным кодом, которая стала действительно жизнеспособный промышленный выбор для широкого спектра применений. Экосистема инструментов, программного обеспечения и опыта стабильно растет. Многие люди и организации уже пожертвовали аппаратные IP-адреса с открытым исходным кодом, реализующие RISC-V ISA. OpenHW Group, например, стремится сделать реальностью долгожданную перспективу использования оборудования с открытым исходным кодом - в частности, процессорных ядер - для микросхем большого объема.

Возникновение RISC-V вызвано множеством причин. RISC-V, созданный с нуля с учетом индивидуальной расширяемости, обеспечивает новый уровень оптимизации оборудования для конкретных рабочих нагрузок. Закон Мура замедляется, и настройка имеет решающее значение для поддержания уровня повышения производительности, которого больше не может обеспечить технологический прогресс в процессе производства полупроводников. Кроме того, архитектура RISC-V не требует затрат на лицензирование и лицензионных отчислений, что позволяет большему количеству компаний разрабатывать инновационные и доступные продукты. Например, многое происходит в области Интернета вещей и носимых устройств с возможностями искусственного интеллекта.

Интеграторы SoC часто используют IP-адреса процессоров RISC-V с открытым исходным кодом или сторонних производителей. Эти конструкции и связанные с ними цепочки инструментов могут быть дополнены пользовательскими инструкциями. Высококачественная среда проверки, поставляемая с IP, и дополнительное тестирование на уровне системы могут дать некоторую уверенность в том, что IP не содержит критических ошибок. К сожалению, для многих приложений этого недостаточно, и необходимо учитывать другие серьезные риски.

Уязвимости и трояны

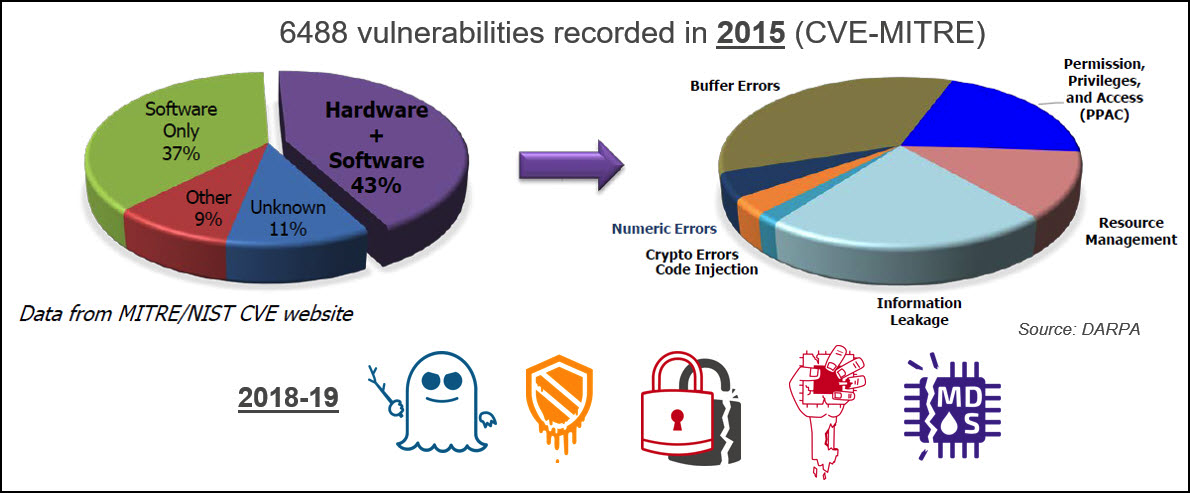

Традиционно уязвимости безопасности в электронных системах были связаны с проблемами системного уровня и программного обеспечения. В последнее время аппаратные IP-адреса, в первую очередь процессоры, также стали центральной проблемой (см. Рис. 1). Реализации процессоров используют микроархитектуры на основе конвейеров и часто включают функции оптимизации производительности и энергопотребления. Сложность увеличивает риск пропустить не только функциональные ошибки, но и уязвимости безопасности. Исследователи безопасности, обнаружившие атаки Meltdown и Spectre в начале 2018 года, продемонстрировали, что функции оптимизации производительности в процессорах могут использоваться непреднамеренно и в гнусных целях. С тех пор было обнаружено гораздо больше уязвимостей как в высокопроизводительных, так и в младших процессорах. Побочные каналы и атаки с временным исполнением могут нарушить защищенные анклавы и позволить вредоносным приложениям утечь конфиденциальные данные или даже взять на себя контроль над системой. И, в отличие от программного обеспечения, проблемы с оборудованием нельзя легко исправить с помощью обновлений по беспроводной сети. Решение аппаратной проблемы с помощью программного обеспечения часто приводит к серьезному снижению производительности.

Архитектура RISC-V имеет множество функций, которые поддерживают реализацию защищенных встроенных систем. Спецификация привилегий определяет четыре режима привилегий (например, компьютер, супервизор, гипервизор и пользователь). Пользовательские инструкции и расширения ISA в процессе ратификации, такие как расширение Cryptographic, обеспечивают дополнительные возможности безопасности. Разработчики могут реализовать несколько безопасных анклавов для изоляции приложений и предотвращения утечки конфиденциальных данных. Однако особенности микроархитектуры RTL могут по-прежнему приводить к уязвимостям безопасности. Эти риски невозможно устранить полностью на уровне ISA. Новый изучаемый подход - это использование расширенного ISA (aISA) для определения аспектов выполнения инструкций на уровне микроархитектуры и, например, управления состоянием буферов или регистров, невидимых на уровне ISA. Функциональные ошибки RTL могут поставить под угрозу все эти функции безопасности.

Менее вероятным, но гораздо более серьезным риском является присутствие вредоносных логических или аппаратных троянов в ядре RISC-V. Аппаратный троянец - это логическая функция, специально разработанная для скрытности, которая активируется в очень редких случаях, известных только злоумышленнику. Определенная последовательность событий данных и управления, которые не могут произойти, пока система работает в целевых вариантах использования, запускает троянскую логику, которая, в свою очередь, доставляет вредоносные полезные данные, например, утечка секрета или критическое нарушение поведения системы. Интеграция SoC с использованием ядер RISC-V с открытым исходным кодом или сторонних производителей больше не может игнорировать этот риск.

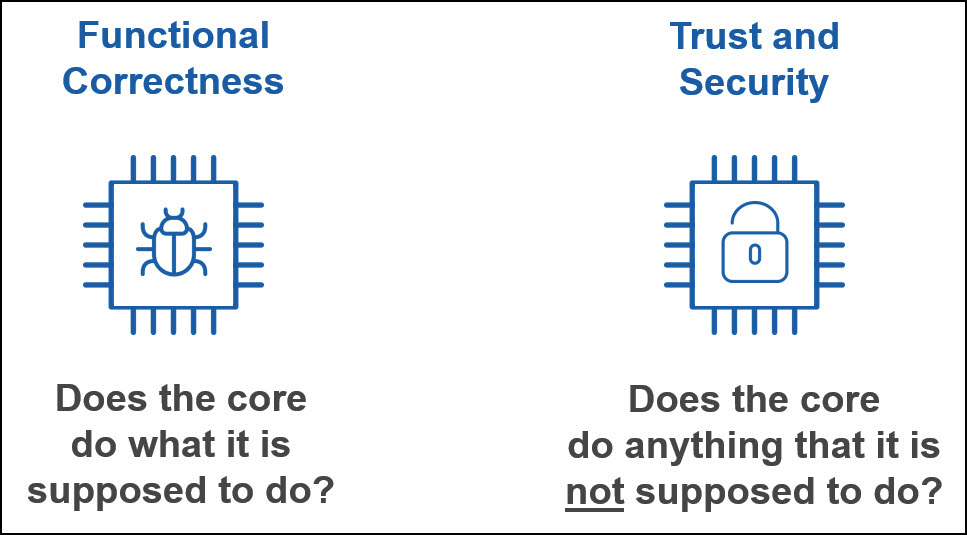

Убедиться, что процессор выполняет то, что он должен делать, сложно, но гарантировать, что он не делает того, что он не должен делать, - еще более сложная задача, которая все еще в значительной степени не решена. Критически важные для безопасности системы и системы, в которых защита конфиденциальности данных имеет первостепенное значение, нуждаются в эффективных и высококачественных решениях, устраняющих риск уязвимостей системы безопасности и троянов.

Рисунок 1. База данных CVE-MITER зафиксировала 6488 уязвимостей в 2015 году, 43% из которых можно классифицировать как программные аппаратные уязвимости. В 2018 и 2019 годах исследователи обнаружили и сообщили о многочисленных уязвимостях в процессорах, включая Meltdown и Spectre, Foreshadow, ZombieLoad, RIDL и Fallout. (Источник:DARPA и OneSpin)

Smart Hardware Assurance

Обеспечение доверия и безопасности IP-адресов RISC-V требует инновационных и эффективных технических решений, которые дополняют подходы к функциональной корректности, в основном нацеленные на предполагаемые варианты использования IP (см. Рис. 2). Поставщики IP несут ответственность за применение современных процессов проверки доверия и безопасности, в то время как интеграторы IP должны иметь доступ к независимым решениям по обеспечению гарантий, которые можно развернуть быстро и без глубоких знаний деталей реализации IP.

Формальные методы могут исчерпывающе анализировать аппаратные функции и предоставлять доказательства того, что IP или SoC точно соответствуют ожидаемому поведению, часто фиксируемому в утверждениях SystemVerilog. Формальная проверка оборудования с использованием программ проверки коммерческих моделей получила широкое распространение за последнее десятилетие. Как правило, провайдеры IP и интеграторы SoC имеют в своих рядах официальных экспертов по верификации, которые пытаются свести к минимуму риск пропуска функциональных ошибок. Хотя некоторые четко определенные формальные задачи проверки можно автоматизировать с помощью приложений , как правило, необходимы значительные инженерные усилия, чтобы зафиксировать ожидаемое поведение IP в утверждениях. Более того, нет гарантии, что было написано достаточно утверждений. Недокументированные функции или непреднамеренные пробелы в наборе утверждений могут привести к непроверенной функциональности IP.

Открытый исходный код RISC-V позволяет разрабатывать заранее подготовленные независимые решения для обеспечения уверенности. Например, решение OneSpin для проверки целостности RISC-V может применяться к широкому спектру микроархитектур. Он включает модели RISC-V ISA и привилегированного ISA, которые являются расширяемыми и могут содержать пользовательские инструкции. Важнейшим аспектом этого решения является то, что оно основано на процессе OneSpin GapFreeVerification ™, который обеспечивает строгое доказательство того, что набор утверждений, моделирующих RISC-V ISA, является полным и свободным от пробелов. Этот аспект имеет первостепенное значение, когда важной задачей является обнаружение аппаратных троянов или недокументированной логики. Решение позволяет интеграторам SoC с ограниченным опытом работы с RISC-V и реализацией RTL под тщательной проверкой получить уверенность в качестве и надежности IP. Разработчики IP могут использовать его для обнаружения слабых мест в системе безопасности и функциональных ошибок перед выпуском.

Рис. 2. Проверка функциональной корректности обеспечивает уверенность в том, что реализация процессора ведет себя, как указано, и удовлетворяет требованиям конечных пользователей. С другой стороны, проверка доверия и безопасности обеспечивает уверенность в том, что процессор не имеет недокументированных функций, непредвиденных побочных каналов, аппаратных троянов или других уязвимостей, которые могут быть использованы злоумышленниками. (Источник:OneSpin)

Это работает?

Процесс обеспечения целостности RISC-V, описанный в предыдущем разделе, был успешно применен к нескольким проектам RTL. Edaptive Computing, компания, которая интегрирует инновационные решения для быстрой оптимизации, обеспечения и автоматизации систем и процессов для различных клиентов Министерства обороны США и коммерческого сектора, применила этот процесс, например, к RocketCore. RocketCore - это проверенное на кристалле 64-битное ядро RISC-V с открытым исходным кодом и 39-битной системой виртуальной памяти. Он имеет пятиэтапный конвейер по очереди, состоящий из одной задачи, с завершением вне очереди для инструкций с длительной задержкой, таких как разделение. Он включает расширенные функции предсказания переходов и воспроизведения инструкций.

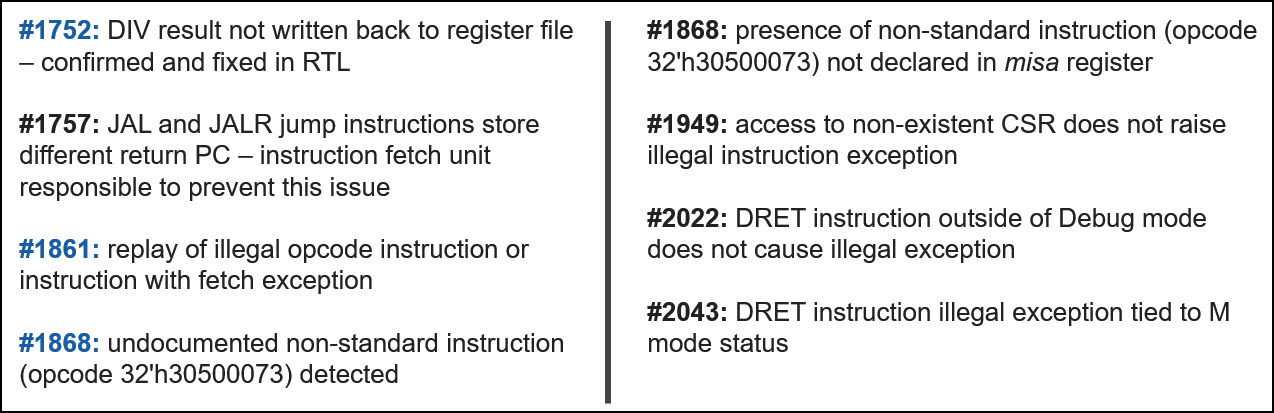

Решение для проверки целостности RISC-V было применено к проекту со всеми инструкциями, уровнями привилегий, прерываниями и механизмом исключений, и было обнаружено 8 проблем (см. Рис. 3). Дополнительная информация о трех из них представлена ниже.

Угловой делитель :серьезная ошибка, связанная с неупорядоченным завершением инструкции деления. Эта проблема могла привести к тому, что программа, использующая операцию деления, вычислила неверные результаты и привела к неправильному поведению системы. Проблема возникает только при сочетании редких обстоятельств, и поэтому предыдущие усилия по проверке не учитывали ее.

Воспроизведение незаконных инструкций :это не крайний случай. Воспроизведение недопустимой инструкции может привести к потере циклов обработки, но если это происходит только в редких ситуациях, влияние на производительность незначительно. Однако следует учитывать и другие аспекты. Воспроизведение инструкций может вызвать ненужные запросы к памяти. Эти запросы могут иметь побочные эффекты, которые могут быть использованы при атаках по побочным каналам. В результате такое поведение необходимо либо устранить, либо четко понять и задокументировать.

Недокументированная инструкция :обнаружена недокументированная нестандартная инструкция CEASE, останавливающая ядро. Фактически, RISC-V RocketCore мог делать то, чего не должен был делать. Недокументированные скрытые функции неприемлемы, когда доверие и безопасность являются проблемой, даже если они относятся к вариантам использования, которые считаются не относящимися к конечному приложению.

Пример использования RocketCore подробно представлен в документе GOMACTech 2019 под названием Полная формальная проверка IP-адресов процессоров RISC-V для надежных ИС, свободных от троянов. Чтобы получить копию, посетите onespin.com/resources/white-papers.

Рис. 3. Список проблем, обнаруженных решениями OneSpin для проверки целостности RISC-V и зарегистрированных в проекте GitHub RocketCore. (Источник:OneSpin)

Что дальше?

Процесс обеспечения RISC-V, представленный в этой статье, выявляет сценарии, которые могут повлиять на безопасность, и систематически обнаруживает недокументированные функции и аппаратные трояны, которые влияют на поведение процессора, независимо от того, насколько они редкие и скрытые. Однако побочные каналы систематически не обнаруживаются. Для исчерпывающего обнаружения всех потенциальных побочных каналов требуется специальное решение с соответствующей технологией. Уже есть прототипы, решающие эту проблему. Для получения дополнительной информации посетите onepin.com/resources/technical-articles и прочтите статью EE Times Атаки по побочным каналам на встроенные процессоры .

Ядра процессора являются важными IP-адресами во встроенных системах. Однако типичная SoC объединяет множество других IP-адресов, которые также могут содержать аппаратных троянов. В отличие от ядер RISC-V, независимые решения по обеспечению доверия могут быть недоступны. В этом случае было бы полезно иметь автоматизированный, не требующий больших усилий процесс оценки доверия, применимый к любому IP. Процесс, не включающий доверенную модель IP, не может гарантировать отсутствие троянца. Однако можно выявить необычные и подозрительные шаблоны кода и известные сигнатуры троянских программ, а также слабые места, которые могут быть использованы на более поздних этапах разработки в гнусных целях. Документ по этой теме под названием Автоматическая оценка надежности IP-адресов до создания кремния для обеспечения надежности оборудования . , созданный инженерами AEROSPACE Corporation и OneSpin, будет представлен на конференции GOMACTech 2020.

Встроенный

- Как максимально использовать свои данные

- Руководство по ускорению приложений с помощью правильных пользовательских инструкций RISC-V

- Как создать платформу для роботов Arduino + Raspberry Pi

- Как сделать стекловолокно

- Как сделать данные цепочки поставок надежными

- Как сделать анимацию в разрезе в Solidworks

- Как сделать прототип

- Как заменить гидравлический шланг

- Как заставить комплексную программу безопасности работать

- Как сделать металлический патрон для токарного станка