Проектирование и внедрение плат межсоединений FDR высокой плотности

В настоящее время скорость передачи высокопроизводительной компьютерной сети с применением высокоскоростной последовательной передачи превратилась в FDR (четырнадцать скоростей передачи данных, 14 Гбит/с), 4-е поколение от первичной SDR (одинарная скорость передачи данных, 2,5 Гбит/с). с), DDR (удвоенная скорость передачи данных, 5 Гбит/с) и QDR (четырехкратная скорость передачи данных, 10 Гбит/с). Конструкция печатной платы (печатной платы) с соединительной и коммутационной платой и интерфейсными картами, которые необходимы для формирования Интернета, вошла в высокоскоростную и высокочастотную область FDR. Поскольку время нарастания сигнала FDR резко сократилось до величины 10 пс, ряд проблем, касающихся целостности сигнала, стал ключевым фактором, определяющим возможность реализации функциональности и надежной работы, таких как затухание, перекрестные помехи, отражение, электромагнитные помехи и т. д. , В зависимости от особенностей микросхем межсоединений FDR, включая несколько портов, несколько каналов, несколько категорий мощности и высокое энергопотребление, для увеличения пропускной способности всегда требуется интегрировать несколько микросхем межсоединений на одной соединительной плате. На плате с ограниченным пространством, с одной стороны, должны быть выполнены некоторые требования, включая компоновку компонентов и рассеивание тепла, маршрутизацию с высокой плотностью, передачу на большие расстояния через заднюю часть платы и целостность всех видов сигналов. С другой стороны, необходимо учитывать некоторые элементы, включая период проектирования печатной платы, ограничения технологии изготовления печатной платы и контроль затрат. Следовательно, это чрезвычайно сложно для реализации проекта и проверки моделирования. Основываясь на примере конструкции печатной платы межсоединения FDR и распределительного щита, в этой статье представлены некоторые методы оптимизации с точки зрения выбора материала подложки, конструкции стека, правил маршрутизации и конструкции защиты от помех для решения проблемы целостности всех видов сигналов в процесс проектирования высокоскоростной печатной платы FDR.

Атрибут затухания и выбор материала подложки

Для высокочастотных сигналов FDR потери в линии передачи являются проблемой целостности сигнала. Когда сигналы FDR передаются от передающего терминала к приемному терминалу по каналам связи, из-за того, что затухание на высоких частотах намного больше, чем затухание на низких частотах, форма сигнала, поступающего на приемный терминал, серьезно деформируется. Деформация в основном классифицируется по двум аспектам:размах напряжения сигналов значительно уменьшился, в то время как сильное ухудшение произошло на фронте нарастания сигнала. Первое ограничивает дальность передачи сигналов, а второе приводит к помехам между кодами. Потери в линии передачи A можно рассматривать как сумму потерь в проводнике Acond и диэлектрические потери Adiel как показано в формуле (1):A =Aдиэль + Aусловие .

Потери в проводнике относятся к потерям, вызванным последовательным резистором на медном проводнике между сигнальным и обратным трактами. В случае высокой частоты скин-эффект заставляет ток течь по поверхности окружающих медных проводников. С увеличением эквивалентного последовательного сопротивления медных проводников потери в проводнике будут возрастать с увеличением частоты, что положительно пропорционально квадратному корню из частоты, что показано в формуле (2): .

.

Диэлектрические потери относятся к потерям, создаваемым средой материала подложки, в основном определяемым свойствами материала и не связанными с геометрической конструкцией, включая ширину проводника, положительно пропорциональную частоте, которая показана в формуле (3): .

.

Согласно формуле (2), увеличение ширины линии способно уменьшить потери в проводнике. Однако в практической конструкции печатной платы ширина проводников никогда не может быть бесконечно большой из-за ограничения расстояния между выводами, платой, количества сигнальных слоев и импеданса. Обычно применяемая ширина/расстояние/ширина проводника в конструкции FDR обычно составляет 7 мил / 7 мил / 7 мил или 8 мил / 10 мил / 8 мил. Когда ширина проводника одинакова, потери в проводнике прямо пропорциональны длине проводника, независимо от материала. Следовательно, чтобы уменьшить общие потери при передаче, необходимо учитывать только диэлектрические потери. Согласно формуле (3), диэлектрические потери пропорциональны коэффициенту диэлектрических потерь, и применение малых коэффициентов диэлектрических потерь может способствовать уменьшению диэлектрических потерь, ведущих к потере общей передачи.

В таблице 1 перечислены параметры атрибутов трех обычных высокоскоростных плат и значения потерь, рассчитанные по формулам (1), (2) и (3) при скорости передачи 14 Гбит/с, ширине проводника 8 мил и импедансе 50 Ом.

| Параметры материала платы | FR4 | Nelco4000-13SI | Мегтрон6 |

| [email protected] | 0,02 | 0,008 | 0,004 |

| [email protected] | 4.10 | 3.200 | 3.600 |

| Aсостояние @7 ГГц/дюйм | 0,24 | 0,240 | 0,240 |

| Адиэль @7 ГГц/дюйм | 0,65 | 0,230 | 0,120 |

| [email protected]/in | 0,89 | 0,470 | 0,360 |

| [email protected]/30in | 27,00 | 14 000 | 11 000 |

| Относительная стоимость | 1,00 | 3.500 | 8 000 |

Можно отметить, что при скорости передачи 14 Гбит/с и длине передачи 30 дюймов общие потери при передаче Nelco4000-13SI составляют приблизительно 14 дБ, в то время как затухание качания напряжения, которое может выдержать типичный чип FDR, находится в диапазоне от 20 дБ до 25 дБ. Таким образом, этот тип материала платы может применяться в конструкции платы межсоединений FDR с расстоянием передачи менее 30 дюймов. Однако общее затухание передачи FR4 составляет примерно 27 дБ, и FR4 не может применяться для конструкции FDR на большие расстояния, но для интерфейсных карт межсоединений FDR с коротким расстоянием передачи разрешено выбирать FR4 для снижения стоимости. Что касается Megtron6, у которого общее затухание передачи наименьшее, он имеет самую высокую стоимость, а его применение в FDR приводит к увеличению платы за архитектуру системы. В заключение, для высокочастотных печатных плат материал платы является основой, и выбор материала платы определяет длину передачи сигналов.

Макет и дизайн стека

При проектировании печатной платы в первую очередь необходимо учитывать структуру печатной платы и стопку. Обычно рисунок и форма печатной платы определяются, а определение количества пакетов зависит от частоты сигнала, плотности контактов печатной платы, стоимости изготовления печатной платы, периода производства и требований к надежности. Платы межсоединений FDR имеют высокую частоту и плотность, а применение многослойных плат является необходимым шагом для снижения помех. Кроме того, очень важно определить номер стека.

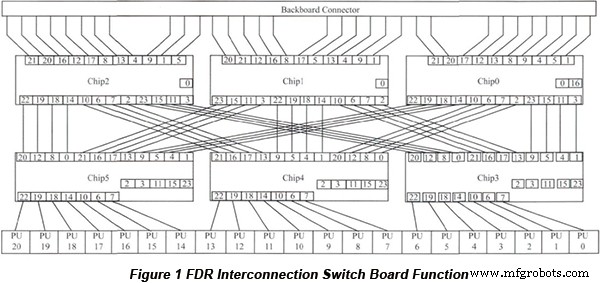

На чипе межсоединений FDR имеется 24 порта, и каждый порт имеет 8 каналов Tx и 8 каналов Rx в методе работы с взаимосвязью. 6 микросхем межсоединений и 3 микросхемы нисходящей линии связи применяются на плате межсоединений FDR, а доступ к 32 портам осуществляется через соединитель задней панели. 3 микросхемы восходящей линии связи получают доступ к 21 порту через оптические волокна QSFP (Quad Small Form-factor Pluggable). Чип восходящего канала и чип нисходящего канала соединены друг с другом через 4 порта, что показано на рисунке 1.

FDR имеет корпус BGA (Ball Grid Array) площадью 50 мм x 50 мм, 1157 контактов и расстоянием между ними 1,0 мм, а контакты P/N на портах Tx и Rx распределены по 3 концентрическим окружностям. Теоретически можно применить 3 сигнальных слоя, чтобы вывести все выводы на всех портах из BGA. При рассмотрении следующих двух элементов можно использовать два сигнальных слоя для доступа к группе контактов концентрических кругов.

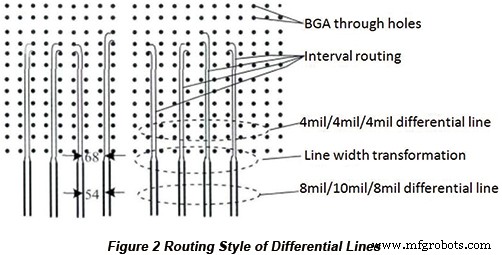

a. Из-за ограничения интервала ширина линии / интервал / ширина дифференциальных линий составляет 4 мил / 4 мил / 4 мил, и она будет расширена до 8 мил / 10 мил / 8 мил, выходящих из BGA, и расстояние между парами дифференциальных линий должно быть не менее 50 мил. Следовательно, пара дифференциальных линий должна занимать ширину 2 мм, а 48 пар сигналов располагаются по краю с наибольшей плотностью. Поэтому реализовать этот метод сложно.

б. Расстояние между контактами BGA составляет 1 мм. Если сигнальный слой применяется для доступа к группе сигналов концентрических кругов, расстояние между парами дифференциальных линий в BGA составляет всего 14 мил, что далеко от требуемых 50 мил. Кроме того, максимальная длина параллельной разводки составляет всего 20 мм, что может вызвать перекрестные помехи.

Чтобы избежать негативных факторов, упомянутых выше, два сигнальных слоя применяются для доступа к группе сигналов концентрических кругов, и дифференциальный сигнал на каждом сигнальном слое должен выводиться из BGA в соответствии с интервалом 50 мил. Следовательно, для соединительных плат FDR требуется не менее 6 слоев, чтобы все дифференциальные сигналы выводились из BGA. С учетом количества подключений и разводки платы и достаточной поверхности платы для обменного конденсатора связи применяются 8 внутренних сигналов и 22-слойный стек.

Анализ перекрестных помех и меры по их уменьшению

Перекрёстные помехи — это первое, что следует учитывать при проектировании высокоскоростных схем с высокой плотностью. При изменении напряжения и тока в наступательной линии будет происходить электромагнитная связь через взаимную емкость и взаимную индуктивность между наступательной линией и линией-жертвой. Перекрёстные помехи, идущие к передающему терминалу по линии-жертве, называются перекрестными помехами ближнего терминала, а перекрестные помехи, идущие к принимающему терминалу по линии-жертве, называются перекрестными помехами дальнего терминала. Вообще говоря, общее шумовое напряжение на линии-жертве должно контролироваться менее чем на 5% от напряжения сигнала. Лучше всего контролировать бюджет перекрестных помех линии атаки с одним краем в пределах 1% с учетом других источников шума и линии атаки вокруг двух сторон от линии жертвы.

Ключевые моменты, которым необходимо следовать с точки зрения уменьшения перекрестных помех, включают:

a. Расстояние между линией нападения и линией жертвы должно быть увеличено, а длина параллельных маршрутов должна быть уменьшена.

b. В качестве обратного пути сигналов применяется интегрированная земля. Согласно эмпирическому закону, для полосковой линии сопротивлением 50 Ом, когда расстояние в три раза превышает ширину линии, перекрестные помехи на ближнем конце составляют примерно 0,5%. Для микрополосковой линии сопротивлением 50 Ом, когда расстояние в три раза превышает ширину линии, перекрестные помехи на ближнем конце составляют примерно 1%. Перекрестные помехи на дальнем конце полосковых линий или полностью встроенных микрополосковых линий почти равны нулю, а полярность перекрестных помех на дальнем конце микрополосковых линий передачи отрицательна, а ее величина относительно велика, поскольку влияние индуктивной связи больше, чем емкостной связи.

• Интервальная маршрутизация

В этой конструкции дифференциальное сопротивление высокоскоростной дифференциальной линии составляет 100 Ом. На основе полевого решателя Si9000 ширина линии/интервал/ширина линии рассчитывается как 8 мил / 10 мил / 8 мил. Чем шире линия, тем меньше затухание, и расстояние 10 мил должно поддерживать дифференциальное сопротивление 100 Ом. Этот тип дифференциальной линии применяется за пределами области чипа BGA. Для уменьшения перекрестных помех расстояние между двумя парами дифференциальных линий составляет не менее 80 мил. The spacing between pins of interconnection chip in this article is 1mm and the through hole size limitation of BGA makes the line width/spacing/line width of the differential line in the BGA chip area 4mil/4mil/4mil. Although the differential impedance of this type of differential line is 100Ω as well, the lead loss is big, requiring differential line of 4mil/4mil/4mil to be transformed into 8mil/10mil/8mil as soon as it enters BGA chip area. In order to reduce crosstalk, differential line of 4mil/4mil/4mil in BGA chip area applies the way of interval routing to ensure the spacing between two pairs of differential lines more than 50mil as well, which is shown in Figure 2.

• Differential holes

Specific differential holes are set in this design for the application of exchange coupling capacitance on the connection surface layer. Ground holes have to be placed beside differential holes to provide backflow channel for returning path. Design of four ground holes features the best effect and two ground holes can be also applied when the area of board is limited. Besides, measures such as back drilling and internal pad eliminationhave should be taken to differential holes to reduce the impedance change at differential holes in order to decrease crosstalk and reflection.

• Preventing Tx and Rx from being routed in the same layer

In order to reduce crosstalk, Tx differential line should be routed in the different layer from Rx differential line. Here, Tx refers to the source terminal of differential line while Rx refers to the receiving terminal of differential line. If both of them have to be routed in the same layer, the spacing between them has to be over 5mm to ensure safety.

• 20H rule

In the PCB circuit with high frequency and high speed, RF energy is coupled by PCB power layer and ground layer and edge magnetic flux leakage is generated between power layer and ground layer. The radio RF energy can be radiated to the free space. 20H rule indicates that if there are high-speed currents on the board, there are electromagnetic fields associated with them. In the design of this article, the distance between all the routings and board edge should be at least 20 times of line width and the distance between high-speed differential holes and power plane cut-off lines is at least 5mm.

• Routing on the surface layer

In the design of high-frequency PCBs, with the relatively big far-end crosstalk between microstrip lines and strip lines considered, high-speed differential lines are prohibited on the surface layer. In the design of this article, at most 8 internal routing layers are required owing to the limitation of manufacturing craft. Moreover, the terminal arrangement limitation of interconnection chip makes it impossible for internal layers only to implement the connections of the interconnection differential lines between 6 chips inside connection board.

Helpful Resources

• Something You Must Know about HDI

• History of High-Density Packaging Technology

• 3 Keys to Designing a Successful HDI PCB

• Advantages of HDI Printed Circuit Boards

• Full Feature PCB Manufacturing Service from PCBCart - Multiple Value-added options

• Advanced PCB Assembly Service from PCBCart - Start from 1 piece

Промышленные технологии

- Как документировать кабели и жгуты

- Что такое отбойные молотки? - Типы, конструкция и работа

- Высокотехнологичные заказные печатные платы

- Рекомендации по проектированию ВЧ и СВЧ

- Материалы и дизайн печатных плат для высокого напряжения

- Возможности гибкого и жесткого изгиба при проектировании печатных плат

- Неудачи и решения при проектировании радиочастотных печатных плат

- Вольфрам

- Процесс проектирования и внедрения автоматизации производства

- Рост межблочных печатных плат высокой плотности