Универсальные регистры сдвига:параллельный вход, параллельный выход

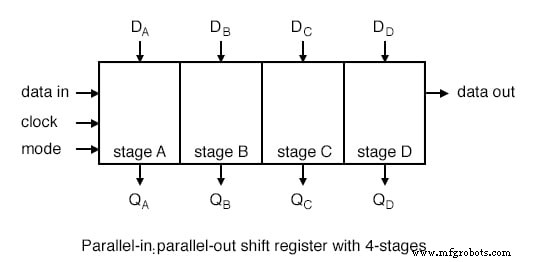

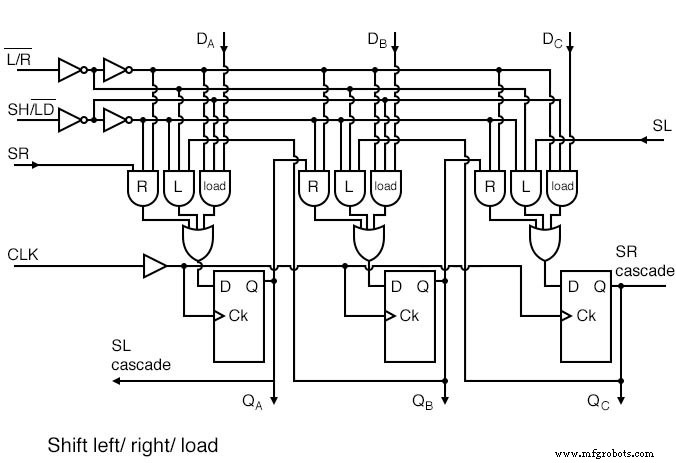

Регистр сдвига с параллельным входом / параллельным выходом предназначен для приема параллельных данных, их сдвига и вывода, как показано ниже.

Универсальный регистр сдвига - это универсальное устройство в дополнение к функции параллельного ввода / вывода.

Выше мы применяем четыре бита данных к регистру сдвига с параллельным входом / параллельным выходом в D A D B D C D D . Управление режимом, которым может быть несколько входов, управляет параллельной загрузкой и смещением.

Управление режимом также может управлять направлением переключения в некоторых реальных устройствах. Данные будут сдвинуты на одну битовую позицию для каждого тактового импульса.

Сдвинутые данные доступны на выходах Q A Q B Q C Q D . Входящие и исходящие данные предназначены для каскадирования нескольких этапов.

Хотя выше мы можем только каскадировать данные для сдвига вправо. Мы могли бы обеспечить каскадирование данных при сдвиге влево, добавив пару сигналов, указывающих влево, «данные на входе» и «данные на выходе», как указано выше.

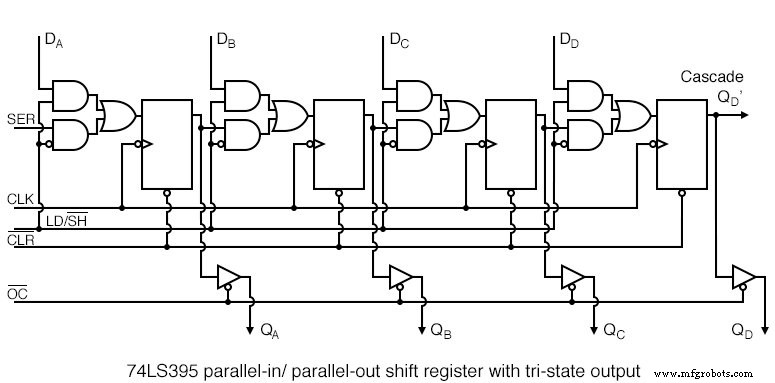

Внутренние детали сдвигового регистра с параллельным входом и выходом правого сдвига показаны ниже.

Буферы с тремя состояниями не являются строго обязательными для сдвигового регистра параллельного ввода / вывода, но являются частью реального устройства, показанного ниже.

74LS395 настолько близко соответствует нашей концепции гипотетического сдвигового регистра с параллельным входом / параллельным выходом со сдвигом вправо, что мы используем чрезмерно упрощенную версию данных, приведенных выше.

Более подробную информацию см. По ссылке на полную таблицу данных далее в этой главе.

LD / SH ’ управляет мультиплексором И-ИЛИ на входе данных в FF. Если LD / SH ’=1 , четыре верхних логических элемента И включены, что позволяет использовать параллельные входы D A D B D C D D к четырем входам данных FF.

Обратите внимание на пузырек инвертора на тактовом входе четырех FF. Это указывает на то, что 74LS395 синхронизирует данные по отрицательной тактовой частоте, которая является переходом от высокого к низкому уровню.

Четыре бита данных будут синхронизироваться параллельно с D A D B D C D D на Q A Q B Q C Q D на следующих часах, идущих отрицательно. В этой «реальной части» OC ’ должен быть низким, если данные должны быть доступны на фактических выходных контактах, а не только на внутренних FF.

Ранее загруженные данные могут быть сдвинуты вправо на одну битовую позицию, если LD / SH ’=0 . для последующих отрицательных фронтов тактовых импульсов.

Четыре такта полностью смещают данные из нашего 4-битного регистра сдвига. Данные будут потеряны, если наше устройство не будет подключено каскадом из Q D ’ на SER другого устройства.

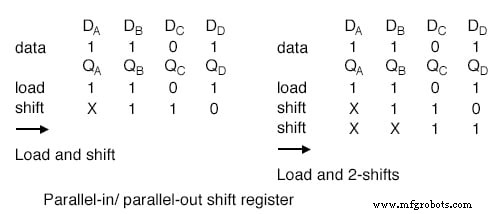

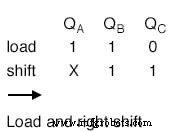

Выше образец данных представлен входам D A D B D C D D . Шаблон загружен в Q A Q B Q C Q D . Затем он сдвигается на один бит вправо.

Входящие данные обозначаются значком X . , то есть мы не знаем, что это такое. Если вход ( SER ) были обоснованы, например, мы бы знали, какие данные ( 0 ) был сдвинут.

Также показан сдвиг вправо на две позиции, требующий двух часов.

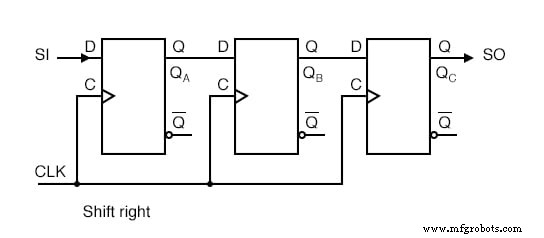

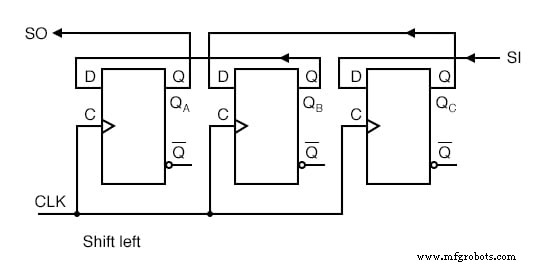

На приведенном выше рисунке показано оборудование, используемое для сдвига данных вправо.

С этой цифрой слишком просто возиться, если не считать сравнения с более сложными цифрами.

Правый сдвиг данных приведен выше для ссылки на предыдущий правый сдвиг.

Если нам нужно сдвинуть влево, FF нужно перепрограммировать. Сравните с предыдущим правым переключателем. Кроме того, SI и ТАК были отменены. SI переходит на Q C . Q C переходит на Q B . Q B переходит на Q A . Q A уходит на SO соединение, где оно может быть передано другому переключателю SI . Эта последовательность сдвига влево является обратной по сравнению с последовательностью сдвига вправо.

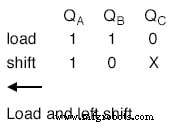

Выше мы сдвигаем тот же образец данных влево на один бит.

Есть одна проблема с рисунком «сдвиг влево» выше. Для этого нет рынка. Детали с левым сдвигом никто не производит.

«Настоящее устройство», которое сдвигает одно направление, может быть подключено снаружи, чтобы сдвигать другое направление. Или, если мы скажем, что нет левого или правого в контексте устройства, которое смещается только в одном направлении.

Однако существует рынок устройств, которые могут переключаться влево или вправо по команде с помощью линии управления. Конечно, в этом контексте допустимы "лево" и "право".

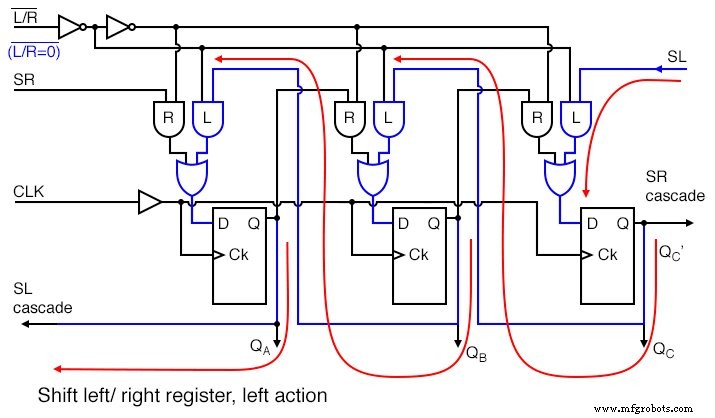

То, что мы имеем выше, является гипотетическим регистром сдвига, способным сдвигать любое направление под управлением L ’/ R . .

Он настроен с помощью L ’/ R =1 . чтобы сместить нормальное направление вправо. L ’/ R =1 включает мультиплексор И вентили, помеченные как R .

Это позволяет данным следовать по пути, показанному стрелками, когда применяются часы. Путь подключения такой же, как на рисунке выше "слишком простой" со сдвигом вправо.

Данные поступают в SR , на Q A , на Q B , в Q C , где он уходит в каскад SR . Этот вывод может управлять SR другого устройства справа.

Что, если мы изменим L ’/ R на L ’/ R =0 ?

При L ’/ R =0 , мультиплексор И вентили, помеченные как L включены, образуя путь, показанный стрелками, такой же, как на приведенном выше рисунке «сдвиг влево».

Данные передаются на SL , в Q C , на Q B , на Q A , откуда он уходит на каскад SL . Этот вывод может управлять SL другого устройства слева.

Основное достоинство двух приведенных выше рисунков, иллюстрирующих «регистр сдвига влево / вправо», - простота.

Работа левого правого регулятора L ’/ R =0 легко понять. Коммерческая часть требует параллельной загрузки данных, подразумеваемой заголовком раздела. Это показано на рисунке ниже.

Теперь, когда мы можем сдвигать вправо и влево с помощью клавиш L ’/ R . , давайте добавим SH / LD ’ , сдвиг / загрузка, а логические элементы И помечены как «загрузка», чтобы обеспечить параллельную загрузку данных со входов D A D B D C .

Когда SH / LD ’=0 , И ворота R и L отключены, И ворота "load" включены для передачи данных D A D B D C ко входам данных FF. следующие часы CLK синхронизирует данные с Q A Q B Q C .

Пока присутствуют одни и те же данные, они будут повторно загружаться на следующих часах. Однако данные, представленные только для одного тактового сигнала, будут потеряны с выходов, когда они больше не будут присутствовать на входах данных.

Одно из решений - загрузить данные по одним часам, а затем перейти к переключению на следующих четырех часах. Эта проблема устранена в 74ALS299 путем добавления еще одного логического элемента И к мультиплексору.

Если SH / LD ’ изменяется на SH / LD ’=1 , элементы И, помеченные как «нагрузка», отключены, позволяя левое / правое управление L ’/ R чтобы установить направление сдвига на L или R И ворота. Сдвиг такой же, как на предыдущих рисунках.

Единственное, что необходимо для создания жизнеспособного интегрированного устройства, - это добавить четвертый логический элемент И к мультиплексору, как упоминалось для 74ALS299.

Это показано в следующем разделе этой части.

Устройства с параллельным входом / параллельным выходом и универсальные

Давайте подробнее рассмотрим регистры сдвига с последовательным входом / параллельным выходом, доступные в виде интегральных схем, любезно предоставленные Texas Instruments.

Чтобы ознакомиться с полными техническими характеристиками устройства, перейдите по ссылкам.

-

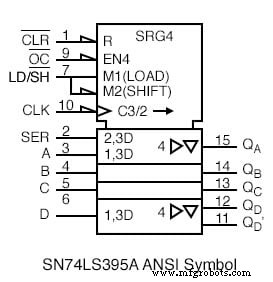

SN74LS395A 4-битный регистр сдвига с параллельным входом / параллельным выходом

-

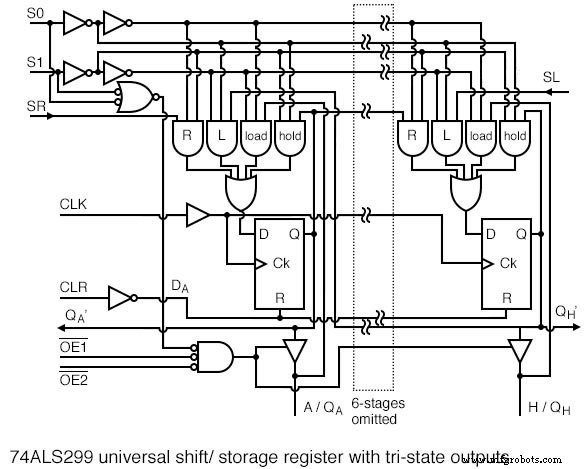

SN74ALS299 8-битный универсальный сдвиговый регистр с параллельным входом / параллельным выходом

Мы уже рассмотрели внутренние детали SN74LS395A, см. Предыдущий рисунок выше, регистр сдвига 74LS395 с параллельным входом / параллельным выходом и выходом с тремя состояниями.

Прямо над ним находится символ ANSI для 74LS395.

Почему только 4 бита, как указано в SRG4 выше? Наличие как параллельных входов, так и параллельных выходов, в дополнение к выводам управления и питания, не позволяет использовать больше битов ввода / вывода (ввод / вывод) в 16-контактном DIP (Dual Inline Package).

R указывает, что каскады регистра сдвига сбрасываются входом CLR ’ (активная нижняя инвертирующая половина стрелки на входе) секции управления вверху символа. OC ’ при низком уровне (снова перевернуть стрелку) будет включен ( EN4 ) четыре буфера вывода с тремя состояниями ( Q A Q B Q C Q D ) в разделе данных.

Нагрузка / смена ’( LD / SH’ ) на контакте (7) соответствует внутреннему устройству M1 (нагрузка) и M2 (сдвиг). Ищите префиксы 1 и 2 в остальной части символа, чтобы определить, что ими управляется.

Часы, чувствительные к отрицательному фронту (обозначены перевернутой стрелкой на выводе 10) C3 / 2 выполняет две функции.

Во-первых, 3 из C3 / 2 влияет на любой ввод с префиксом 3 , скажем 2,3D или 1,3D в разделе данных.

Это будет параллельная нагрузка на A, B, C, D связано с M1 и C3 для 1,3D . Во-вторых, 2 из C3 / 2 -право-стрелка указывает на синхронизацию данных в любом месте 2 появляется в префиксе ( 2,3D на выводе-2).

Таким образом, у нас есть синхронизация данных в SER . в Q A с режимом 2 . Стрелка вправо после C3 / 2 учитывает сдвиг на этапах внутреннего регистра сдвига Q A Q B Q C Q D .

Правые указывающие треугольники указывают на буферизацию; перевернутый треугольник указывает на три состояния, которые контролируются EN4 .

Обратите внимание:все 4 s в символе, связанном с EN часто опускаются. Этапы Q B Q C считаются имеющими те же атрибуты, что и Q D . Q D ’ каскадно переходят к SER следующего пакета вправо.

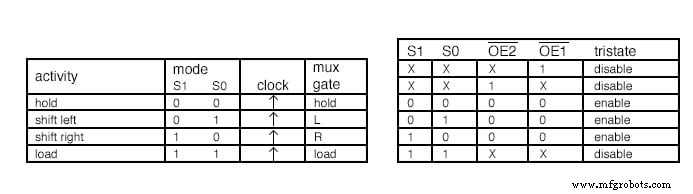

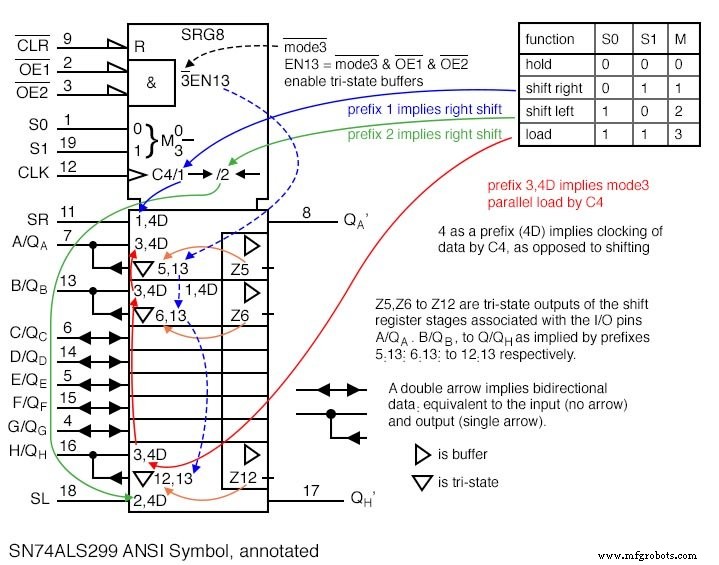

В приведенной выше таблице, взятой из таблицы данных «299», резюмируется работа универсального регистра сдвига / хранения 74ALS299.

Для получения полной информации перейдите по ссылке «299» выше. Входы мультиплексора R , L , загрузка действуют как на предыдущих рисунках «сдвиг влево / вправо».

Разница в том, что входы режима S1 и S0 выберите сдвиг влево, сдвиг вправо и загрузите с режимом S1 S0 = по 01 , 10 и 11 соответственно, как показано в таблице, включение шлюзов мультиплексора L , R и загрузить соответственно.

См. Таблицу. Незначительное отличие - параллельный путь нагрузки от выходов с тремя состояниями. На самом деле буферы с тремя состояниями отключены (должны быть) отключены S1 S0 =11 для поддержки шины ввода-вывода для использования в качестве входных данных.

Автобус - это набор похожих сигналов. Входные данные применяются к A , B через H (те же контакты, что и Q A , Q B через Q H ) и направляется к нагрузке шлюз в мультиплексоры, а на D входы ФФ. Данные представляют собой параллельную нагрузку на тактовый импульс.

Один новый вентиль мультиплексора - вентиль И с меткой удерживать . , активируется S1 S0 =00 . удержание ворота разрешают путь от Q вывод FF обратно в удержание ворот, на вход D того же ФФ. В результате в режиме S1 S0 =00 , выход постоянно перезагружается с каждым новым тактовым импульсом. Таким образом, данные хранятся. Это кратко изложено в таблице.

Для чтения данных с выходов Q A , Q B через Q H , буферы с тремя состояниями должны быть включены с помощью OE2 ’, OE1’ =00 и mode = S1 S0 =00, 01 или 10 .

То есть mode любой, кроме load . . См. Вторую таблицу.

Сдвиг вправо данные из пакета влево, сдвигается на SR Вход. Любые данные, сдвинутые вправо со стадии Q H каскады вправо через Q H ’.

Буферы с тремя состояниями не влияют на этот вывод. Последовательность сдвига вправо для S1 S0 =10 это:

SR> Q A > Q B > Q C > Q D > Q E > Q F > Q G > Q H (Q H ’)

Сдвиг влево данных из пакета вправо сдвигается на SL Вход. Любые данные, сдвинутые влево от этапа Q A каскады влево через Q A ’, Также не подвержен влиянию буферов с тремя состояниями. Последовательность сдвига влево для S1 S0 =01 это:

(Q A ’) Q A B

C

D

E

F

G

H (Q SL ’)

Сдвиг может происходить при отключении буферов с тремя состояниями одним из OE2 ’ или OE1 ’=1 . Однако выходы содержимого регистров будут недоступны. См. Таблицу

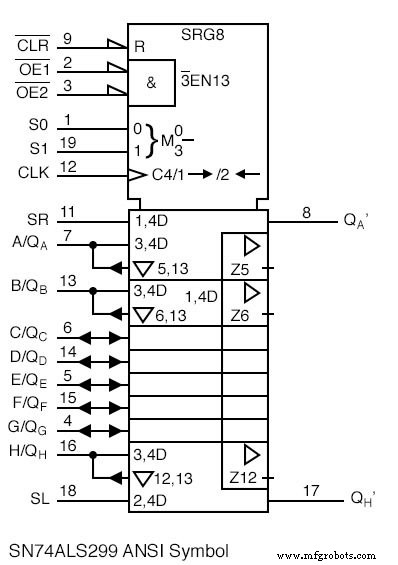

«Чистый» символ ANSI для 8-битного универсального сдвигового регистра SN74ALS299 с параллельным входом / параллельным выходом и выходом с тремя состояниями показан для справки выше.

Аннотированная версия символа ANSI показана для пояснения содержащейся в нем терминологии.

Обратите внимание, что режим ANSI (S0 S1) отличается от порядка (S1 S0), использованного в предыдущей таблице.

Это меняет местами десятичные числа режима (1 и 2). В любом случае мы полностью согласны с официальной таблицей данных, копируя это несоответствие.

Практическое применение

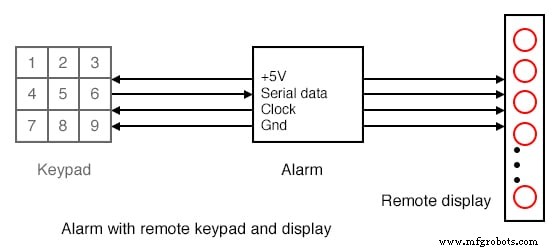

Блок-схема сигнализации с удаленной клавиатурой повторяется ниже. Ранее мы создавали считыватель клавиатуры и выносной дисплей как отдельные блоки.

Теперь мы объединим клавиатуру и дисплей в единый блок, используя универсальный регистр сдвига.

Хотя на схеме и разделены, клавиатура и дисплей находятся в одном удаленном корпусе.

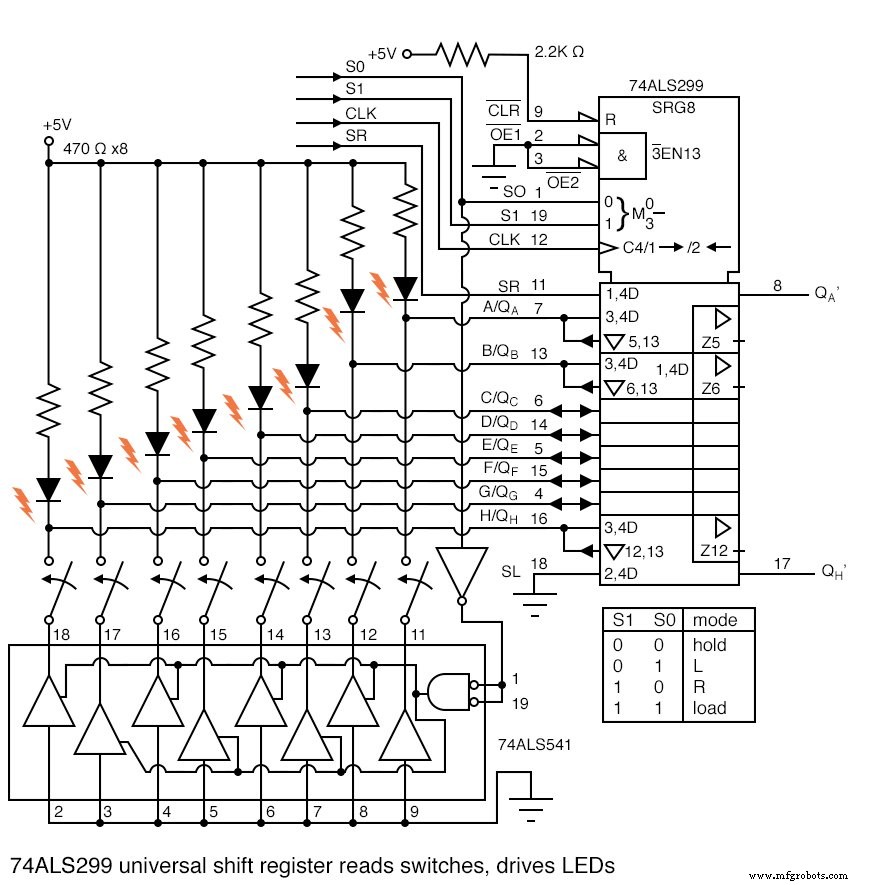

Мы будем параллельно загружать данные клавиатуры в регистр сдвига на одном тактовом импульсе, а затем переместить их в главное окно аварийной сигнализации.

В то же время мы переместим данные светодиода из основного сигнала тревоги в удаленный регистр сдвига, чтобы светодиоды загорелись.

Мы будем одновременно переносить данные с клавиатуры и данные светодиодов в регистр сдвига.

Восемь светодиодов и токоограничивающие резисторы подключены к восьми контактам ввода-вывода универсального сдвигового регистра 74ALS299.

Светодиоды могут работать только в режиме 3 с S1 =0 S0 =0 . OE1 ’ и OE2 ’ включения трех состояний заземлены для постоянного включения трехсторонних выходов в режимах 0, 1, 2 .

Это приведет к тому, что светодиоды загорятся (мерцают) во время переключения. Если это была проблема, EN1 ’И EN2’ может быть незаземленным и параллельно с S1 и S0 соответственно, чтобы включить только буферы с тремя состояниями и загорать светодиоды во время удержания, режим 3 . Давайте рассмотрим этот пример проще.

Во время параллельной загрузки S0 =1 инвертирован в 0, позволяет восьмимеричным буферам с тремя состояниями заземлять дворники переключателя.

Верхние разомкнутые контакты переключателя подтягиваются до логического уровня за счет комбинации резистора и светодиода на восьми входах.

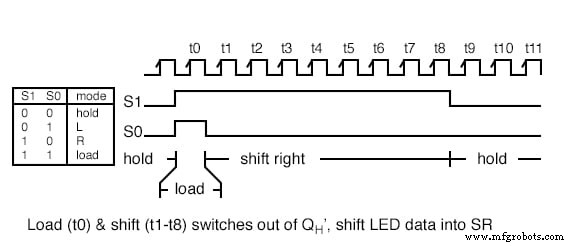

Любое замыкание переключателя закоротит входной низкий уровень. Мы параллельно загружаем данные коммутатора в ‘299 в часы t0 когда оба S0 и S1 высокие. См. Кривые ниже.

Один раз S0 понижается, восемь тактов ( t0 в t8 ) данные о закрытии переключателя передач из ‘299 через Q h ’ булавка.

В то же время новые данные светодиода переносятся в SR . из 299 на те же восемь часов. Данные светодиода заменяют данные о замыкании переключателя в процессе переключения.

После часов 8-й смены t8 , S1 переходит в режим удержания доходности ( S1 S0 =00 ). Данные в регистре сдвига остаются прежними, даже если тактовых импульсов больше, например T9 . , t10 и т. д.

Откуда берутся формы волны? Они могут быть сгенерированы микропроцессором, если тактовая частота не превышает 100 кГц, и в этом случае было бы неудобно генерировать какие-либо часы после t8 . .

Если бы часы находились в мегагерцовом диапазоне, они бы работали непрерывно. Часы, S1 и S0 будет генерироваться цифровой логикой, здесь не показано.

СВЯЗАННЫЕ РАБОЧИЕ ТАБЛИЦЫ:

- Таблица регистров сдвига

Промышленные технологии

- Сетевые протоколы

- Почему цифровой?

- Микропроцессоры

- Данные операционного усилителя

- Данные о поражении электрическим током

- Производство на основе данных здесь

- Использование ваших данных

- Большие данные против искусственного интеллекта

- Коды Data Matrix против QR-кодов

- Что такое данные технического обслуживания?