Регистры сдвига:преобразование параллельного входа и выхода (PISO)

Регистры сдвига с параллельным входом / последовательным выходом делают все, что делали предыдущие регистры сдвига с последовательным входом / последовательным выходом, плюс ввод данных для всех этапов одновременно.

Регистр сдвига с параллельным входом / последовательным выходом хранит данные, сдвигает их по тактовому принципу и задерживает их на количество этапов, умноженное на тактовый период.

Кроме того, параллельный вход / последовательный выход действительно означает, что мы можем загружать данные параллельно на всех этапах до того, как начнется какое-либо переключение.

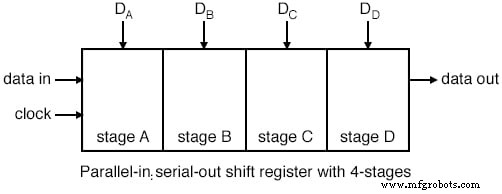

Это способ преобразования данных из параллельной форматировать в серийный формат. Под параллельным форматом мы подразумеваем, что биты данных присутствуют одновременно на отдельных проводах, по одному для каждого бита данных, как показано ниже.

Под последовательным форматом мы подразумеваем, что биты данных представлены последовательно во времени на одном проводе или цепи, как в случае «вывода данных» на блок-схеме ниже.

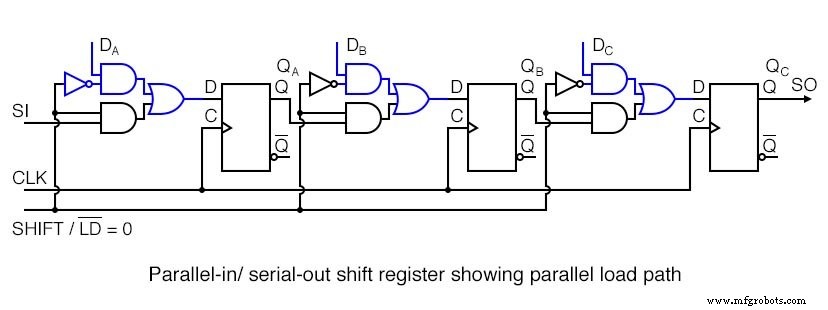

Ниже мы подробно рассмотрим внутренние детали трехступенчатого сдвигового регистра с параллельным входом и последовательным выходом.

Этап состоит из типа D Триггер для хранения и селектор И-ИЛИ, чтобы определить, будут ли данные загружаться параллельно, или сдвинуть сохраненные данные вправо.

Как правило, эти элементы будут повторяться в течение необходимого количества этапов. Мы показываем три этапа из-за нехватки места.

Четыре, восемь или шестнадцать бит - это нормально для реальных деталей.

Выше мы показываем параллельный путь загрузки, когда SHIFT / LD ’имеет низкий логический уровень. Верхние ворота NAND, обслуживающие D A D B D C включены, передавая данные на входы D типа D Вьетнамки Q A Q B D C соответственно.

При следующем положительном фронте тактовой частоты данные будут синхронизированы от D до Q трех FF. Три бита данных будут загружены в Q A Q B D C одновременно.

Только что описанный тип параллельной нагрузки, при которой данные загружаются в виде тактового импульса, известен как синхронная загрузка . потому что загрузка данных синхронизирована с часами.

Это нужно отличать от асинхронной нагрузки . где загрузка контролируется предварительно установленными и очищенными контактами триггеров, для чего не требуются часы.

В отдельном устройстве используется только один из этих методов загрузки, синхронная загрузка более распространена в новых устройствах.

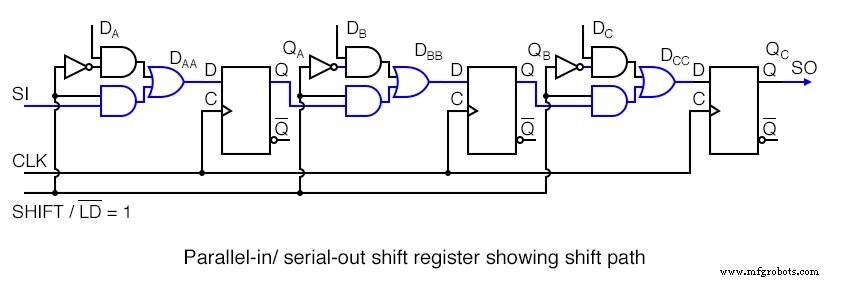

Путь сдвига показан выше, когда SHIFT / LD ’имеет высокий логический уровень. Нижние вентили И пар, питающих логический элемент ИЛИ, включены, что дает нам соединение регистра сдвига SI с D A , Q A кому:D B , Q B в D C , Q C в SO. Тактовые импульсы приведут к сдвигу данных вправо в сторону SO на последовательных импульсах.

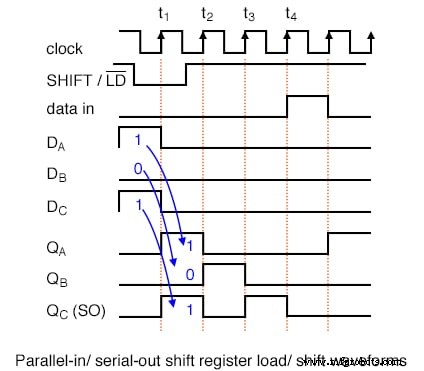

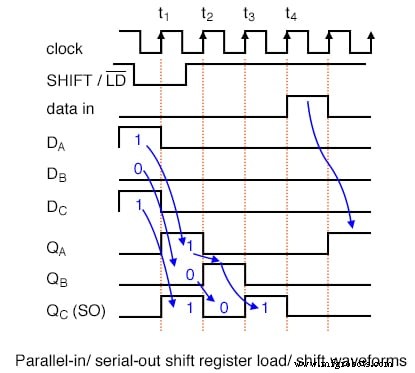

Осциллограммы ниже показывают как параллельную загрузку трех битов данных, так и последовательный сдвиг этих данных. Параллельные данные в D A D B D C преобразуется в последовательные данные в SO.

То, что мы ранее описывали словами для параллельной нагрузки и сдвига, теперь представлено в виде сигналов выше.

В качестве примера приведем 101 к параллельным входам D AA Д BB D CC . Затем SHIFT / LD ’становится низким, что позволяет загружать данные, а не сдвигать данные.

Он должен быть низким за короткое время до и после тактового импульса из-за требований установки и удержания. Он значительно шире, чем должен быть.

Хотя при синхронной логике ее удобно сделать широкой. Мы могли бы сделать активный низкий SHIFT / LD ’шириной почти на два такта, низкий - почти за такт до t 1 и обратно высоко перед t 3 .

Важным фактором является то, что он должен быть низким круглосуточно t 1 чтобы разрешить параллельную загрузку данных по часам.

Обратите внимание, что при t 1 данные 101 в D A D B D C синхронизируется от D до Q триггеров, как показано в Q A Q B Q C в момент t 1 .

Это параллельная загрузка данных синхронно с часами.

Теперь, когда данные загружены, мы можем сдвинуть их при условии, что SHIFT / LD ’имеет высокий уровень для включения сдвига, что происходит до t 2 .

В t 2 данные 0 в Q C сдвигается из SO, что совпадает с Q C форма волны. Он либо переключается на другую интегральную схему, либо теряется, если к SO ничего не подключено.

Данные в Q B , а 0 сдвигается на Q C . 1 в Q A сдвигается в Q B . С "данными в" 0 , Q A становится 0 . После t 2 , Q A Q B Q C = 010 .

После t 3 , Q A Q B Q C = 001 . Это 1 , который изначально присутствовал на Q A после t 1 , теперь присутствует на SO и Q C .

Последний бит данных передается на внешнюю интегральную схему, если она существует. После t 4 все данные из параллельной загрузки удалены.

На часах t 5 мы показываем сдвиг данных 1 присутствует на SI, последовательный ввод.

В:Зачем нужны выводы SI и SO в регистре сдвига?

A:Эти соединения позволяют каскадировать каскады регистра сдвига для получения больших сдвигов, чем те, которые доступны в одном корпусе IC (интегральная схема). Они также позволяют последовательное соединение с другими микросхемами, такими как микропроцессоры.

Давайте подробнее рассмотрим регистры сдвига с параллельным входом и последовательным выходом, доступные в виде интегральных схем, любезно предоставленные Texas Instruments.

Чтобы ознакомиться с полными техническими данными устройства, перейдите по этим ссылкам.

Устройства с параллельным входом / последовательным выходом

- SN74ALS166 8-битный регистр сдвига с параллельным входом / последовательным выходом, синхронная загрузка

- SN74ALS165 8-битный регистр сдвига с параллельным входом / последовательным выходом, асинхронная загрузка

- CD4014B 8-битный регистр сдвига с параллельным входом / последовательным выходом, синхронная загрузка

- SN74LS647 16-разрядный регистр сдвига с параллельным входом / последовательным выходом, синхронная загрузка

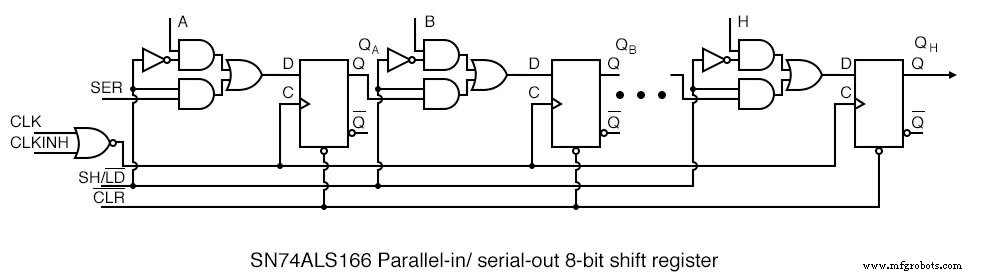

Показанный выше SN74ALS166 является наиболее близким по форме к предыдущим показателям переключателей с параллельным входом / последовательным выходом.

Отметим незначительные изменения в нашем рисунке выше. Прежде всего, это 8 этапов. Мы показываем только три.

Все 8 этапов показаны в таблице данных, доступной по ссылке выше. Производитель маркирует входы данных A, B, C и т. Д. До H.

Элемент управления SHIFT / LOAD называется SH / LD ’. Это сокращение от нашей предыдущей терминологии, но работает так же:параллельная нагрузка, если низкая, сдвиг, если высокая.

Ввод сдвига (вход последовательных данных) - это SER на ALS166 вместо SI. Часы CLK управляются запрещающим сигналом CLKINH.

Если CLKINH высокий, часы заблокированы или отключены. В остальном эта «реальная часть» такая же, как то, что мы рассмотрели подробно.

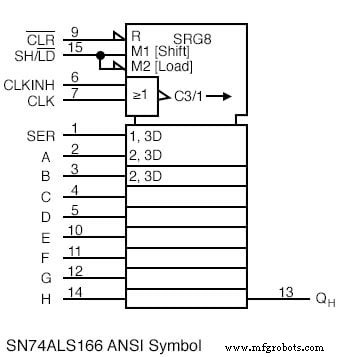

Выше представлен символ ANSI (Американский национальный институт стандартов) для SN74ALS166, как указано в листе технических данных.

Как только мы узнаем, как работает деталь, удобно скрыть детали внутри символа. Есть много общих форм символов.

Преимущество символа ANSI заключается в том, что метки содержат подсказки о том, как работает деталь.

Большой зубчатый блок в верхней части «74ASL166» является контрольной частью символа ANSI. Имеется сброс, обозначенный символом R .

Есть три управляющих сигнала: M1 . (Shift), M2 (Загрузить) и C3 / 1 (стрелка) (заблокированные часы). У часов две функции.

Во-первых, C3 для смещения параллельных данных везде, где появляется префикс 3. Во-вторых, когда M1 утверждается, как указано в 1 из C3 / 1 (стрелка) , данные сдвигаются, как показано правой стрелкой.

Косая черта (/) является разделителем между этими двумя функциями. Этапы с 8 сменами, как указано в заголовке SRG8 , идентифицируются внешними входами A, B, C, в H .

Внутренний 2, 3D указывает эти данные, D , контролируется M2 [Загрузить] и C3 Часы. В этом случае можно сделать вывод, что параллельные данные загружаются синхронно с часами C3 .

Разгонный блок на А является более широким блоком, чем другие, для размещения ввода SER .

Легенда 1, 3D означает, что SER контролируется M1 [Shift] и C3 Часы. Таким образом, мы ожидаем, что данные будут отображаться на уровне SER . при смещении, а не при параллельной загрузке.

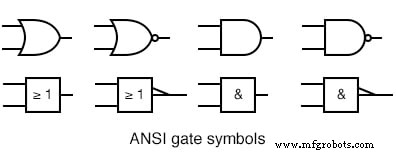

Базовый вентиль ANSI / IEEE прямоугольные символы представлены выше для сравнения с более знакомыми символами фигур чтобы мы могли расшифровать значение символов, связанных с CLKIN H и CLK контакты на предыдущем символе ANSI SN74ALS166.

CLK и CLKINH передают ИЛИ ворота на символе SN74ALS166 ANSI. ИЛИ обозначается => на прямоугольном символе-вставке.

Длинный треугольник на выходе обозначает часы. Если бы там был пузырек со стрелкой, это означало бы сдвиг отрицательного фронта часов (от высокого к низкому).

Поскольку на стрелке часов нет пузыря, регистр сдвигается по положительному фронту тактового сигнала (переход от низкого к высокому).

Длинная стрелка после легенды C3 / 1 указатель вправо означает сдвиг вправо, то есть вниз по символу.

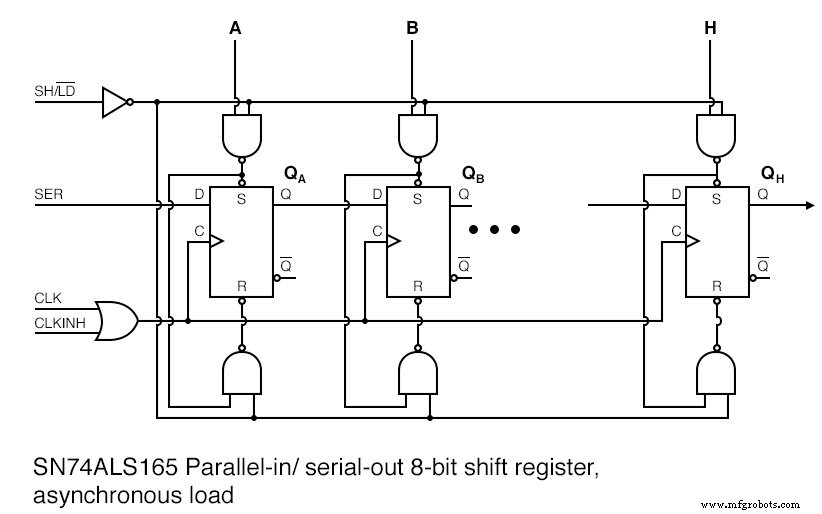

Часть внутренней логики SN74ALS165 с параллельным входом / последовательным выходом и асинхронной загрузкой сдвигового регистра воспроизведена из таблицы данных выше.

См. Ссылку в начале этого раздела для полной диаграммы. До сих пор мы не рассматривали асинхронную загрузку данных.

В первую очередь загрузка осуществляется подачей соответствующих сигналов на Set (предустановка) и Сброс (очистить) входы триггеров.

Верхний NAND ворота питают набор контакты FF, а также каскады в нижнюю NAND ворота, питающие Сброс штифты ФФ.

Нижний NAND гейт инвертирует сигнал, идущий от Set закрепить на сбросе булавка.

Во-первых, SH / LD ’ необходимо потянуть Низко чтобы включить верхний и нижний NAND ворота.

Если SH / LD ’ были на логическом высоком вместо этого инвертор питает логический низкий ко всем NAND ворота вызовут высокий наружу, отпуская «активный минимум» Установить и Сброс пины всех ФФ.

Не было бы возможности загрузить FF.

С SH / LD ’ удерживается низкий , мы можем передать, например, данные 1 к параллельному входу A , который инвертируется в ноль в верхней строке И-НЕ выход затвора, установка FF Q A к 1 .

0 на Set штифт подается на нижнюю NAND ворота, где он превращается в 1 , отпуская кнопку Reset контакт Q A .

Таким образом, данные A =1 устанавливает Q A =1 . Поскольку для этого не нужны часы, загрузка выполняется асинхронно по отношению к часам.

Мы используем регистр сдвига с асинхронной загрузкой, если мы не можем дождаться, пока часы для параллельной загрузки данных, или если неудобно генерировать один тактовый импульс.

Единственная разница в подаче данных 0 к параллельному входу A в том, что он превращается в 1 из верхних ворот, отпуская Set .

Это 1 при Установить преобразуется в 0 у нижних ворот, нажав кнопку Reset до низкого , который сбрасывает Q A =0 .

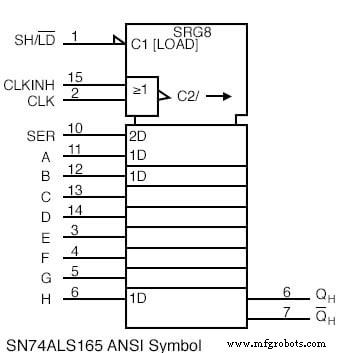

Указанный выше символ ANSI для SN74ALS166 имеет два внутренних элемента управления: C1 . [ЗАГРУЗИТЬ] и C2 часы из ИЛИ функция ( CLKINH, CLK ).

SRG8 говорит 8-ступенчатый переключатель. Стрелка после C2 указывает на смещение вправо или вниз. SER ввод - это функция часов, на что указывает внутренняя метка 2D .

Параллельные вводы данных A, B, C в H являются функцией C1 [ЗАГРУЗИТЬ], обозначенный внутренней меткой 1D .

C1 утверждается, когда sh / LD ’=0 из-за полустрелочного инвертора на входе.

Сравните это с управлением параллельным вводом данных часами предыдущего синхронного ANSI SN75ALS166. Обратите внимание на различия в метках данных ANSI.

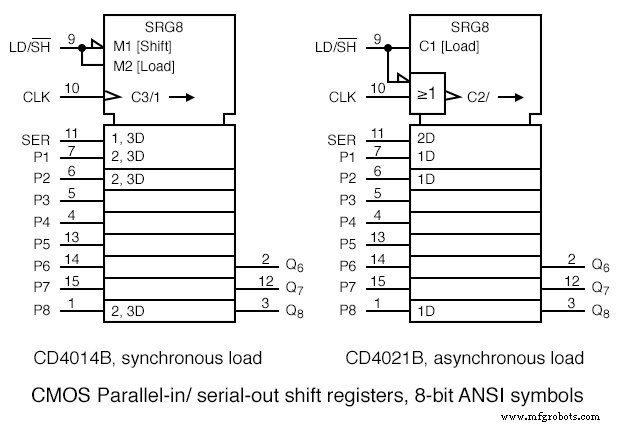

На CD4014B выше M1 утверждается, когда LD / SH ’=0 . M2 утверждается, когда LD / SH ’=1 .

Часы C3 / 1 используется для параллельной загрузки данных в 2, 3D когда M2 активен, что обозначено 2, 3 метки префикса.

Контакты P3 на P7 предполагается, что они имеют внутренние 2, 3 префиксные метки как P2 и P8 . В SER , 1,3D префикс означает, что M1 и часы C3 необходимы для ввода последовательных данных.

Сдвиг вправо происходит, когда M1 активен, как показано на 1 в стрелке C3 / 1 .

CD4021B представляет собой аналогичную часть, за исключением асинхронной параллельной загрузки данных, что подразумевается отсутствием каких-либо 2 префикс в метке данных 1D для контактов P1, P2, до P8.

Конечно, префикс 2 в ярлыке 2D при вводе SER говорит, что данные синхронизируются с этим контактом. Оператор ИЛИ вставка ворот показывает, что часы контролируются LD / SH ’ .

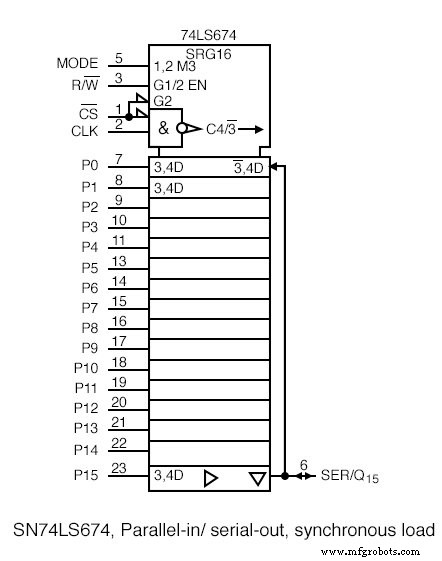

Вышеупомянутая внутренняя метка SN74LS674 SRG 16 обозначает 16-битный регистр сдвига.

РЕЖИМ вход в раздел управления в верхней части символа помечен как 1,2 M3 . Внутренний M3 является функцией ввода РЕЖИМ и G1 и G2 как указано в 1,2 предшествующий M3 .

Базовая метка G обозначает И функция любого такого G входы. Введите R / W ’ имеет внутреннюю метку G1 / 2 EN .

Это включение EN (контролируется G1 И G2 ) для устройств с тремя состояниями, используемых в другом месте символа.

Мы отмечаем, что CS ’ на (контакт 1) является внутренним G2 . Выбор микросхемы CS ’ также является И ed с вводом CLK чтобы дать внутренним часам C4 .

Пузырек внутри стрелки часов указывает на то, что активность находится на отрицательном фронте тактового сигнала (переход от высокого к низкому).

Косая черта (/) - это разделитель, обозначающий две функции для часов. Перед косой чертой: C4 . указывает на контроль над чем-либо с префиксом 4 .

После косой черты значок 3 ’(стрелка) указывает на смещение. 3 ’ из C4 / 3 ’ подразумевает смещение, когда M3 деактивирован ( MODE =0 ). Длинная стрелка указывает на сдвиг вправо (вниз).

Спустившись ниже раздела управления в раздел данных, мы видим внешние входы P0-P15 . , штифты (7-11, 13-23).

Префикс 3,4 внутренней метки 3,4D указывает, что M3 и часы C4 контролировать загрузку параллельных данных.

D означает данные. Предполагается, что эта метка применяется ко всем параллельным входам, хотя явно не записана.

Найдите ярлык 3 ’, 4D . справа от P0 (pin7) этап. Дополняемый - 3 указывает, что M3 =MODE =0 входы (смещения) SER / Q 15 (pin5) по часам, ( 4 3 ’, 4D), что соответствует часам C4 .

Другими словами, при MODE =0 , мы сдвигаем данные в Q 0 от последовательного входа (вывод 6). Все остальные этапы сдвигаются вправо (вниз) по часам.

При перемещении в нижнюю часть символа треугольник, указывающий вправо, указывает на буфер между Q и выходной штифт.

Треугольник, указывающий вниз, указывает на устройство с тремя состояниями. Ранее мы заявляли, что трехстороннее состояние контролируется включением EN , что на самом деле является G1 И G2 из раздела управления.

Если R / W =0 , трехступенчатое состояние отключено, и мы можем сдвинуть данные в Q 0 через SER (вывод 6), деталь, которую мы опускали выше. Нам действительно нужен MODE =0, R / W ’=0, CS’ =0

Внутренняя логика SN74LS674 и таблица, суммирующая работу сигналов управления, доступны по ссылке в маркированном списке в верхней части раздела.

Если R / W ’=1 , тристатус включен, Q 15 заменяет SER / Q 15 (вывод 6) и рециркулирует до Q 0 этап через правый провод к 3 ’, 4D .

Мы предположили, что CS ’был низким, что дало нам часы C4 / 3’ и G2 на EN . в состоянии три состояния.

Практическое применение

Регистр сдвига с параллельным входом и выходом предназначен для считывания данных в микропроцессор.

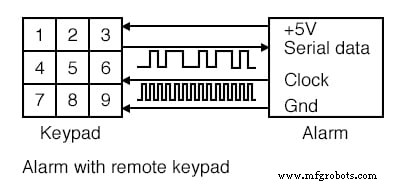

Вышеуказанная сигнализация управляется удаленной клавиатурой. Блок сигнализации подает + 5 В и заземление на удаленную клавиатуру для ее питания.

Сигнал тревоги считывает удаленную клавиатуру каждые несколько десятков миллисекунд, отправляя часы сдвига на клавиатуру, которая возвращает последовательные данные, показывающие состояние клавиш, через регистр сдвига параллельного ввода / последовательного вывода.

Таким образом, мы читаем девять клавишных переключателей с четырьмя проводами. Сколько проводов потребовалось бы, если бы нам пришлось запустить цепь для каждого из девяти ключей?

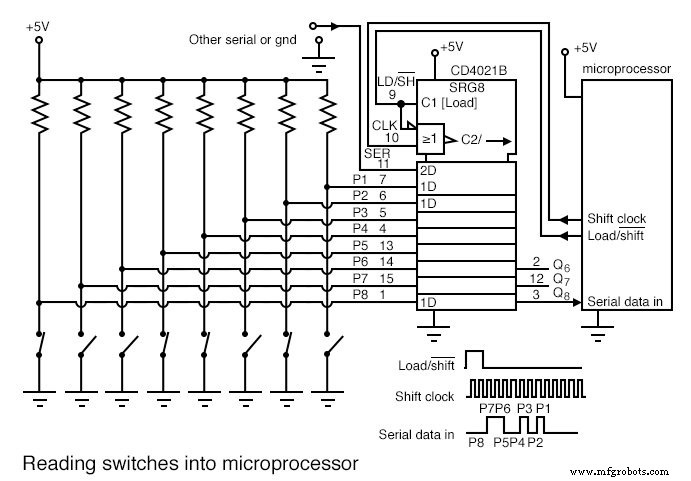

Практическое применение сдвигового регистра с параллельным входом / последовательным выходом - считывание замыканий многих переключателей в микропроцессор всего на нескольких выводах.

Некоторые микропроцессоры начального уровня имеют только 6 контактов ввода / вывода, доступные на 8-контактном корпусе.

Или, возможно, мы использовали большинство контактов на 84-контактном корпусе. Мы можем уменьшить количество проводов, проходящих вокруг печатной платы, машины, транспортного средства или здания.

Это повысит надежность нашей системы. Сообщается, что производители, сократившие количество проводов в автомобиле, производят более надежный продукт.

В любом случае для считывания 8-битных данных с переключателей на рисунке выше требуется только три контакта микропроцессора.

Мы выбрали асинхронное загрузочное устройство CD4021B, потому что с его помощью легче контролировать загрузку данных, не генерируя единственные часы параллельной загрузки.

Параллельные входы данных сдвигового регистра подтягиваются до +5 В с помощью резистора на каждом входе.

Если все переключатели разомкнуты, все 1 s будет загружен в регистр сдвига, когда микропроцессор перемещает LD / SH ’ линия от минимума к максимуму, а затем обратно вниз в ожидании сдвига.

При любом замыкании переключателя будет применяться логика 0 . s на соответствующие параллельные входы. Шаблон данных в P1-P7 будет загружен параллельно с помощью LD / SH ’=1 генерируется программным обеспечением микропроцессора.

Микропроцессор генерирует импульсы сдвига и считывает бит данных для каждого из 8 битов.

Этот процесс может выполняться полностью с помощью программного обеспечения, или более крупные микропроцессоры могут иметь один или несколько последовательных интерфейсов для более быстрого выполнения задачи с помощью оборудования.

Если LD / SH ’=0 , микропроцессор выдает сообщение 0 на 1 переход на Сдвиг линии часов , затем считывает бит данных в Последовательные данные в линия. Это повторяется для всех 8 битов.

SER Линия сдвигового регистра может управляться другой идентичной схемой CD4021B, если необходимо прочитать больше контактов переключателя.

В этом случае микропроцессор генерирует 16-сдвиговые импульсы. Скорее всего, им будет управлять что-то еще, совместимое с этим форматом последовательных данных, например аналого-цифровой преобразователь, датчик температуры, сканер клавиатуры, последовательное постоянное запоминающее устройство.

Что касается замыкания выключателя, то это могут быть концевые выключатели на тележке машины, датчик перегрева, герконовый магнитный переключатель, дверной или оконный выключатель, реле давления воздуха или воды или твердотельный оптический прерыватель.

СВЯЗАННЫЕ РАБОЧИЕ ТАБЛИЦЫ:

- Таблица регистров сдвига

Промышленные технологии

- Сетевые протоколы

- Почему цифровой?

- Микропроцессоры

- Данные операционного усилителя

- Преобразование типов Python и приведение типов

- Производство на основе данных здесь

- Использование ваших данных

- Что такое Интернет вещей?

- Цифровизация производственных объектов

- Большие данные против искусственного интеллекта