Краткое введение в языки Verilog и HDL

Введение:

В этой статье мы познакомим вас с VHDL и Verilog. Мы также изучим базовую структуру модуля Verilog и познакомимся с типом данных Verilog «wire» и его векторной формой. Мы также расскажем вам об основных различиях между Verilog и VHDL.

Что такое Verilog?

Verilog – это язык описания оборудования (HDL), стандартизованный как IEEE 1364. Чаще всего он используется для описания электронных схем и систем, используемых при проектировании и проверке цифровых схем.

Что такое VHDL?

VHDL также представляет собой тип языка описания оборудования (HDL), который используется в автоматизации проектирования электроники для описания поведения и структуры электронных систем и особенно подходит в качестве языка для описания структуры и поведения конструкций цифрового электронного оборудования, а также обычные цифровые схемы.

Нужны ли мне и Verilog, и VHDL?

Прежде чем мы продолжим, давайте обсудим, нужны ли нам оба этих языка? Оба они являются мощными инструментами, используемыми при проектировании сложных цифровых схем, но вы можете освоить тот, который хотите использовать. Однако вы должны иметь базовое понимание обоих языков.

Эволюция Verilog

Verilog был разработан в 1984 году компанией Gateway Design Automation. В 1987 году VHDL стал стандартом IEEE, а Verilog вышел на сцену к 1995 году. Сегодня оба они являются мощными HDL (языками описания оборудования). Слово «Verilog» происходит от слов «проверка» и «логика». Это связано с тем, что язык был первым, который использовался в качестве инструмента моделирования и проверки.

Теперь мы обсудим некоторые концепции Verilog.

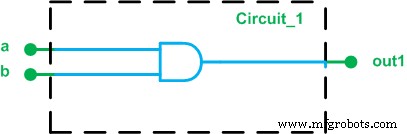

Пример 1:

В этом примере давайте напишем код Verilog для схемы, показанной ниже.

Показаны два входа и один выход, а ширина портов составляет один бит. Схема показывает функцию И от двух входов, приводящую к выходу на порте out1. Описание Verilog может быть показано как:

Строки 1 и 8:

Ключевые слова «модуль» и «конечный модуль» используются для указания строк между ними, описывающих Circuit_1.

Строки со 2 по 6:

Эти строки определяют интерфейс Circuit_1 с его окружением. Ключевые слова «вход» и «выход» показывают порты ввода и вывода. После этого ключевое слово «провод» указывает тип данных Verilog, который представляет физический провод в проекте. В нашем модуле три провода a, b и out1.

Строка 7:

Строка описывает функциональность И схемы с побитовым оператором И ‘&’. Ключевое слово «назначить; используется для размещения a и b на выходном порту. Это также известно как непрерывное присваивание, потому что оно всегда активно всякий раз, когда выражение изменяется в правой части, левая часть переоценивается, т. е. его выходные данные постоянно обновляются.

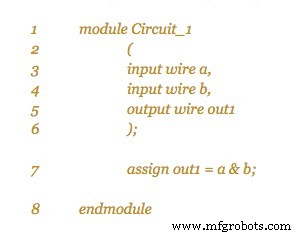

Сравнение примера 1 с кодом VHDL:

На рисунке ниже показаны описания Verilog и VHDL для модуля Circuit_1.

В VHDL мы должны включить некоторые библиотеки, которые определяют типы данных и операторы. Поэтому код VHDL является более описательным. Однако в некоторых случаях это выгодно, например, при моделировании систем более высокого уровня.

Система Verilog с четырьмя значениями:

В типах данных Verilog используются четыре значения:

- 0:низкий уровень логики/ложь

- 1:высокий уровень логики/правда

- z:для состояния с высоким импедансом (также используется для описания вывода буфера с тремя состояниями)

- x:неизвестное значение

Тип данных VHDL std_logic может принимать девять различных значений, но обычно используются значения «0», «1», «Z» и «-» («-» означает неизвестное значение).

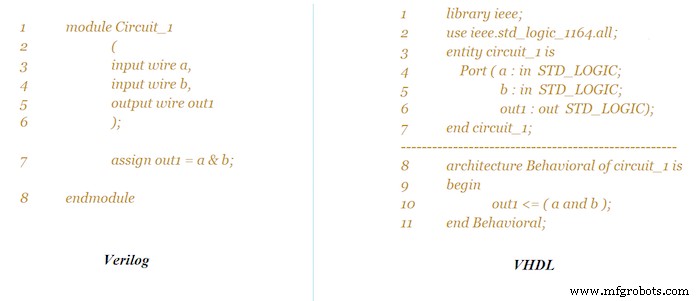

Пример 2:

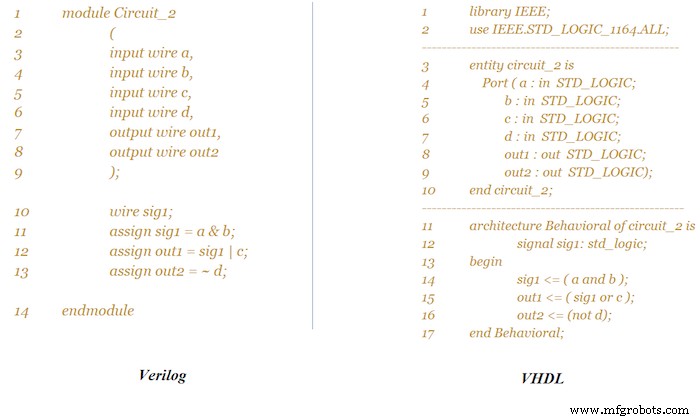

В следующем примере давайте напишем код Verilog для схемы (Circuit_2), показанной на рисунке ниже.

Следующий код Verilog описывает показанную схему:

Используемые элементы аналогичны тем, что использовались в нашем предыдущем примере, однако внутренний сигнал определен в строке 10. Ключевое слово «провод» указывает тип данных этого соединения. Побитовый оператор «~» используется для операций НЕ и «|» для операций ИЛИ. Побитовый оператор «^» используется для операции XOR.

На следующем рисунке показаны описания Verilog и VHDL для модуля Circuit_2, чтобы вы могли наблюдать различия.

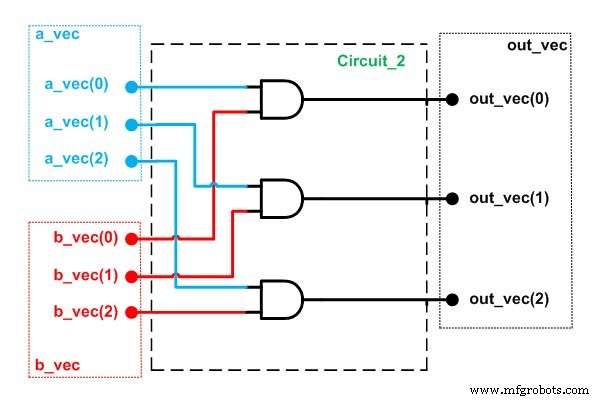

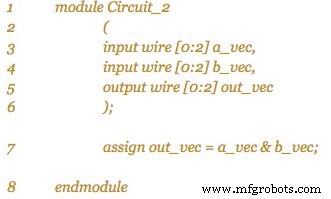

Пример 3:

В нашем третьем и последнем примере мы дадим код Verilog для схемы, показанной на следующем рисунке: Вы заметите, что красный и синий входные порты объединены оператором AND. Результат показывает выходной порт. Мы можем сгруппировать сигналы и рассматривать их как вектор, что сделает наш код компактным и читабельным. Мы можем описать приведенную выше схему, используя код Verilog. Мы также можем легко расширить код из листинга 1, чтобы описать эту схему.

Вы заметите, что красный и синий входные порты объединены оператором AND. Результат показывает выходной порт. Мы можем сгруппировать сигналы и рассматривать их как вектор, что сделает наш код компактным и читабельным. Мы можем описать приведенную выше схему, используя код Verilog. Мы также можем легко расширить код из листинга 1, чтобы описать эту схему.

Имейте в виду, что диапазон индексов векторов может быть как возрастающим, как показано ([0:2]), так и нисходящим ([2:0]). Убывающий формат обычно менее подвержен ошибкам и может использоваться вместо него.

Промышленные технологии

- Введение в люверсы и принципы их работы

- Цепочка поставок и машинное обучение

- Кевлар 101:что это такое и каковы преимущества?

- Симбиоз электронной коммерции и кирпича и раствора

- Колеса на шасси крутятся и крутятся… Не

- Краткое руководство по типам соединений насосов

- В чем разница между Индустрией 4.0 и Индустрией 5.0?

- Много типов полиуретана и для чего они используются

- Что такое фрезерный станок и для чего он нужен?

- Понимание испытаний на прочность:измерение предельных значений основных материалов и деталей