Xilinx повышает производительность RFSoC с помощью жесткого IP-адреса цифрового внешнего интерфейса для радиостанций 5G

Xilinx анонсировала свое цифровое интерфейсное устройство Zynq RFSoC (DFE), предназначенное для развертываний 5G New Radio (NR). Основываясь на архитектуре Zynq UltraScale, Zynq RFSoC DFE расширяет семейство Xilinx RFSoC за счет жесткой IP-реализации вычислительно-ресурсоемких функций, необходимых для эффективной поддержки 5G NR, а также устаревшего 4G в новых радиоблоках (RU) 5G.

При всем своем потенциале 5G ставит перед разработчиками инфраструктуры 5G множество задач. Хотя разработчики смартфонов и других мобильных устройств могут выбирать из постоянно растущего набора микросхем 5G, различные требования, связанные с широким спектром возможностей 5G, обычно требуют более специализированных решений.

В то время как версия 15 3GPP заложила основу для 5G NR с акцентом на расширенную широкополосную мобильную связь (eMBB), в версии 16 ранее в этом году 5G были расширены до новых типов коммуникационных услуг, связанных с сверхнадежностью. Связь с малой задержкой (URLLC) и массовая связь типа машины (mMTC). URLLC удовлетворяет потребность в минимальной задержке ответа, необходимой для критически важных приложений, таких как промышленная автоматизация, удаленная хирургия и транспорт, в то время как mMTC поддерживает крупномасштабное развертывание интеллектуальных устройств с высокой плотностью размещения в таких приложениях, как умные города и умные предприятия. В будущих выпусках 3GPP 5G будет по-прежнему расширяться за счет таких возможностей, как NR MIMO (множественный вход и множественный выход), динамическое совместное использование спектра, усовершенствования URLLC и другие в версии 17, а также расширенная поддержка конкретных областей приложений в версии 18.

Используя возможности 5G, такие как виртуализация сетевых функций (NFV) и сегментирование сети, поставщики решений 5G могут предоставлять специализированные сети, способные предоставлять уникальное сочетание услуг, необходимых для каждого приложения и клиента. Тем не менее, выполнение обещания широкой гибкости сетей 5G зависит от наличия устройств, способных предложить подходящее сочетание производительности и гибкости, а также энергоэффективности.

«В связи с потребностями рынка в развитии 5G интегрированные радиочастотные решения должны быть адаптированы к будущим стандартам», - сказал Лиам Мэдден, исполнительный вице-президент и генеральный менеджер Xilinx 'Wired and Wireless Group , в заявлении. «Zynq RFSoC DFE обеспечивает оптимальный баланс между адаптируемостью и фиксированной функцией IP».

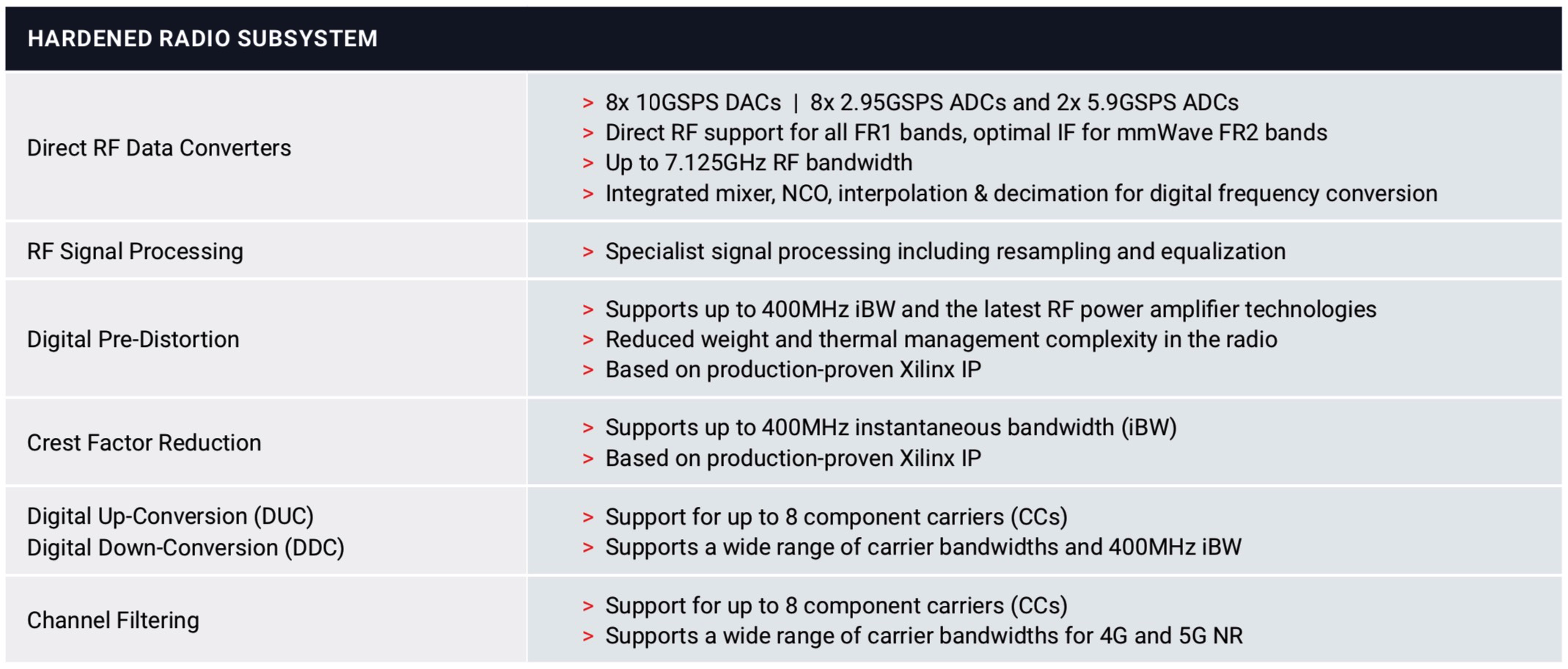

Zynq RFSoC DFE встраивает жесткий IP-адрес, который реализует базовые функции, необходимые для сигнальных трактов 5G RU (рисунок 1).

щелкните, чтобы просмотреть изображение в полном размере

Рис. 1. Жесткий IP-адрес Zynq RFSoC DFE поддерживает широкий спектр возможностей обработки, необходимых для 5G NR, а также для устаревших радиостанций 4G. (Источник:Xilinx)

Поскольку ядро жесткого IP DFE занимает меньше места, чем эквивалентная реализация мягкого IP в более раннем устройстве Zynq RFSoC Gen 3, новое устройство может поддерживать больше ядер DFE, что увеличивает производительность вычислений DFE. и снижение энергопотребления по сравнению с более ранним устройством. В результате Zynq RFSoC DFE может достичь как минимум 2-кратной производительности обработки DFE на ватт по сравнению с полностью используемым устройством Zynq RFSoC Gen 3, согласно Xilinx.

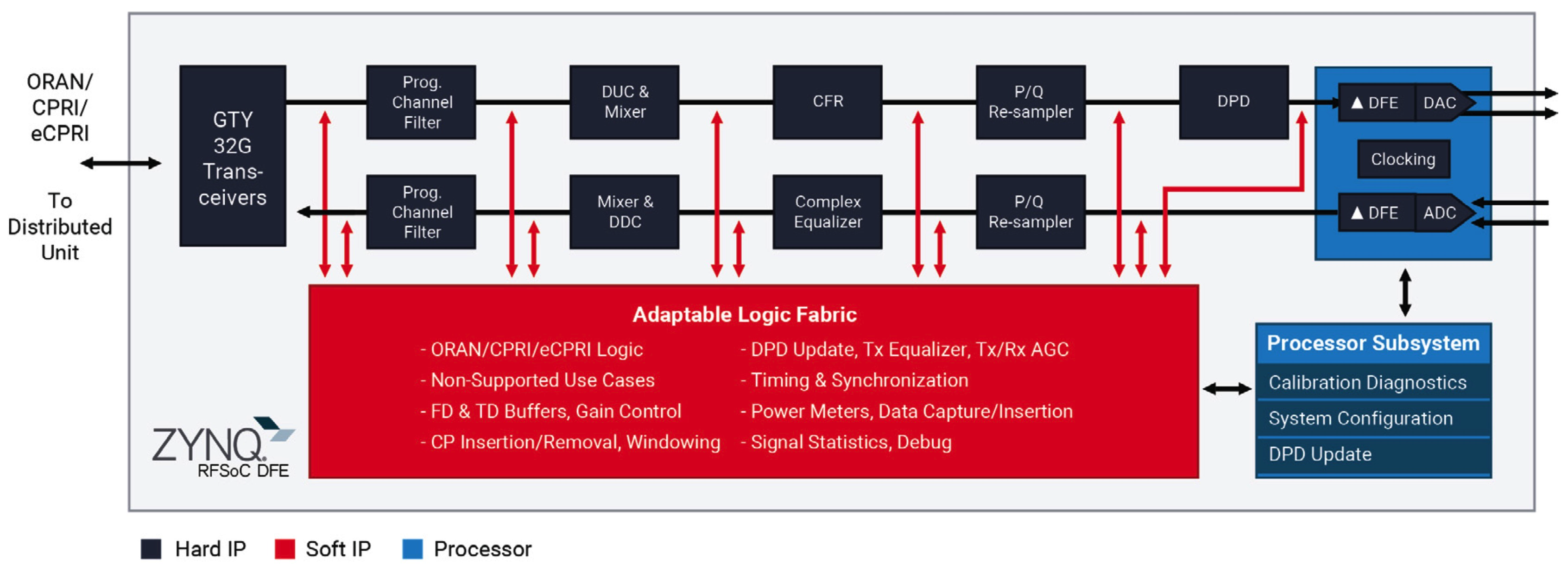

В то же время разработчики могут изменять путь прохождения сигнала, минуя жесткие IP-блоки или вставляя свои собственные функции, реализованные в логической матрице (рисунок 2).

щелкните, чтобы просмотреть изображение в полном размере

Рис. 2. Функциональная архитектура Zynq RFSoC DFE объединяет жесткий IP, логическую матрицу и подсистему процессора. (Источник:Xilinx)

Проектная документация и поддержка Zynq RFSoC DFE доступны клиентам с ранним доступом, поставки ожидаются в первой половине 2021 года. Для получения дополнительной информации посетите страницу продукта Xilinx RFSoC DFE. Xilinx также предоставит дополнительную информацию об устройстве в рамках своего виртуального мероприятия 5G 18-19 ноября.

Встроенный

- Xilinx расширяет портфель Zynq UltraScale + RFSoC до полной поддержки спектра ниже 6 ГГц

- Cadence:Tensilica ConnX B20 DSP повышает производительность до 30 раз для связи 5G

- Renesas:решение функциональной безопасности RX с сертификацией программного обеспечения SIL3 для промышленного об…

- Renesas:микроконтроллеры RX72M с поддержкой EtherCAT для промышленных приложений

- MCU ST:STM32H7 сочетают в себе двухъядерную производительность и широкую интеграцию функций

- SoC повышает производительность носимых устройств

- Lanner:оптимизированное для виртуализации решение с многоядерным процессором

- Portwell:Mini-ITX на базе семейства Intel Core i с производительностью до шести ядер

- Глобальные индикаторы обслуживания, производительности

- Блог:медицинские носимые устройства с отличными характеристиками