Детерминизм фазы включения:использование многокристальной синхронизации

Интеграция нескольких блоков цифровой обработки сигналов (DSP), широкополосных цифро-аналоговых преобразователей (ЦАП) и широкополосных аналого-цифровых преобразователей (АЦП) в одном монолитном кристалле теперь позволяет разгрузить энергоемкие ресурсы FPGA для позволяют использовать платформы с меньшим размером занимаемой площади, меньшим энергопотреблением и увеличенным количеством каналов, которые могут выполнять выборку с более высокой скоростью, чем это было возможно ранее. Наряду с этой новой возможностью появляются новые алгоритмы многокристальной синхронизации (MCS) в этих интегральных схемах (IC), которые позволяют пользователям достичь известной (детерминированной) фазы для всех каналов при питании системы или иным образом внесении изменений в программное обеспечение системы. Таким образом, эта детерминированная фаза упрощает более широкие алгоритмы калибровки на уровне системы, необходимые для достижения синхронизации всех каналов на выходе или входе во входные сети, подключенные к этим ИС. В этой статье представлены экспериментальные результаты, демонстрирующие эту возможность MCS при использовании 16-канальной платформы приемника / передатчика, состоящей из нескольких микросхем дигитайзера, источников синхронизации и цифровых интерфейсов.

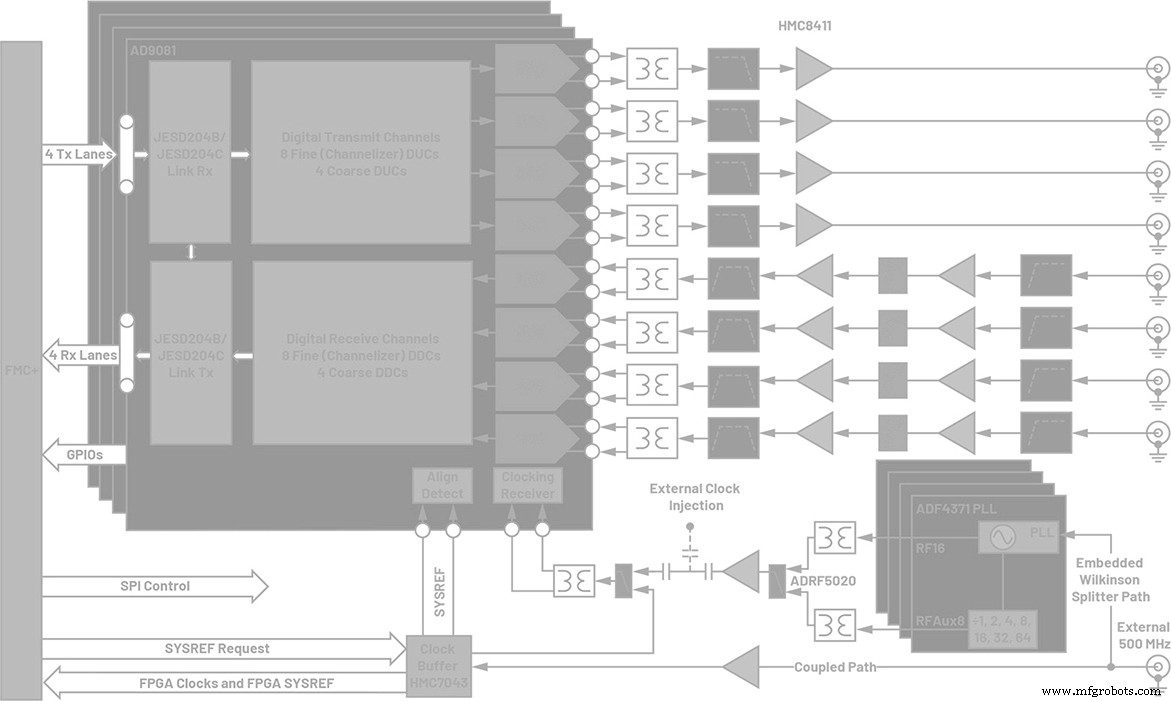

Блок-схема системы высокого уровня

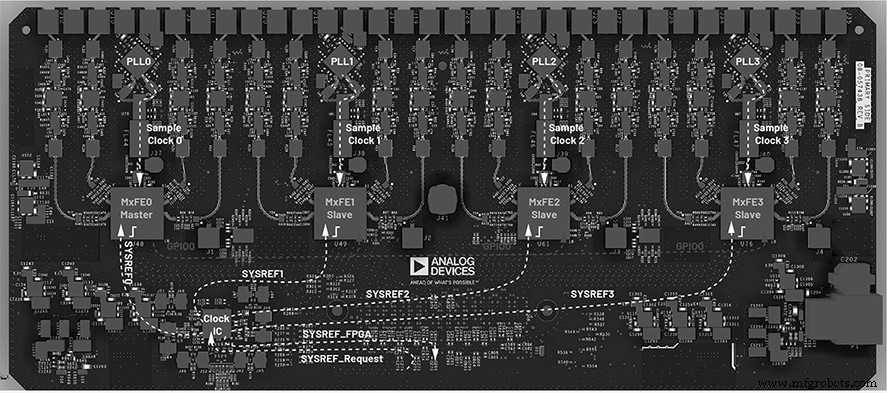

Блок-схема системы, используемой для этого теста, показана на рисунке 1 и состоит из четырех интегрированных ИС ЦАП / АЦП / ЦОС, каждая из которых состоит из четырех ЦАП на 12 GSPS, четырех АЦП на 4 GSPS и 12 цифровых преобразователей с повышением частоты (DUC) и 12 цифровых преобразователей частоты. блоки понижающего преобразователя (DDC).

щелкните, чтобы просмотреть изображение в полном размере

Рис. 1. Блок-схема высокого уровня системы, используемой для демонстрации MCS и алгоритмов многоканальной калибровки. (Источник:Analog Devices)

DUC / DDC допускают преобразование частоты и / или интерполяцию / децимацию в цифровой области. Используя один опорный тактовый сигнал 500 МГц, вводимый на плату, затем используется буфер тактового сигнала с синхронизацией опорного сигнала для генерации системных опорных сигналов, необходимых для MCS, а также тактовых импульсов, необходимых для цифрового интерфейса к процессору основной полосы частот (BBP). Система также содержит четыре отдельных синтезатора с фазовой автоподстройкой частоты (ФАПЧ), которые генерируют источники 12 ГГц, необходимые для синхронизации каждой оцифрованной ИС от общего опорного сигнала. К каждому выходу / входу дигитайзера присоединяется ВЧ-интерфейс, который создает отфильтрованный и усиленный сигнал на / из РЧ-разъемов с периферийным выходом. Реализовано полное решение по распределению мощности. Все напряжения, необходимые для системы, генерируются от одного источника 12 В. Все передаваемые сигналы распространяются по нижней части платы, тогда как все принимаемые сигналы распространяются по верхней части платы для достижения наиболее оптимальной межканальной развязки.

Древовидная структура часов подмассивов

Как упоминалось ранее, дерево тактовой частоты подматрицы состоит из одного опорного источника 500 МГц, который разделяется и отправляется на опорные входы четырех отдельных ИС синтезатора ФАПЧ, как показано выше на рисунке 1. Этот сигнал 500 МГц также связан с усилением на 10 дБ. , и отправляется в другую ИС буфера синхронизации, которая отвечает за создание системных ссылок (SYSREF) и тактовых импульсов BBP, необходимых для цифрового интерфейса. Это дерево часов преследует три цели:

- Позволяет индивидуальным задержкам SYSREF канала исправлять любые несоответствия длины трассы между IC.

- Позволяет индивидуальную регулировку фазы ФАПЧ / синтезатора и, следовательно, обеспечивает синхронизацию между соответствующими источниками тактовых импульсов ИС дигитайзера, чтобы компенсировать любые наведенные температурные градиенты в системе.

- Позволяет пользователю выполнить необходимые требования по настройке и удержанию для оцифрованных ИС.

ИС дерева синхронизации выбраны, чтобы продемонстрировать, что различные аномалии компоновки платы могут быть исправлены программно и / или аппаратно с помощью цифровых и аналоговых блоков задержки, присутствующих в этих микросхемах. В конечном итоге результатом является дерево тактовых импульсов, которое может предоставить импульс SYSREF всем требуемым микросхемам в пределах одного тактового цикла выборки каждой из этих микросхем.

Цифровой интерфейс с процессором основной полосы частот

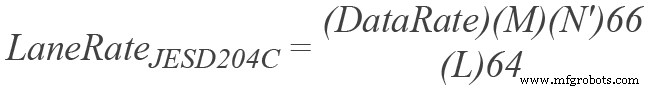

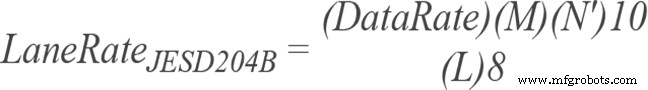

Каждая из четырех оцифровывающих ИС устанавливает цифровой интерфейс связи JESD204B или JESD204C с BBP. 1,2 Этот интерфейс отвечает за передачу кодов АЦП и ЦАП по физическим трассам (SERDES) на BBP и обратно. Количество дифференциальных трассировок SERDES, используемых в этом интерфейсе, называется количеством дорожек (L) для этого канала. Разрядность преобразователя, передаваемая по каналу связи, рассматривается как N ’. Количество канальных трактов данных, также придуманных виртуальных преобразователей, помечено как M. Результаты, показанные в этой статье, используют канал JESD204C с M =16, N '=16, L =4 для каналов на стороне ЦАП и M =8. , N '=16, L =2 для звеньев на стороне АЦП.

Скорость, с которой данные передаются и принимаются между дигитайзером IC и BBP, называется скоростью полосы движения. Блоки DSP на кремнии (то есть DDC / DUC) позволяют пользователю выполнять выборку цифровых преобразователей со скоростью, отличной от скорости передачи данных по физическим каналам. По существу, скорость передачи зависит от скорости передачи данных, прореженных / интерполированных в цифровом виде, для каждого пути данных. Для этой работы использовалась скорость I / Q данных 250 MSPS. Для интерфейса JESD204C скорость полосы определяется как:

тогда как для интерфейса JESD204B скорость полосы определяется как:

Результаты, показанные в этой статье, используют скорость передачи 16,5 Гбит / с для каналов JESD204C на стороне АЦП и на стороне ЦАП.

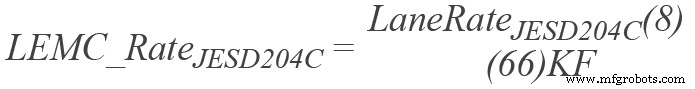

Каждая ссылка JESD204B / JESD204C может быть установлена в разных подклассах. Эти подклассы разделяются в зависимости от того, требуется ли многокристальная синхронизация или детерминированная задержка. Для этой работы показанные данные используют режим подкласса 1 JESD204C и, следовательно, используют сигналы SYSREF для выравнивания частей цифровых данных, передаваемых по множественным каналам, присутствующим в системе. В частности, в этом режиме подкласса 1 JESD204C сигналы SYSREF используются для выравнивания локального расширенного многоблочного счетчика (LEMC), который передает со скоростью:

где F - количество октетов на кадр JESD на полосу, а K - количество кадров на один мультикадр. Для этой работы F =8 и K =32, поэтому используется скорость LEMC 7,8125 MSPS. Знание этой скорости LEMC важно, поскольку любая успешная процедура MCS должна продемонстрировать, что радиочастотные частоты, которые не являются целым числом, кратным скорости LEMC, могут обеспечить детерминированную фазу включения питания.

Метод синхронизации с несколькими микросхемами

В этой системе широкополосные интегрированные ИС АЦП / ЦАП обеспечивают схему MCS, чтобы обеспечить детерминированную фазу включения питания на всех каналах передачи и приема RF, даже при использовании блоков DUC / DDC DSP в ИС. Эта функция MCS позволяет пользователям заполнять справочную таблицу (LUT) во время заводской калибровки, чтобы минимизировать время простоя. Любая успешная демонстрация MCS должна обеспечивать детерминированную фазу по всем каналам в системе для каждой попытки РЧ частоты, температурного градиента и цикла питания системы.

Интегрированные ИС АЦП / ЦАП содержат 12 блоков DUC и 12 блоков DDC, как показано выше на рисунке 1. Каждый из этих блоков содержит подблок интерполяции (DUC) или децимации (DDC) для изменения скорости передачи данных цифрового входного сигнала ЦАП или Выходной сигнал АЦП оцифрован соответственно. В каждом DUC / DDC также содержится сложный генератор с числовым программным управлением (NCO), который обеспечивает преобразование частоты в цифровой области. Каждый из этих NCO может выполнять комплексную регулировку фазы в реальном времени, так что цифровой сигнал между ЦАП / АЦП и BBP может быть изменен для компенсации различных несоответствий длины трассы SERDES.

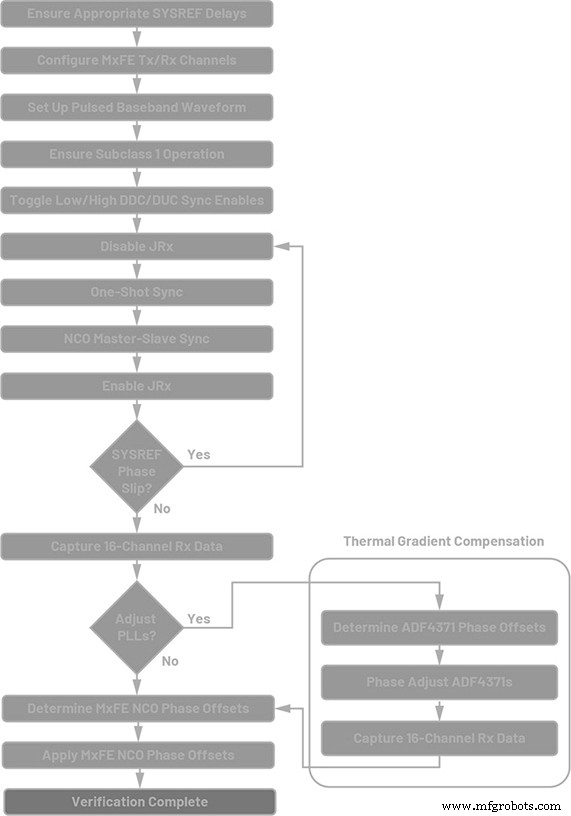

Функция MCS для этих ИС АЦП / ЦАП отвечает за достижение фазового детерминизма во всех аспектах канала данных ИС дигитайзера. Рабочий процесс для достижения MCS показан на рисунке 2.

щелкните, чтобы просмотреть изображение в полном размере

Рис. 2. Рабочий процесс MCS включает отдельные функции, которые выравнивают разные части канала данных. (Источник:Analog Devices)

Алгоритм MCS можно разделить на две отдельные функции:

- Однократная синхронизация:эта функция отвечает за выравнивание данных основной полосы частот, отправляемых по физическим каналам всех микросхем дигитайзера в системе подмассивов.

- Синхронизация главного-подчиненного NCO:эта функция отвечает за выравнивание всех NCO во всех различных ИС дигитайзера в системе субмассивов.

Функция однократной синхронизации сначала требует, чтобы пользователь определил параметры связи JESD (такие как M, N ’, L и т. Д.), А затем сконфигурировал логику синхронизации для любого желаемого усреднения SYSREF (при использовании непрерывных импульсов SYSREF). Кроме того, желаемые задержки LEMC могут использоваться для принудительного создания LEMC с определенной задержкой после фронта SYSREF. После этого пользователь включает бит однократной синхронизации в каждой ИС дигитайзера и затем запрашивает, чтобы импульсы SYSREF были отправлены на каждую ИС в течение одного тактового цикла, как показано на рисунке 3.

щелкните, чтобы просмотреть изображение в полном размере

Рис. 3. Алгоритм MCS использует сигналы SYSREF для реализации однократной синхронизации и сигналы GPIO для реализации синхронизации главного-подчиненного NCO для достижения детерминированной фазы. (Источник:Analog Devices)

Для этой системы аналоговые точные задержки были введены в ИС тактового буфера, чтобы разрешить синхронные SYSREF для всех ИС дигитайзера. Последующая проверка может быть выполнена для подтверждения успешного выполнения процесса однократной синхронизации путем опроса регистров в каждой ИС, которые предоставляют информацию о фазовом соотношении между сигналом SYSREF и границей LEMC каждой связи ИС.

После измерения стабильной фазы (то есть, когда регистр фазы SYSREF-LEMC покажет 0), пользователь знает, что LEMC всех микросхем дигитайзера выровнены, и затем пользователь может перейти к процессу синхронизации главного-подчиненного NCO. Для этого действия подзадачи, описанные для однократной синхронизации, содержатся в интерфейсе прикладного программирования (API), предоставляемом производителем микросхемы.

Функция синхронизации главный-подчиненный NCO сначала назначает одну из ИС дигитайзера в подмассиве, чтобы она действовала как главный чип, как показано выше на рисунке 3. Все остальные дигитайзеры затем считаются подчиненными ИС. Главная ИС настроена так, что вывод GPIO0 этого устройства настроен как выход и направляется к цепям GPIO0 трех подчиненных ИС дигитайзера. Подчиненные сети GPIO0 настроены как входы. Затем пользователь может выбрать запуск по импульсу SYSREF, по переднему фронту LEMC или по заднему фронту LEMC. Для данных, показанных в этой статье, нарастающий фронт LEMC используется в качестве источника запуска синхронизации NCO master-slave, а сети GPIO маршрутизируются через BBP, а не локально на подмассиве. Затем биты синхронизации DDC переключаются на низкий, а затем на высокий уровень, чтобы активировать алгоритм синхронизации NCO на стороне АЦП. Аналогичным образом бит выравнивания микропроцессора переключается на низкий, а затем на высокий уровень, чтобы активировать алгоритм синхронизации NCO на стороне ЦАП.

Когда запрашивается этот триггер, на следующем нарастающем фронте LEMC ИС ведущего дигитайзера устанавливает высокий выходной сигнал ведущего через свою сеть GPIO0. Этот сигнал распространяется на входы GPIO0 каждого из подчиненных устройств. На следующем краю LEMC все ИС дигитайзера испытывают алгоритм сброса NCO. После этого любые импульсы LEMC игнорируются в отношении алгоритма синхронизации NCO ведущий-ведомый. Как и в случае с однократной синхронизацией, эти подзадачи синхронизации NCO «главный-подчиненный» содержатся в функциях API для простоты использования пользователем.

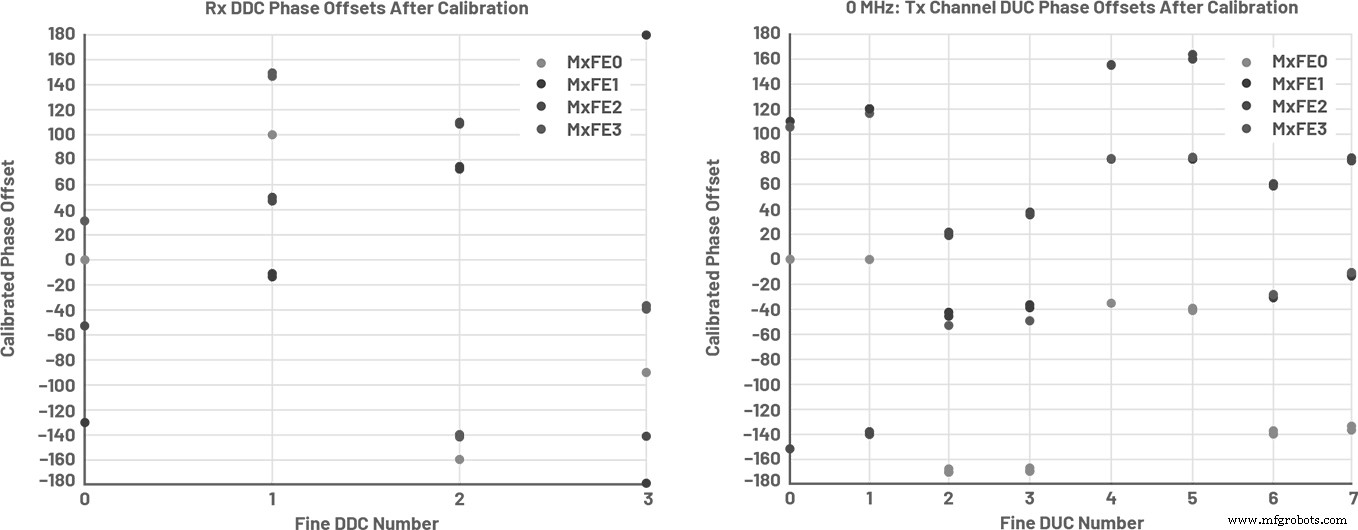

Использование как однократной синхронизации, так и функции синхронизации главный-подчиненный NCO выравнивает оба входа для каждого DDC / DUC таким образом, чтобы смещение выходной фазы каждого канала приема и передачи повторялось после нескольких циклов включения питания, как показано на рисунке 4. Данные на рисунке 4 показаны откалиброванные сдвиги фаз за 100 циклов включения питания (обозначены множеством сплошных точек) для каждого приемно-передающего канализатора, когда система работает в условиях статического температурного градиента во время каждой перезагрузки.

щелкните, чтобы просмотреть изображение в полном размере

Рис. 4. DDC приема (слева) и DUC передачи (справа) правильно выровнены при выполнении алгоритма MCS. (Источник:Analog Devices)

Как видно из множества точек, представленных на этом рисунке, точки каждого цвета для данного DDC / DUC все плотно сгруппированы в одну и ту же позицию после включения и выключения, тем самым отображая детерминированную фазу для этого конкретного канала. Для данных в этом тесте все восемь DUC формирователя каналов использовались на передающей стороне, тогда как только четыре из восьми DDC формирователя каналов использовались. Тем не менее, было подтверждено, что действительно все восемь каналов DDC обеспечивают детерминированную фазу при использовании алгоритма MCS.

Выполнение этого алгоритма при загрузке устанавливает детерминированную фазу для каждого канала, если тактовые импульсы синтезатора ФАПЧ и тактовые импульсы IC SYSREF поддерживают одинаковое фазовое соотношение при загрузке. Однако любая система будет подвергаться температурным градиентам, что может привести к дрейфу тактовой частоты ФАПЧ и может привести к другой фазе включения питания, если ее не компенсировать. Чтобы компенсировать дрейф температурного градиента в системе, эта платформа использует регулировку фазы синтезатора ФАПЧ.

В следующей части этой серии статей мы рассмотрим регулировку фазы синтезатора ФАПЧ, масштабируемость до нескольких подмассивов и алгоритмы калибровки на уровне системы.

Ссылки

1 Дель Джонс. «Учебник по JESD204C:что нового и что есть в нем для вас - часть 1.» Аналоговый диалог , Vol. 53, No. 2, июнь 2019.

2 Дель Джонс. «Учебник по JESD204C:что нового и что есть в нем для вас - часть 2». Аналоговый диалог , Vol. 53, No. 3, июль 2019 г.

Встроенный

- Фазовый сдвиг

- Фаза переменного тока

- Поворот фазы

- С# с использованием

- MACOM представляет новый усилитель со сверхнизким фазовым шумом

- Keysight запускает новую систему тестирования фазового шума

- Использование нескольких микросхем вывода требует тщательного планирования

- Как сгенерировать высокоточный сигнал с помощью ЦАП и специальной печатной платы

- Генератор часов Verilog

- Использование фрезерного станка в качестве токарного станка