Что такое блок управления:компоненты и его конструкция

Блок управления является основным компонентом центрального процессора (ЦП) в компьютерах, который может управлять операциями во время выполнения программы процессором / компьютером. Основная функция блока управления - извлекать и выполнять инструкции из памяти компьютера. Он получает входную инструкцию / информацию от пользователя и преобразует ее в управляющие сигналы, которые затем передаются в ЦП для дальнейшего выполнения. Он включен как часть архитектуры фон Неймана, разработанной Джоном Нейманом. Он отвечает за предоставление сигналов синхронизации и сигналов управления, а также направляет выполнение программы центральным процессором. Он включен как внутренняя часть ЦП в современных компьютерах. В этой статье дается полная информация о блоке управления.

Что такое блок управления?

Компонент, который получает входной сигнал / информацию / инструкцию от пользователя и преобразует в управляющие сигналы для выполнения в ЦП. Он контролирует и направляет основную память, арифметико-логический блок (ALU), устройства ввода и вывода, а также отвечает за инструкции, которые отправляются в ЦП компьютера. Он извлекает инструкции из основной памяти процессора и отправляет их в регистр инструкций процессора, который содержит содержимое регистра.

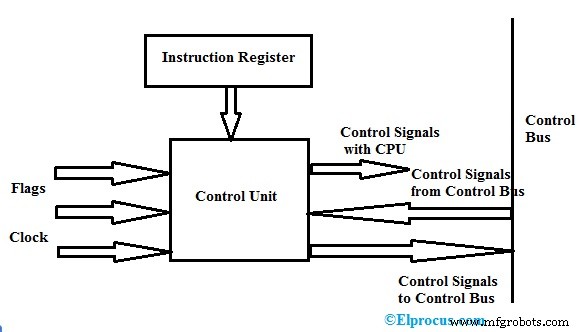

Блок управления преобразует входные данные в управляющие сигналы, а затем отправляет их процессору и направляет выполнение программы. Операции, которые необходимо выполнить, направляются процессором компьютера. В основном центральному процессору (ЦП) и графическому процессору (ГП) требуется блок управления в качестве внутренней части. Блок-схема блока управления показана выше.

Компоненты блока управления

Компонентами этого устройства являются регистры команд, управляющие сигналы внутри ЦП, управляющие сигналы на шину и из нее, шину управления, входные флаги и тактовые сигналы.

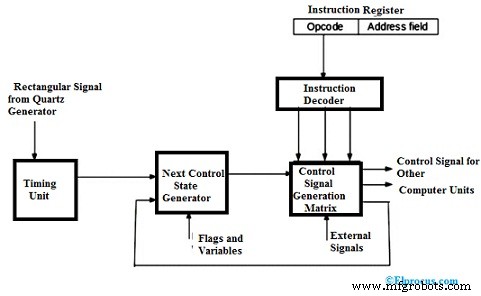

Компонентами аппаратного блока управления являются регистр команд (содержит код операции и поле адреса), блок синхронизации, генератор состояний управления, матрица генерации управляющих сигналов и декодер команд.

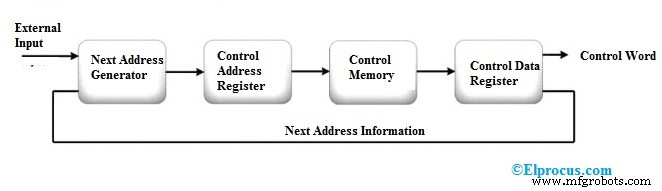

Компоненты программируемого блока управления Micro являются следующим адресом. генератор, регистр адреса управления, память управления и регистр данных управления.

Функции

Функции блока управления включить следующее.

- Он направляет поток последовательности данных между процессором и другими устройствами.

- Он может интерпретировать инструкции и управлять потоком данных в процессоре.

- Он генерирует последовательность управляющих сигналов из полученных инструкций или команд из регистра инструкций.

- Он отвечает за управление исполнительными модулями, такими как ALU, буферы данных и регистры в ЦП компьютера.

- Он может извлекать, декодировать, обрабатывать выполнение и сохранять результаты.

- Он не может обрабатывать и хранить данные.

- Для передачи данных он взаимодействует с устройствами ввода и вывода и управляет всеми блоками компьютера.

Дизайн блока управления

Это можно сделать с помощью двух типов блока управления . которые включают следующее.

- На основе проводной связи

- На основе микропрограмм (одноуровневые и двухуровневые)

Проводной блок управления

Базовая конструкция проводного блока управления показана выше. В этом типе управляющие сигналы генерируются специальной аппаратной логической схемой без каких-либо изменений в структуре схемы. В этом случае сгенерированный сигнал не может быть изменен для выполнения в процессоре.

Основные данные кода операции (код операции команды отправляется в декодер команд для декодирования. Декодер команд - это набор декодеров для декодирования различных типов данных в коде операции. Это приводит к выходным сигналам, которые содержат значения активных сигналов которые подаются на вход генератора матриц для генерации управляющих сигналов для выполнения программы процессором компьютера.

Генератор матриц выдает состояния блока управления и сигналы от процессора (сигналы прерывания). Матрица построена как массив программируемой логики. Управляющие сигналы, генерируемые генератором матрицы, подаются в качестве входных данных в следующую матрицу генератора и комбинируются с синхронизирующими сигналами блока синхронизации, который содержит прямоугольные шаблоны.

Для получения новой инструкции блок управления превращается в начальный этап для выполнения новой инструкции. Блок управления остается на начальном этапе или на первом этапе до тех пор, пока синхронизирующие сигналы, входные сигналы и состояния команд компьютера не изменяются. Изменение состояния блока управления может быть вызвано изменением любого из генерируемых сигналов.

Когда возникает внешний сигнал или прерывание, блок управления переходит в следующее состояние и выполняет обработку сигнала прерывания. Флаги и состояния используются для выбора желаемых состояний для выполнения цикла выполнения инструкции.

В последнем состоянии блок управления выбирает следующую команду и отправляет результат в счетчик программ, затем в регистр адреса памяти, в буферный регистр, а затем в регистр команд для чтения инструкции. Наконец, если последняя инструкция (которая выбирается блоком управления) является инструкцией завершения, то она переходит в рабочее состояние процессора и ждет, пока пользователь не укажет следующую программу.

Микропрограммный блок управления

В этом типе управляющая память используется для хранения управляющих сигналов, которые кодируются во время выполнения программы. Управляющий сигнал не генерируется сразу и не декодируется, потому что микропрограмма хранит адресное поле в управляющей памяти. Весь процесс находится на одном уровне.

Микрооперации выполняются для выполнения микрокоманд в программе. Блок-схема программируемого блока управления Micro показана выше. Как видно из схемы, адрес микрокоманды получается из адресного регистра памяти управления. Вся информация о блоке управления постоянно хранится в управляющей памяти, называемой ПЗУ.

Микрокоманда из управляющей памяти хранится в управляющем регистре. Поскольку микрокоманда имеет форму управляющего слова (содержит двоичные управляющие значения), для обработки данных требуется выполнение 1 или более микроопераций.

Во время выполнения микрокоманды генератор следующего адреса вычисляет следующий адрес микрокоманды и затем отправляет его в регистр адреса управления для чтения следующей микрокоманды.

Последовательность микрокоманд микрокоманды -программа выполняется следующим генератором адресов и действует как микропрограммный секвенсор для получения адреса последовательности, т. е. считывается из управляющей памяти.

Код Verilog для блока управления

Код Verilog для блока управления показан ниже.

`включить« prj_definition.v »

модуль CONTROL_UNIT (MEM_DATA, RF_DATA_W, RF_ADDR_W, RF_ADDR_R1, RF_ADDR_R2, RF_READ, RF_WRITE, ALU_OP1, ALU_OP2, ALU_OPRN, MEM_ADDR, MEM_READ, MEM_WRITE, RF_DATA, RF_DATA, RF_DATA, RF_DATA)

// Выходные сигналы

// Выходные данные для регистрового файла

вывод [`DATA_INDEX_LIMIT:0] RF_DATA_W;

вывод [` ADDRESS_INDEX_LIMIT:0] RF_ADDR_W, RF_ADDR_R1, RF_ADDR_R2;

вывод RF_READ, RF_WRITE;

// Выходы для ALU

output [`DATA_INDEX_LIMIT:0] ALU_OP1, ALU_OP2;

output [` ALU_OPRN_INDEX_LIMIT:0] ALU_OPRN;

// Вывод для памяти

output [`ADDRESS_INDEX_LIMIT:0] MEM_ADDR;

output MEM_READ, MEM_WRITE;

// Входные сигналы

input [`DATA_INDEX_LIMIT:0] RF_DATA_R1, RF_DATA_R2, ALU_RESULT;

input ZERO, CLK, RST;

// Сигнал Inout

inout [`DATA_INDEX_LIMIT:0] MEM_DATA;

// Состояние сетей

wire [2:0] proc_state;

// содержит значение счетчика программы, сохраняет текущую инструкцию, регистр указателя стека

reg MEM_READ, MEM_WRITE;

reg MEM_ADDR;

reg ALU_OP1, ALU_OP2;

reg ALU_OPRN;

reg RF_ADDR_W, RF_ADDR_R1, RF_ADDR_R2;

reg RF_DATA_W;

reg [1:0] состояние, next_state;

PROC_SM state_machine (.STATE (proc_state), CLK (CLK), RST (RST));

always @ (posedge CLK)

begin

if (RST)

state <=RST;

else

state <=next_state;

конец

всегда @ (состояние)

начало

MEM_READ =1’b0; MEM_WRITE =1’b0; MEM_ADDR =1’b0;

ALU_OP1 =1’b0; ALU_OP2 =1’b0; ALU_OPRN =1’b0;

RF_ADDR_R1 =1’b0; RF_ADDR_R2 =1’b0; RF_ADDR_W =1’b0; RF_DATA_W =1’b0;

case (состояние)

`PROC_FETCH:begin

next_state =` PROC_DECODE;

MEM_READ =1’b1;

RF_ADDR_R1 =1’b0; RF_ADDR_R2 =1’b0;

RF_ADDR_W =1’b1;

конец

`PROC_DECODE:begin

next_state =` PROC_EXE;

MEM_ADDR =1’b1;

ALU_OP1 =1’b1; ALU_OP2 =1’b1; ALU_OPRN =1’b1;

MEM_WRITE =1’b1;

RF_ADDR_R1 =1’b1; RF_ADDR_R2 =1’b1;

конец

`PROC_EXE:begin

next_state =` PROC_MEM;

ALU_OP1 =1’b1; ALU_OP2 =1’b1; ALU_OPRN =1’b1;

RF_ADDR_R1 =1’b0;

конец

`PROC_MEM:begin

next_state =` PROC_WB;

MEM_READ =1’b1; MEM_WRITE =1’b0;

конец

`PROC_WB:begin

next_state =` PROC_FETCH;

MEM_READ =1’b1; MEM_WRITE =1’b0;

конец

конечный регистр

конец

endmodule;

module PROC_SM (STATE, CLK, RST);

// список входов

input CLK, RST;

// список выходов

output [2:0] STATE;

// список ввода

input CLK, RST;

// список вывода

output STATE;

reg [2:0] STATE;

reg [1:0] state;

reg [1:0] next_state;

reg PC_REG, INST_REG, SP_REF;

`define PROC_FETCH 3’h0

` define PROC_DECODE 3’h1

`define PROC_EXE 3’h2

` define PROC_MEM 3’h3

`define PROC_WB 3’h4

// инициирование состояния

начальное

begin

state =2’bxx;

next_state =`PROC_FETCH;

end

// сбрасываем обработку сигналов

всегда @ (posedge RST)

begin

state =`PROC_FETCH;

next_state =` PROC_FETCH;

end

всегда @ ( posedge CLK)

begin

state =next_state;

end

всегда @ (state)

begin

if (state ===`PROC_FETCH)

begin

next_state =`PROC_DECODE;

print_instruction (INST_REG);

конец

if (состояние ===`PROC_DECODE)

begin

next_state =` PROC_EXE;

конец

if (состояние ===`PROC_EXE)

begin

next_state =` PROC_MEM;

print_instruction (SP_REF);

конец

if (state ===`PROC_MEM)

begin

next_state =` PROC_WB;

конец

if (состояние ===`PROC_WB)

begin

next_state =` PROC_FETCH;

print_instruction (PC_REG);

конец

конец

задание print_instruction;

input [`DATA_INDEX_LIMIT:0] inst;

reg [5:0] код операции;

reg [4:0] rs;

reg [4:0] rt;

reg [4:0] rd;

reg [ 4:0] Шамт; reg [5:0] функция; рег [15:0] немедленно; reg [25:0] адрес;

начало

// разбираем инструкцию

// R-тип

{opcode, rs, rt, rd, shamt, funct} =inst;

// I-тип

{код операции, rs, rt, немедленный} =inst;

// J-тип

{код операции, адрес} =inst;

$ write (« @% 6dns -> [0X% 08h] «, $ time, inst);

case (код операции) // R-Type

6'h00:begin

case (funct)

6'h20:$ write («add r [% 02d], r [% 02d], r [% 02d];», rs, rt, rd);

6'h22:$ write («sub r [% 02d], r [% 02d], r [% 02d]; », rs, rt, rd);

6'h2c:$ write (« mul r [% 02d], r [% 02d] , r [% 02d]; », rs, rt, rd);

6'h24:$ write (« and r [% 02d], r [% 02d], r [% 02d]; », rs , rt, rd);

6'h25:$ write («или r [% 02d], r [% 02d], r [% 02d];», rs, rt, rd);

6'h27:$ write («nor r [% 02d], r [% 02d], r [% 02d];», rs, rt, rd);

6'h2a:$ write («slt r [% 02d], r [% 02d], r [% 02d]; », rs, rt, rd);

6'h00:$ write (« sll r [% 02d],% 2d, r [ % 02d]; », rs, shamt, rd);

6'h02:$ write (« srl r [% 02d], 0X% 02h, r [% 02d]; », rs, shamt, rd);

6'h08:$ write («jr r [% 02d];», rs);

по умолчанию:$ write («»);

endcase

end

// I-типа

6'h08:$ write («addi r [% 02d], r [% 02d], 0X% 04h;», rs, rt, немедленно);

6'h1d:$ write («muli r [% 02d], r [% 02d], 0X% 04h; », rs, rt, немедленно);

6'h0c:$ write (« andi r [% 02d], r [% 02d], 0X% 04h; », Rs, rt, немедленно);

6'h0d:$ write (« ori r [% 02d], r [% 02d], 0X% 04h; », rs, rt, немедленно);

6'h0f:$ write («lui r [% 02d], 0X% 04h;», rt, немедленно);

6'h0a:$ write («slti r [% 02d], r [% 02d], 0X% 04h; », rs, rt, немедленно);

6'h04:$ write (« beq r [% 02d], r [% 02d], 0X% 04h; », rs, rt , немедленно);

6'h05:$ write («bne r [% 02d], r [% 02d], 0X% 04h;», rs, rt, немедленно);

6'h23:$ write («lw r [% 02d], r [% 02d], 0X% 04h;», rs, rt, немедленно);

6'h2b:$ write («sw r [% 02d], r [% 02d], 0X% 04h; ”, rs, rt, немедленно);

// Тип J

6'h02:$ write («jmp 0X% 07h;», адрес);

6'h03:$ write («jal 0X% 07h;», адрес);

6'h1b:$ write («Push;»);

6'h1c:$ write («pop;»);

по умолчанию:$ write («»);

endcase

$ write (« \ n ”);

end

endtask

end module;

Часто задаваемые вопросы

1). Как работает блок управления?

Работа блока управления заключается в том, чтобы направлять поток данных или инструкций для выполнения процессором компьютера. Он контролирует, управляет и координирует основную память, ALU, регистры, блоки ввода и вывода. Он извлекает инструкции и генерирует управляющие сигналы для выполнения.

2). Что такое контрольная память?

Управляющая память - это обычно RAM или ROM для хранения адреса и данных управляющего регистра.

3). Что такое блок управления Wilkes?

Последовательная и комбинационная схемы проводного блока управления заменены блоком управления Wilkes. Он использует блок памяти для хранения последовательностей инструкций микропрограммы.

4). Что такое проводной блок управления?

Проводной блок управления генерирует управляющие сигналы, переходя из одного состояния в другое в каждом тактовом импульсе без каких-либо физических изменений в схеме. Генерация сигналов управления зависит от регистра инструкций, декодера и сигналов прерывания.

5). Что такое контрольная память?

Информация блока управления или данные временно или постоянно хранятся в управляющей памяти.

Управляющая память бывает двух типов. Это оперативная память (RAM) и постоянная память (ROM).

Таким образом, речь идет об определении, компонентах, конструкции, схеме, функциях и типах управляющего модуля. Вот вам вопрос:«Какова цель реестра управляющих адресов?»

Встроенный

- Что такое блок управления:компоненты и его конструкция

- Что такое встроенное системное программирование и его языки

- Что такое ЧИСЛОВОЕ УПРАВЛЕНИЕ [NC]?

- Основы дизайна панели управления

- Что такое кевлар? Краткое руководство

- Что такое архитектурный дизайн?

- Что такое микроэлектроника?

- Что такое контроль качества?

- 3D-печать:каково ее влияние на машинную обработку и промышленный дизайн?

- Что такое прототипирование промышленного образца?