Startup упаковывает 1000 ядер RISC-V в чип AI-ускорителя

Энергосберегающий чип стартапа нацелен на M.2 розетки ускорителя для ускорения рекомендуемых моделей в центрах обработки данных.

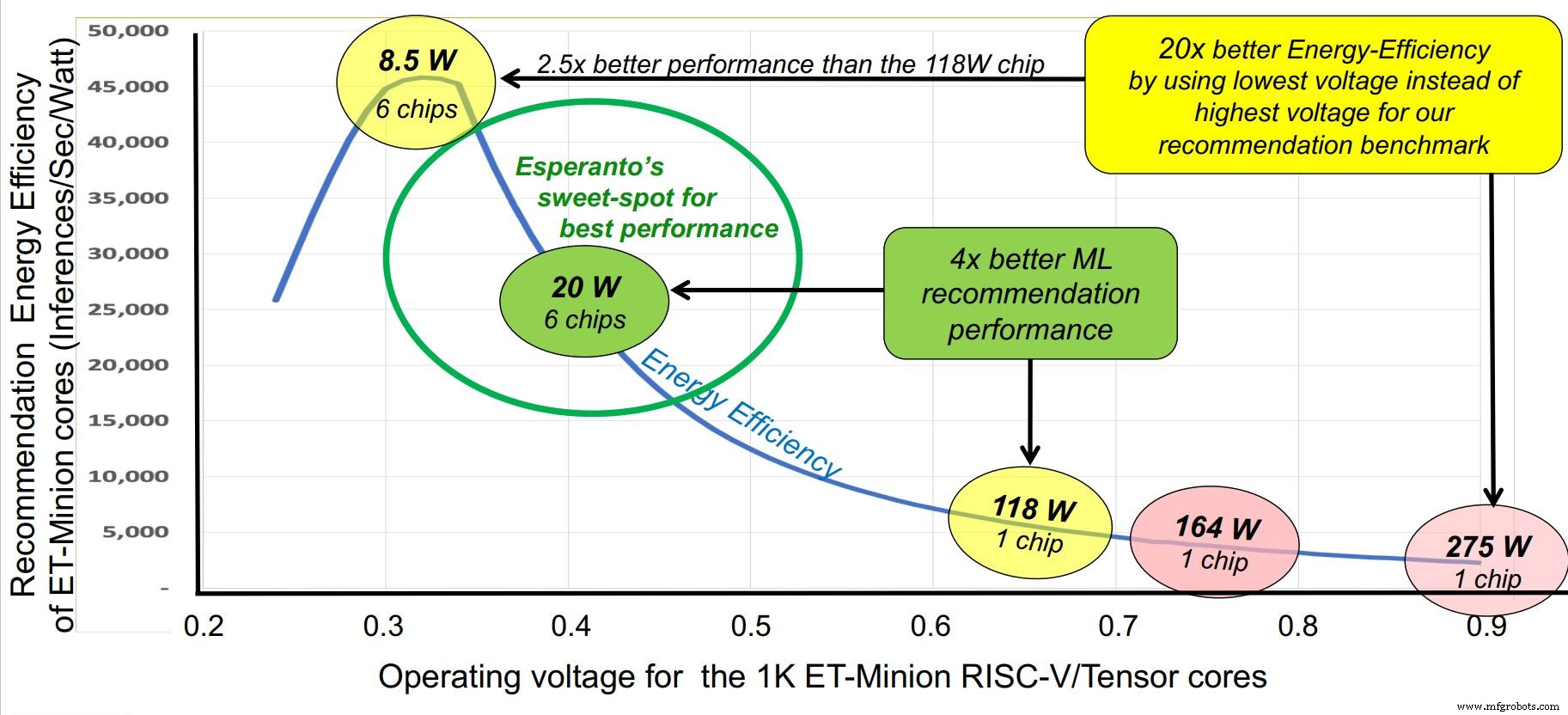

Одновременно с конференцией Hot Chips стартап Esperanto на этой неделе вышел из скрытого режима с самым производительным на сегодняшний день коммерческим чипом RISC-V - тысячным ускорителем искусственного интеллекта, разработанным для гипермасштабируемых центров обработки данных. В то время как чип может работать с несколькими профилями напряжения и мощности от 10 до 60 Вт, его «золотая середина» составляет 20 Вт мощности на чип, конфигурация, которая позволяет установить шесть чипов на карту ускорителя Glacier Point, сохраняя общее потребление менее 120 Вт. Суммарная производительность шести микросхем составляет примерно 800 TOPS.

ET-SoC-1 от Esperanto считается имеющим наибольшее количество ядер RISC-V, когда-либо построенных на одном кристалле:1093. Счетчик включает 1088 пользовательских ядер RISC-V ET-Minion, которые служат энергоэффективными двигателями ускорения AI. Также включены четыре ядра ET-Maxion RISC-V и служебный процессор RISC-V. Вся конструкция ориентирована на энергоэффективность.

Впереди Hot Chips, EE Times поговорил с ветераном отрасли Дэйвом Дитзелем, основателем и исполнительным председателем эсперанто. (Дитзель является соавтором вместе с Дэвидом Паттерсоном основополагающей статьи «Дело о компьютере с сокращенным набором команд», опубликованной в 1980 году.)

Дэйв Дитзель (Источник:эсперанто)

«Мы первые, кто поместил тысячу ядер RISC-V на один чип», - сказал Дитзель. «Люди много лет говорят о многоядерных процессорах, но мы мало что видели. Большая часть имеющихся материалов RISC-V предназначена для встраиваемых систем.

«Мы сказали:« Давайте покажем им, что RISC-V может создавать высококлассные… Мы покажем им, на что способны действительно опытные разработчики процессоров ».

Требования клиентов

Команда разработчиков ЦП Дитцеля смогла узнать подробности об их требованиях у операторов гипермасштабируемых центров обработки данных.

«Им не нужен тренировочный чип, у них нет проблем с тренировками», - сказал Дитзель. Обучение искусственного интеллекта часто является проблемой в автономном режиме, и огромная мощность процессора x86 гипермасштабирующего устройства не всегда работает при пиковой нагрузке. Следовательно, эта способность может быть использована для обучения, когда она доступна. «Их настоящая проблема - это умозаключения», - добавил Дитзель. «Это то, что движет их рекламой. Им нужен ответ в течение 10 миллисекунд или меньше ».

Следовательно, ускорение механизма вывода рекомендаций для онлайн-рекламы стало основной задачей микросхемы центра обработки данных. Требования гипермасштаберов для ускорения этого типа моделей были довольно четкими.

«Наши клиенты хотели 100 мегабайт памяти на кристалле - все, что они хотели делать с логическим выводом, умещалось в 100 мегабайт», - сказал он. Заказчикам также требовался внешний интерфейс для внешней памяти. «Настоящая проблема в том, сколько вы можете удерживать на карте ускорителя», - объяснил Дитзель. «Думайте о карте как о вычислительной единице, а не о чипе. Как только вы получите память на карте, вы сможете получить доступ к информации намного быстрее, чем через шину PCIe к хосту ».

щелкните, чтобы увидеть полноразмерное изображение

Эсперанто поместил шесть двойных карт M.2, каждая с одним чипом, на карту ускорителя Glacier Point. (Источник:эсперанто)

Система памяти на кристалле имеет кеши L1, L2 и L3 и полную систему основной памяти с файлами регистров общим объемом чуть более 100 МБ. Система памяти на карте может вместить большинство весов и активаций модели объемом около 100 ГБ.

Общеизвестно, что модели рекомендаций сложно ускорить, что является одной из причин, по которым они все еще работают на существующих серверах ЦП.

«Когда вы выбираете из 100 миллионов клиентов и то, что они покупали в последнее время, вам нужно получить доступ к этой ... памяти на карте, и вы выполняете все виды случайных обращений к памяти, поэтому кеши этого не делают. Работа. Вам действительно нужно больше классического компьютера, - сказал Дитзель. Серверы x86 обрабатывают большие объемы памяти и имеют предварительную выборку, а процессоры общего назначения очень хорошо справляются с этой рабочей нагрузкой. Из-за этого акселераторам было сложно прорваться в рекомендательный бизнес ».

Также требуется поддержка INT8 вместе с типами данных FP16 и FP32. Требование математики с плавающей запятой проистекает как из необходимости поддерживать максимально возможную точность предсказания, так и из-за отсутствия склонности к переносу или переписыванию программ для математических вычислений с более низкой точностью. Дитзель сказал, что ведущие производители серверных микросхем x86 только недавно добавили 8-битные векторные расширения в серверные процессоры.

«Большая часть логических выводов, происходящих в [гипермасштабируемом центре обработки данных] на их миллионе серверов x86, по-прежнему является 32-битной плавающей точкой», - сказал он.

Микросхема Esperanto на двойной карте M.2 предназначена для установки в слоты ускорителей в существующей серверной инфраструктуре x86 CPU. Это приводит к ограничению мощности 120 Вт, требующему воздушного охлаждения.

Дитзель сказал, что дизайн эсперанто не конкурирует напрямую с внутренними разработками, такими как Google TPU или Inferentia Amazon Web Services. Гипермасштаберы «пытаются убедить все сообщество создать для них микросхемы ускорителей. Многие из этих компаний верят в открытые вычисления и [Open Compute Project] ». Следовательно, «они покупают серверы OCP и хотят, чтобы там были стандартизированные материалы. Если есть конкуренция, им это нравится ... они пытаются поощрять конкуренцию и показывают людям, что возможно ».

Тем не менее, стартап настаивает на том, что операторам крупных центров обработки данных нужны внешние поставщики микросхем для ускорителей. «Всегда нужно выбирать между производством, а не покупкой». Например, у одного покупателя эсперанто не было доступа к микросхемам собственной разработки, используемым другим подразделением. «Если вы превзойдете то, что есть у них, возможно вход в любую из этих компаний».

Новый подход

Esperanto использует противоположный подход к гигантским энергоемким ускорителям чипов конкурентов, предлагая чип с меньшим энергопотреблением, который можно использовать в нескольких экземплярах. Подход направлен на удовлетворение требований к пропускной способности памяти, поскольку для ввода-вывода памяти можно использовать больше контактов, не прибегая к дорогостоящему HBM.

Аппаратное обеспечение Esperanto также разработано как универсальный компьютер; По словам Дитзеля, несмотря на акцент на рекомендательных моделях, чип может ускорить параллельную обработку. Карта-ускоритель с шестью микросхемами включает около 6000 параллельных ядер, и каждое ядро может выполнять два потока, которые могут быть «решены в любой произвольной задаче».

Еще одна хитрость в рукаве эсперанто - агрессивный энергоэффективный дизайн. Требования заказчика устанавливают общий бюджет мощности 120 Вт, в то время как максимальное пространство, установленное на карте Glacier Point, составляет шесть микросхем, или 20 Вт на микросхему. Для сравнения:ускорители вывода ИИ работают более чем в десять раз больше.

На эсперанто этот вопрос рассматривался с нескольких точек зрения. Тактовая частота была снижена до оптимального уровня около 1 ГГц. Напряжение питания было снижено примерно до 0,4 В, что превышает предел SRAM. Коммутационной емкости способствовало использование упрощенных ядер RISC-V с наименьшим коммерчески жизнеспособным набором команд для уменьшения количества транзисторов. Был выбран передовой, но стабильный техпроцесс TSMC 7 нм.

щелкните, чтобы увидеть полноразмерное изображение

Эсперанто определил «золотую середину» для работы на частоте около 1 ГГц. (Источник:эсперанто)

Основной дизайн

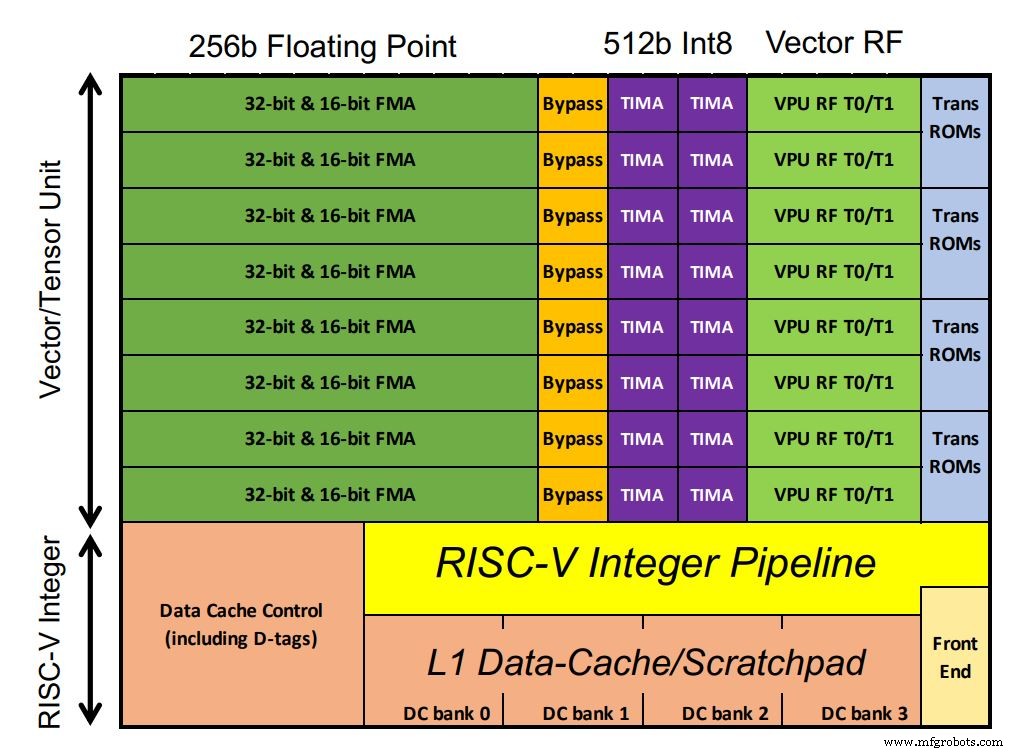

Чип Esperanto включает 1088 ядер ET-Minion, которые обрабатывают рабочую нагрузку AI. Ядра представляют собой 64-битные процессоры RISC-V с упорядоченным порядком, с собственным векторным и тензорным блоком Esperanto, оптимизированным для искусственного интеллекта, и занимают большую часть площади чипа. MAC с плавающей запятой доминируют в конфигурации. Необычно, что целочисленные MAC-адреса имеют вдвое большую ширину обработки, чем с плавающей запятой (в соответствии с требованиями заказчика, отметил Дитцель). Также поддерживаются векторные трансцендентные инструкции, такие как сигмовидные функции, распространенные в моделях глубокого обучения. Поскольку ядра работают в одном низковольтном домене, было использовано больше транзисторов со SRAM в небольшом кэше L1 для обеспечения надежной производительности.

щелкните, чтобы увидеть полноразмерное изображение

Чип Esperanto содержит 1088 ядер ET-Minion (щелкните изображение, чтобы увеличить) (Источник:Esperanto)

Каждое ядро способно выполнять 128 GOPS на ГГц. Специальная команда многоциклового тензора выполняет большие матричные умножения с отдельным контроллером, выполняющим до 512 циклов с использованием полной ширины 512 бит. Это позволяет одной тензорной инструкции выполнять более 64000 арифметических операций до того, как контроллер выберет следующую инструкцию RISC-V. Это снижает пропускную способность инструкций, поскольку основная часть рабочей нагрузки использует тензорные инструкции. Следовательно, требуется только одна инструкция на 512 тактов.

Восемь ядер ET-Minion составляют «соседство», а модифицированные инструкции используют их физическую близость. Другая функция, называемая «кооперативная загрузка», позволяет ядрам передавать данные напрямую друг от друга без выборки из кеша. Такая конфигурация экономит электроэнергию. Восемь ядер также используют большой кэш L2 для повышения энергоэффективности.

Если снова уменьшить масштаб, четыре 8-ядерных района образуют «Minion Shire» с 34 шайрами на каждом чипе, что в сумме составляет 1088 ядер. (По словам Дитзеля, для повышения производительности также возможны вычисления только с 1024 ядрами). Четыре ядра ET-Maxion, каждое с производительностью, примерно сравнимой с Arm A-72, предназначены для будущей автономной работы, а не для текущей конфигурации ускорителя.

Колебания порогового напряжения смягчаются за счет того, что каждому Shire предоставляется собственный источник напряжения, позволяющий точно настраивать индивидуальные напряжения.

Система памяти

Каждый чип имеет четыре 64-битных интерфейса DDR - фактически, каждый интерфейс представляет четыре 16-битных канала - всего 96 16-битных каналов. В конструкции используется LPDDR4x, разработанный как память с низким энергопотреблением для смартфонов. Энергия на бит примерно эквивалентна HBM, но поддержание общего значения 1536 бит через интерфейс памяти для карты ускорителя с шестью микросхемами дает более высокую общую пропускную способность памяти.

Esperanto установил свои чипы на двухсокетные карты M.2; шесть подходят к карте ускорителя OCP Glacier Point v2 (три спереди, три сзади). Это обеспечивает около 800 TOPS при работе микросхем на частоте 1 ГГц. Они также могут быть установлены на низкопрофильных (половинной высоты или половинной длины) платах PCIe, что увеличивает бюджет мощности каждого чипа примерно до 60 Вт. Чипы могут работать в диапазоне от 300 МГц до 2 ГГц, в зависимости от приложения.

Основываясь на результатах аппаратной эмуляции, Ditzel утверждал, что шесть чипов Esperanto на карте Glacier Point могут превзойти конкурентов. Преимущество стартапа становится очевидным в рекомендательных тестах, когда учитываются конструкция системы памяти и показатели производительности на ватт, что является следствием акцента на низковольтной конструкции.

Будущие версии могут включать в себя уменьшенную версию ET-SoC-1 для периферийных приложений. Дитзель сказал, что текущая версия должна выйти «в ближайшие пару месяцев».

>> Эта статья изначально была опубликована на нашем дочернем сайте EE Times.

Связанное содержание:

- SoC с поддержкой AI обрабатывают несколько видеопотоков.

- Xilinx нацелена на разгрузку центра обработки данных с помощью «компонуемого» оборудования.

- Вычисление сокращенного набора операций (ROSC) для функционального покрытия NNA.

- Гибридная архитектура ускоряет рабочие нагрузки ИИ и машинного зрения.

- Аппаратные ускорители обслуживают приложения ИИ.

Чтобы получить больше информации о Embedded, подпишитесь на еженедельную рассылку Embedded по электронной почте.

Встроенный

- Револьвер

- Хорошие перспективы для EDA в облаке

- Саммит RISC-V:основные моменты повестки дня

- Arm позволяет настраивать инструкции для ядер Cortex-M

- Проектирование с помощью сети Bluetooth:чип или модуль?

- Архитектура микросхемы ИИ нацелена на обработку графов

- Крошечный модуль Bluetooth 5.0 объединяет чип-антенну

- Исследователи создают крошечный тег идентификации аутентификации

- Представлен процессор автомобильных радаров со скоростью 30 кадров в секунду

- Радиолокационный чип с низким энергопотреблением использует нейронные сети с пиками