Сборки GPU с открытым исходным кодом на RISC-V

Группа энтузиастов предлагает новый набор графических инструкций, предназначенный для обработки трехмерной графики и мультимедиа. Эти новые инструкции построены на наборе команд базового вектора RISC-V. Они добавят поддержку новых типов данных, специфичных для графики, в виде многоуровневых расширений в духе базовой архитектуры набора команд RISC-V (ISA). Поддерживаются векторы, трансцендентная математика, пиксели и текстуры, а также операции с буфером Z / Frame. Это может быть слитный CPU-GPU ISA. Группа называет это RV64X, поскольку инструкции будут иметь длину 64 бита (32 бита будет недостаточно для поддержки надежного ISA).

Почему именно сейчас?

В мире есть из чего выбирать, почему это? Потому что, по словам группы, коммерческие графические процессоры менее эффективны для удовлетворения необычных потребностей, таких как двухфазное усеченное трехмерное ограничение, адаптируемые HPC (БПФ с произвольной битовой глубиной), аппаратное SLAM. Они считают, что сотрудничество обеспечивает гибкие стандарты, сокращает затраты на 10–20 человеко-лет, которые в противном случае потребовались бы, и поможет при перекрестной проверке, чтобы избежать ошибок.

Команда говорит, что их мотивация и цели обусловлены желанием создать небольшой, эффективный по площади дизайн с настраиваемой программируемостью и расширяемостью. Он должен предлагать недорогое владение ИС и разработку, а не конкурировать с коммерческими предложениями. Он может быть реализован в целях FPGA и ASIC и будет бесплатным с открытым исходным кодом. Первоначальный дизайн будет ориентирован на микроконтроллеры с низким энергопотреблением. Он будет совместим с Khronos Vulkan и со временем будет поддерживать другие API (OpenGL, DirectX и другие).

Конечным оборудованием будет ядро RISC-V с функциональным блоком GPU. Для программиста это будет выглядеть как единое целое с 64-битными длинными инструкциями, закодированными как скалярные инструкции. Модель программирования представляет собой очевидную SIMD, то есть компилятор генерирует SIMD из скалярных кодов операций с префиксом. Он будет включать в себя проблемы с переменными, предиктивную внутреннюю часть SIMD, интерфейс векторов, точные исключения, затенение ветвей и многое более. По словам команды, не будет необходимости в механизме вызовов RPC / IPC для отправки вызовов 3D API в / из неиспользуемого пространства памяти ЦП в пространство памяти ГП и наоборот. И он будет доступен как с 16-битной фиксированной точкой (идеально подходит для FPGA), так и с 32-битной плавающей точкой (ASIC или FPGA).

В дизайне будет использован формат Vblock (от усилий Libre GPU):

- Это немного похоже на VLIW (только не совсем)

- Блок инструкций предварительно фиксируется тегами регистров, которые придают дополнительный контекст скалярным инструкциям внутри блока.

- Подблоки включают:длину вектора, изменение ширины, переопределение вектора / ширины и прогнозирование.

- Все это добавлено в скалярные коды операций

- Нет векторных кодов операций (и в них нет необходимости).

- В векторном контексте это выглядит следующим образом:если регистр используется скалярным кодом операции и регистр указан в векторном контексте, активируется векторный режим.

- Активация приводит к тому, что цикл for на аппаратном уровне выполняет несколько смежных скалярных операций (вместо одной).

- Разработчики могут реализовать цикл любым желаемым способом:SIMD, многозадачность, однократное выполнение.

В проекте будут использоваться скаляры (8-, 16-, 24- и 32-битные фиксированные и числа с плавающей запятой), а также трансцендентные числа (sincos, atan, pow, exp, log, rcp, rsq, sqrt и т. Д.). Векторы (RV32-V) будут поддерживать 2-4-элементные (8-, 16- или 32-битные / 32-битные / элемент) векторные операции, а также специализированные инструкции для общего конвейера рендеринга 3D-графики для точек, пикселей, текселей (по сути, специальных векторов )

- Точки XYZW (64- и 128-битные фиксированные и плавающие)

- пиксели RGBA (8-, 16-, 24- и 32-битные пиксели)

- тексели UVW (8-, 16-битные на компонент)

- Источники света и материалы (Ia, ka, Id, kd, Is, ks…)

Матрицы будут иметь размер 2 × 2, 3 × 3 и 4 × 4. Матрицы будут поддерживаться как собственный тип данных вместе со структурами памяти для их поддержки для векторов атрибутов и будут по существу представлены в матрице 4 × 4.

Среди преимуществ слияния ISA CPU-GPU - возможность реализовать стандартный графический конвейер в микрокоде, обеспечить поддержку настраиваемых шейдеров и реализовать расширения трассировки лучей. Он также поддерживает векторы для численного моделирования с 8-битными целочисленными типами данных для ИИ и машинного обучения.

Можно реализовать собственные растеризаторы, такие как сплайны, поверхности SubDiv и патчи.

Дизайн будет достаточно гибким, чтобы реализовывать настраиваемые этапы конвейера, этапы настраиваемой геометрии / пикселя / буфера кадра, настраиваемые тесселяторы и настраиваемые операции создания экземпляров.

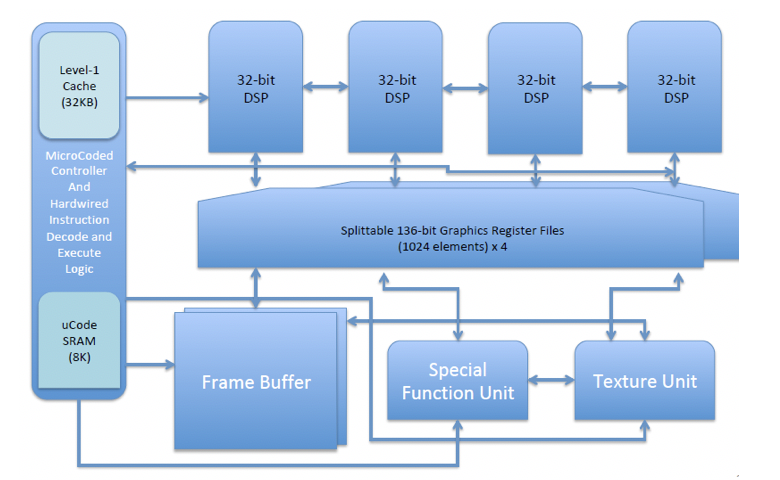

Блок-схема RV64X

Эталонная реализация RV64X будет включать:

- Кэш SRAM для инструкций / данных (32 КБ)

- SRAM микрокода (8 КБ)

- Декодер инструкций двойного назначения

- Проводная реализация RV32V и X

- Декодер микрокодированных инструкций для пользовательского ISA.

- Quad Vector ALU (32 бита / ALU - фиксированный / с плавающей запятой)

- 136-битные файлы регистров (1К элементов)

- Блок специальных функций

- Текстурный блок

- Настраиваемый локальный буфер кадра

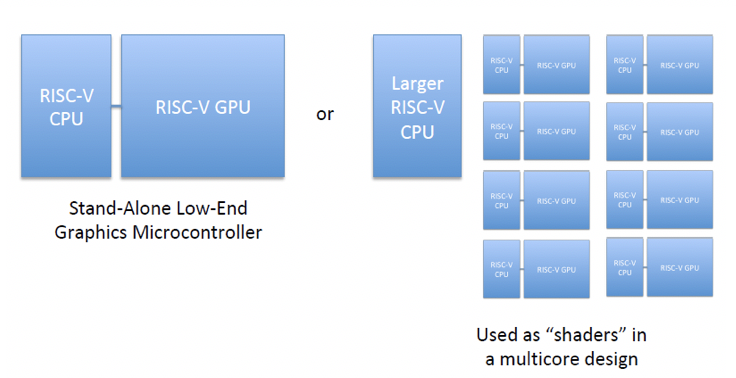

Дизайн должен быть масштабируемым, как указано ниже.

Масштабируемая конструкция RV64X

В конструкции RV64X есть несколько новых идей, включая объединенный унифицированный ISA CPU-GPU, конфигурируемые регистры для пользовательских типов данных и определяемый пользователем микрокод на основе SRAM для определяемых приложением пользовательских аппаратных расширений для:

- Пользовательские этапы растеризации

- Трассировка лучей

- Машинное обучение

- Компьютерное зрение

Та же самая конструкция служит как автономным графическим микроконтроллером, так и масштабируемым шейдерным блоком, а форматы данных поддерживают реализации FPGA или ASIC.

Зачем нужна открытая графика?

Разработчики считают, что большинство графических процессоров предназначены для высокопроизводительных приложений, таких как игры, высокочастотная торговля, компьютерное зрение и машинное обучение. Они считают, что в экосистеме отсутствует масштабируемое графическое ядро для более массовых приложений, таких как киоски, рекламные щиты, игры в казино, игрушки, робототехника, бытовая техника, носимые устройства, промышленные человеко-машинные интерфейсы, информационно-развлекательные и автомобильные измерительные кластеры. Между тем, для программирования ядер графического процессора для OpenGL, OpenCL, CUDA, DirectCompute и DirectX должны использоваться специальные языки программирования.

Расширение графики для RISC-V устранит проблемы масштабируемости и многоязычности, что позволит повысить уровень инноваций в сценариях использования.

Дальнейшие действия

Это очень ранняя спецификация, все еще в разработке и может быть изменена в зависимости от мнения заинтересованных сторон и отрасли. Команда создаст дискуссионный форум. Ближайшей целью является создание образца реализации с симулятором набора инструкций, реализация FPGA с использованием IP с открытым исходным кодом и пользовательского IP, разработанного как проект с открытым исходным кодом. Разрабатываются демонстрационные версии и тесты. Разработчики, заинтересованные в участии, должны заключить контракт с Атифом Зафаром.

Что касается Libre-RISC 3D GPU, цель организации - разработать гибридный CPU, VPU и GPU. Это не «специализированный эксклюзивный графический процессор», как широко сообщается. Существует возможность создать автономный продукт с графическим процессором. Их основная цель - разработать комплексную SoC для процессора "все в одном", которая может включать в себя виртуальный процессор и графический процессор с лицензией Libre.

Что мы думаем?

Число поставщиков графических процессоров увеличивается. Теперь у нас больше дюжины.

AppleLibre-RISC-V 3D GPUQualcommAMDNvidiaRISC-V ГрафикаArmIntelThink-SiliconDMPJingjia MicroVeriSilcionImagination TechnologiesПриложение, не указанное в списке как потенциальный пользователь бесплатного гибкого небольшого графического процессора, включает криптовалюту и майнинг.

Если целью сообщества RISC-V является подражание поставщикам IP, таким как Arm и Imagination, то мы можем ожидать увидеть проекты DSP, ISP и DP. Есть по крайней мере одно предложение Open DSP; возможно, его удастся внести в сообщество RISC-V.

Пройдет как минимум два года, прежде чем появятся какие-либо аппаратные реализации. Одним из наиболее логичных кандидатов на принятие этого дизайна является Xilinx, который теперь использует Arm’s Mali в своем дизайне Zynq. Мы также ожидаем увидеть несколько внедрений из Китая.

>> Эта статья была первоначально опубликована на наш дочерний сайт EE Times.

Джон Педди , пионер в графической индустрии, является президентом Jon Peddie Research.

Джон Педди , пионер в графической индустрии, является президентом Jon Peddie Research. Чтобы получить больше информации о Embedded, подпишитесь на еженедельную рассылку Embedded по электронной почте.

Встроенный

- Введение в терминологию с открытым исходным кодом

- Открытый исходный код и Интернет вещей:инновации через сотрудничество

- Саммит RISC-V:основные моменты повестки дня

- Безопасность промышленного Интернета вещей основывается на аппаратном обеспечении

- Журнал проекта для FirePick Delta, MicroFactory с открытым исходным кодом

- AT&T и Tech Mahindra совместно работают над новой платформой искусственного интеллекта с открытым исходным кодом

- Программные риски:защита открытого исходного кода в IoT

- Инструменты разработки IoT с открытым исходным кодом и инструменты, поддерживаемые поставщиком

- MassRobotics публикует «первые в мире» стандарты совместимости автономных мобильных роботов с открытым исходным к…

- Необходимость открытого исходного кода на периферии (электронная книга)