Чип процессора в памяти ускоряет вычисления AI

Imec и GlobalFoundries продемонстрировали микросхему «процессор в памяти», которая может обеспечить энергоэффективность до 2900 TOPS / Вт, что примерно на два порядка выше, чем у современных коммерческих микросхем «процессор в памяти». В чипе используется устоявшаяся идея - аналоговые вычисления, реализованные в SRAM по 22-нанометровой технологии полностью обедненного кремния на изоляторе (FD-SOI) GlobalFoundries. Аналоговые вычисления в памяти (AiMC) Imec будут доступны клиентам GlobalFoundries в качестве функции, которая может быть реализована на платформе компании 22FDX.

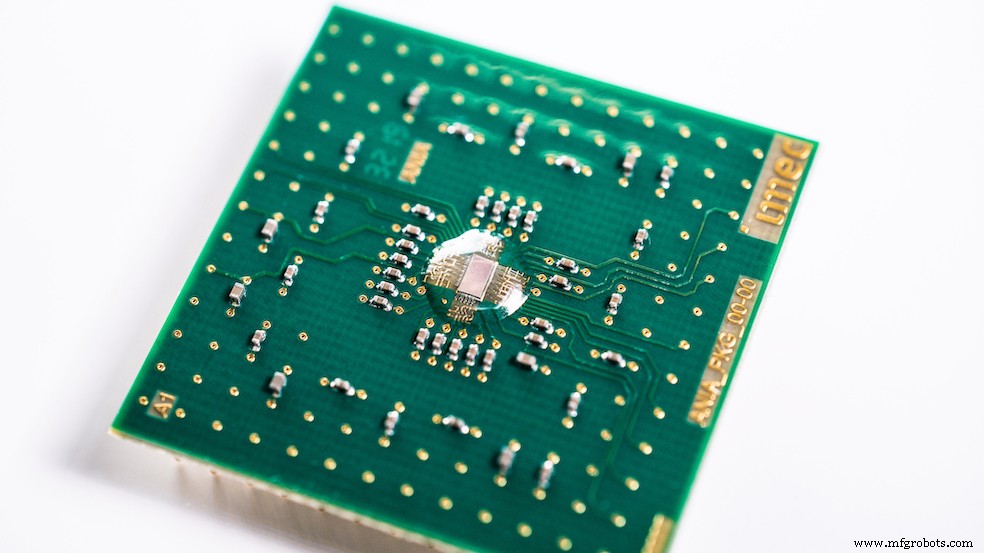

Тестовый чип Imec AnIA, установленный на печатной плате, используемой для измерения и определения характеристик, может достигать 2900 TOPS / Вт (Изображение:Imec)

Аналоговые вычисления

Аналоговые вычисления, или процессор в памяти, - это устоявшаяся технология, которая уже используется в коммерческих микросхемах ускорителей искусственного интеллекта от стартапов Mythic, Syntiant, Gyrfalcon и других.

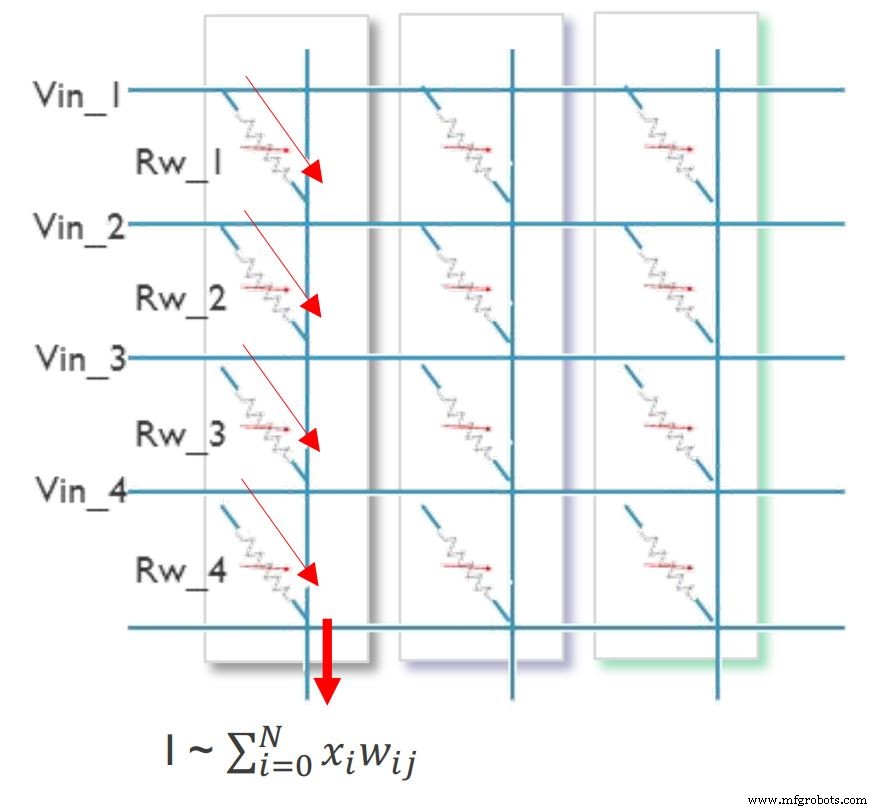

Поскольку модель нейронной сети может иметь десятки или сотни миллионов весов, отправка данных между памятью и процессором неэффективна. Аналоговые вычисления используют массив памяти для хранения весов, а также для выполнения операций умножения-накопления (MAC), поэтому нет необходимости в передаче от памяти к процессору. Каждый мемристорный элемент (возможно, ячейка ReRAM) запрограммирован на аналоговый уровень проводимости, который пропорционален требуемому весу.

Приложение напряжения, пропорционального активации входа (через цифро-аналоговое преобразование - слева на диаграмме ниже), означает, что ток через каждый элемент пропорционален произведению активации и веса. Ток через каждую вертикальную битовую линию (вертикальные линии на диаграмме ниже) является суммой этих продуктов веса активации, которые могут подаваться через аналого-цифровой преобразователь. Эта сумма продуктов веса активации имеет решающее значение для расчета алгоритмов нейронной сети.

Аналоговые вычисления используют массив ячеек мемристора для вычисления умножения векторов матрицы без необходимости пересылки данных между памятью и процессором (Изображение:Imec)

«На практике, помимо ReRAM, возможны многие варианты - мы можем использовать MRAM, Flash, DRAM ... цель этой программы - понять, что лучше всего для приложения, и оптимизировать параметры для каждого домена приложения», - пояснил Дидерик Веркест, программа директор по машинному обучению в Imec.

Тестовый чип

Imec построила тестовый чип, называемый ускорителем аналогового вывода (AnIA), на основе 22-нм процесса FD-SOI GlobalFoundries. Массив AnIA 512 КБ ячеек SRAM плюс цифровая инфраструктура, включая 1024 ЦАП и 512 АЦП, занимает 4 мм 2 . Он может работать около полумиллиона

Иоаннис Папистас (Изображение:Imec)

вычислений за рабочий цикл на основе 6-битных (плюс знаковый бит) активаций входа, троичных весов (-1, 0, +1) и 6-битных выходов.

«Мы можем производить выходные данные матричного умножения векторов при различных напряжениях питания, 0,8 и 0,6 В», - сказал Иоаннис Папистас из группы машинного обучения Imec. «Работа при более низких напряжениях питания, не влияя на точность работы, может значительно снизить энергопотребление при работе, что особенно важно для вывода в системах с ограничением энергии. Это важная особенность нашего дизайна, реализованная с помощью процесса 22FDX, которая позволяет делать выводы о конкурентоспособности на грани ».

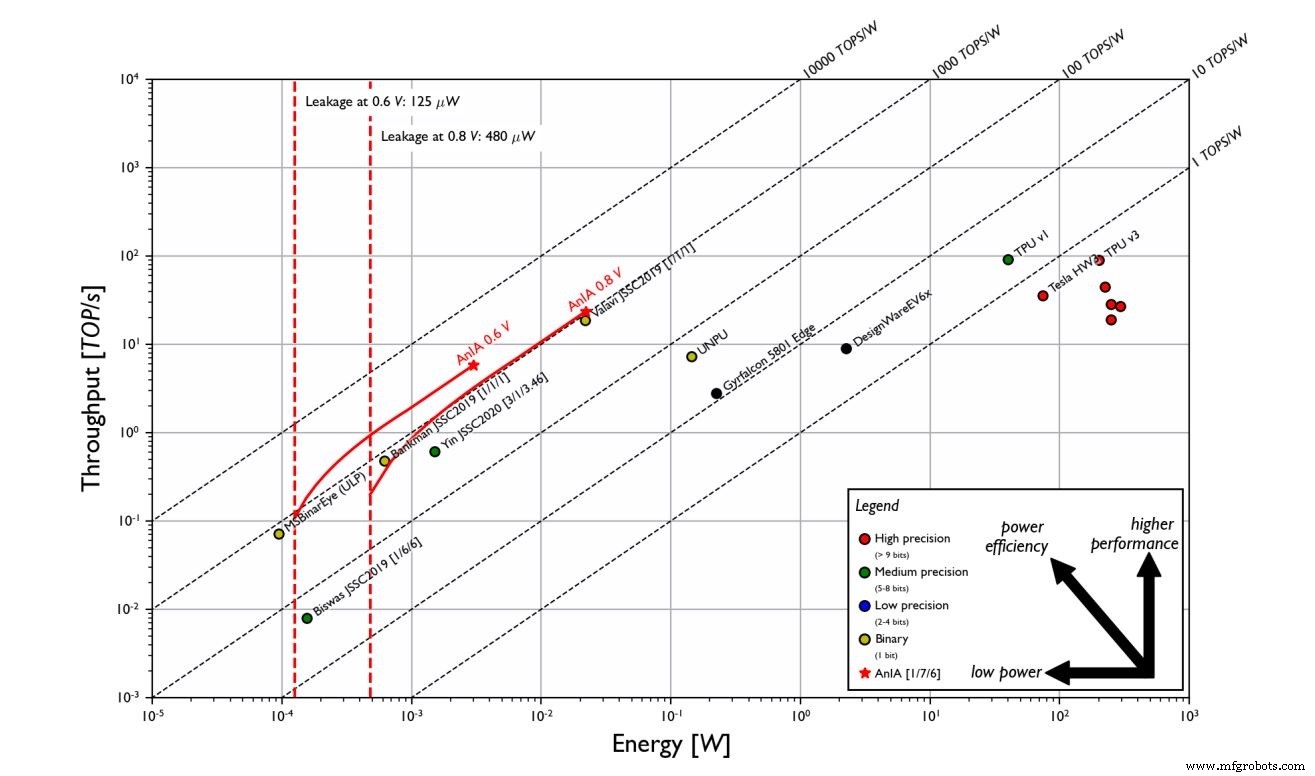

Imec продемонстрировал результаты точности вывода распознавания объектов для набора данных CIFAR 10, которые упали всего на один процентный пункт по сравнению с аналогичным количественным базовым уровнем. При напряжении питания 0,8 В энергоэффективность AnIA составляет от 1050 до 1500 ТОПС / Вт при 23,5 ТОПС. Для напряжения питания 0,6 В AnIA достиг 5,8 ТОПС при 1800-2900 ТОПС / Вт.

Энергоэффективность различных ускорителей ИИ по сравнению с тестовым чипом Imec AnIA (Нажмите, чтобы увеличить) (Изображение:Imec)

Основные инновации

«Инновация [представленная Imec] станет мейнстримом, - сказал Хирен Маджмудар, вице-президент и генеральный директор компьютерного подразделения GlobalFoundries. «Мы видим партнеров, клиентов GlobalFoundries, которые находятся на стадии постпроизводства с проверенным кремнием… мы ожидаем, что кремний на основе аналоговых вычислений начнет производство примерно в конце этого или в начале следующего года. Что касается массового развертывания рынка, мы ожидаем, что аналоговые вычисления начнут поступать на массовый рынок не позднее 2022 года. Но потенциально это может произойти и раньше ».

Дидерик Веркест (Изображение:Imec)

GlobalFoundries работает над включением технологии Imec AiMC в качестве функции, которая может быть реализована на платформе 22 FDX для создания энергоэффективных ускорителей искусственного интеллекта. Процесс FD-SOI разработан для низкого энергопотребления, с возможностью работы при напряжении до 0,5 В с 1 пикоампер на микрон для сверхмалой утечки в режиме ожидания. 22FDX с новой функцией AiMC находится в разработке на 300-миллиметровой производственной линии GlobalFoundries на заводе Fab 1 в Дрездене, Германия.

Что касается Imec, то программа машинного обучения будет продолжена. По словам Веркеста, группа стремится достичь 10 000 TOPS / Вт (10 TOPS при менее 100 мВт) для постоянно включенных интеллектуальных датчиков и потребительских носимых устройств.

«В нашей программе машинного обучения наши следующие шаги - уменьшить размер этих вычислительных ячеек и начать рассматривать новые устройства памяти как реализацию следующего поколения для этого принципа», - сказал он.

>> Эта статья была первоначально опубликована на наш дочерний сайт EE Times.

Встроенный

- Введение в аналоговые интегральные схемы

- Вычислительные схемы

- Проектирование с помощью сети Bluetooth:чип или модуль?

- Архитектура микросхемы ИИ нацелена на обработку графов

- Крошечный модуль Bluetooth 5.0 объединяет чип-антенну

- Исследователи создают крошечный тег идентификации аутентификации

- Представлен процессор автомобильных радаров со скоростью 30 кадров в секунду

- Радиолокационный чип с низким энергопотреблением использует нейронные сети с пиками

- Интеллектуальная сенсорная плата ускоряет разработку периферийного ИИ

- Прочный БПЛА ускоряется до производственного уровня