Цифровой линейный АЦП

Также известен как ступенька-пандус . , или просто counter Преобразователь A / D, это тоже довольно легко понять, но, к сожалению, имеет несколько ограничений.

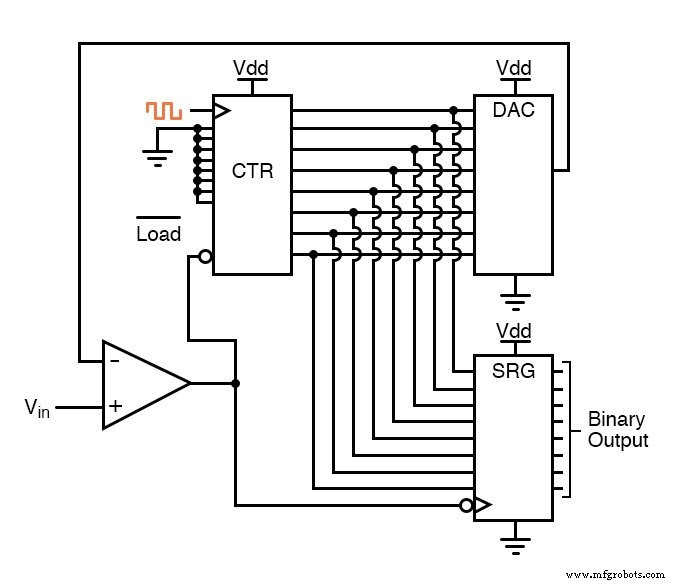

Основная идея состоит в том, чтобы подключить выход автономного двоичного счетчика ко входу ЦАП, затем сравнить аналоговый выход ЦАП с аналоговым входным сигналом, который необходимо оцифровать, и использовать выход компаратора, чтобы сообщить счетчику, когда нужно остановиться. подсчет и сброс. На следующей схеме показана основная идея:

По мере того как счетчик считает с каждым тактовым импульсом, ЦАП выдает немного более высокое (более положительное) напряжение. Это напряжение сравнивается с входным напряжением компаратором.

Если входное напряжение больше, чем выходное напряжение ЦАП, выход компаратора будет высоким, и счетчик продолжит нормальный счет. Однако в конце концов выходное напряжение ЦАП превысит входное напряжение, в результате чего выход компаратора станет низким.

Это вызовет две вещи:во-первых, переход от высокого к низкому на выходе компаратора заставит сдвиговый регистр «загружать» любой двоичный счет, выводимый счетчиком, таким образом обновляя выход схемы АЦП; во-вторых, счетчик получит сигнал низкого уровня на входе LOAD с активным низким уровнем, что приведет к его сбросу на 00000000 при следующем тактовом импульсе.

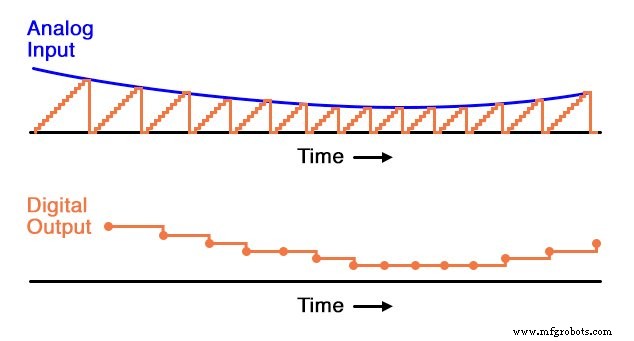

Эффект этой схемы состоит в том, чтобы создать выходной сигнал ЦАП, который нарастает до любого уровня аналогового входного сигнала, вывести двоичное число, соответствующее этому уровню, и начать все сначала. На графике это выглядит так:

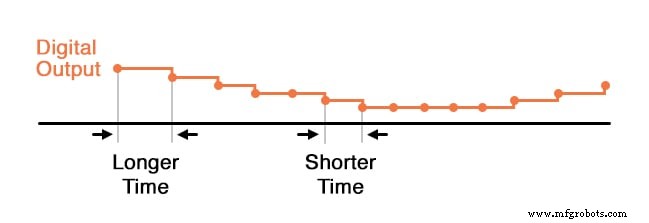

Обратите внимание, как время между обновлениями (новыми значениями цифрового выхода) изменяется в зависимости от того, насколько велико входное напряжение. Для низких уровней сигнала обновления расположены довольно близко друг к другу. Для более высоких уровней сигнала они разнесены во времени дальше:

Для многих приложений АЦП такое изменение частоты обновления (времени выборки) неприемлемо. Это, а также тот факт, что схема должна вести счет полностью от 0 в начале каждого цикла счета, приводит к относительно медленной выборке аналогового сигнала, ставит АЦП с цифровым линейным нарастанием в невыгодное положение по сравнению с другими стратегиями счетчиков.>

Промышленные технологии