Синхронизация и распределение асинхронного сброса - ASIC и FPGA

Отсутствие координации между асинхронным сбросом и синхронными логическими часами приводит к периодическим сбоям при включении питания. В этой серии статей мы обсуждаем требования и проблемы асинхронного сброса и исследуем передовые решения для проектирования ASIC и FPGA.

Асинхронный сброс традиционно используется в конструкциях СБИС для приведения синхронной схемы в известное состояние после включения питания. Операция разблокировки асинхронного сброса должна быть скоординирована с сигналом синхронных логических часов, чтобы исключить сбои синхронизации из-за возможного конфликта между сбросом и часами. Отсутствие такой координации приводит к периодическим сбоям при включении питания. Проблема усугубляется при рассмотрении больших многочастотных доменов. Помимо проблем с синхронизацией, распределение асинхронного сброса на миллионы триггеров является сложной задачей, требующей методов, аналогичных CTS (Синтез дерева часов) и требующих аналогичных ресурсов области и маршрутизации.

Рассмотрены требования и проблемы асинхронного сброса с уделением особого внимания вопросам синхронизации и распределения. Обсуждаются недостатки классических решений для синхронизации сброса (синхронизация источника дерева сброса) и распределения (синтез дерева сброса). Представлены передовые решения для более быстрой и простой сходимости по времени и более надежной синхронизации и распределения сбросов. Подробно описаны различные подходы к проектированию ASIC и FPGA.

В части 1 описываются проблемы, связанные с асинхронным сбросом, и излагаются подходы к их решению. В части 2 (эта статья) обсуждаются дополнительные решения для правильного асинхронного сброса в ASIC и FPGA. Некоторые полезные частные случаи обсуждаются в Части 3.

2. Методы конвергенции с асинхронным сбросом времени

Одной из основных проблем, обсуждаемых в Части 1, была сложность сброса сброса для больших проектов (с распределительной сетью сброса с высокой задержкой), особенно когда используется короткий тактовый цикл. Сходимость по времени, основанная на стандартной оптимизации STA, приводит к дорогостоящему проекту, а в некоторых случаях даже невозможна. Здесь мы обсуждаем два метода, которые смягчают эту проблему синхронизации. Оба метода применимы как для ASIC, так и для проектов FPGA.

2.1. Конвейерная обработка асинхронного сброса

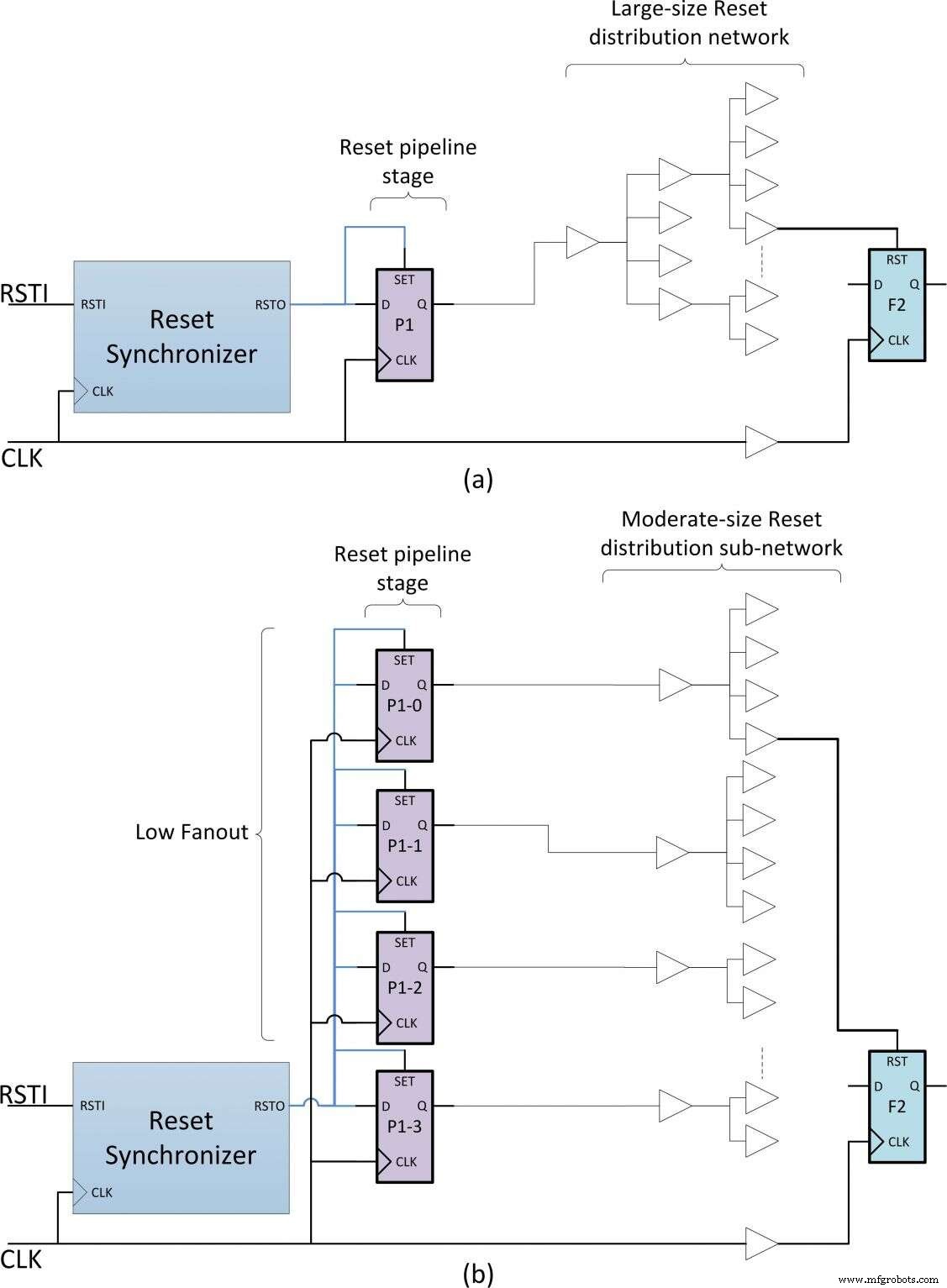

Один из способов решения проблемы синхронизации при асинхронном сбросе сброса состоит в том, чтобы найти компромисс между задержкой сброса сброса в пользу более расслабленного выбора времени. Это может быть достигнуто путем конвейерной обработки дерева сброса следующим образом. После каждого синхронизатора в линию сброса включается дополнительный каскад P1 с асинхронным триггером (рис. 6а). Оба входа SET и D триггера подключены к активному высокому уровню сброса RSTO, поступающему от синхронизатора сброса. В версии RSTO условия установки и удержания удовлетворяются для входов P1 D и SET, поскольку они ограничены как обычные синхронные пути.

щелкните, чтобы увеличить изображение

Рисунок 6. Асинхронный сброс с конвейерной обработкой (Источник:vSync Circuits)

Функциональная работа новой схемы аналогична обычной, описанной в части 1 (рисунок 3d), за исключением дополнительной задержки в один цикл при сбросе. Более высокая задержка сброса, связанная с этим методом, обычно приемлема для большинства приложений, так как происходит только один раз при включении питания.

Дополнительная часть этого метода охватывает ограничения дизайна. В то время как триггеры синхронизатора должны быть ограничены от дублирования, чтобы предотвратить проблемы пути повторной конвергенции, как описано в Части 1, этап конвейера P1 подлежит ограничению MAX_FANOUT. Пример ограничения максимального разветвления показан на рисунке 6b. Триггер P1 автоматически дублируется инструментом синтеза, создавая четыре подсети для распределения сброса. Каждая подсеть имеет меньшую задержку, чем исходная сеть, что соответствует требованиям по времени для сброса. Кроме того, выход синхронизатора сброса легко соответствует восьми разветвителям.

Этот метод конвейерной обработки асинхронного сброса масштабируется для любого размера проекта и не требует изменений при изменении проекта, поскольку инструмент синтеза автоматически дублирует стадию P1, сохраняя ограниченную подсеть сброса с умеренной задержкой. Дублированный разветвитель ступени P1 для выхода синхронизатора обычно небольшой и не вызывает нарушений синхронизации. Однако, когда одна ступень конвейера не приводит к сходимости по времени, могут быть включены дополнительные ступени конвейера P2 - PN и ограничены различными ограничениями MAX_FANOUT.

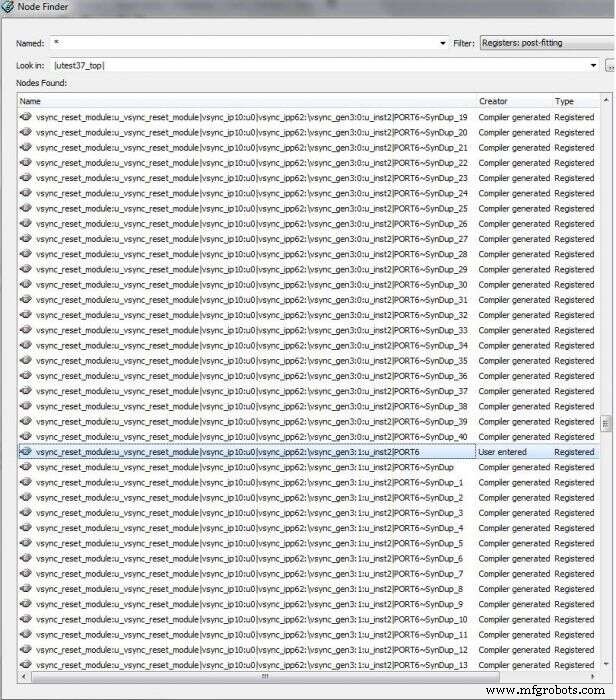

Пример этого метода, примененного к реальному проекту, показан на рисунке 7. Регистр каскада P1, названный PORT6, был автоматически дублирован примерно 40 раз инструментом синтеза [6], чтобы соответствовать ограничению MAX_FANOUT. Каждая из 40 подсетей соответствовала срокам своего локального разветвления.

щелкните, чтобы увеличить изображение

Рисунок 7. Пример конвейерной обработки асинхронного сброса (Источник:vSync Circuits)

Встроенный

- Структуры и классы в C ++

- Почтовые ящики:введение и основные услуги

- Семафоры:введение и базовые услуги

- Anvo-Systems и Mouser подписывают дистрибьюторское соглашение

- Mouser и Inventek Systems объявляют о глобальном дистрибьюторском соглашении

- Rutronik и AP Memory подписывают глобальное дистрибьюторское соглашение

- Albis Plastics Разделенное распространение и объединение предприятий

- Искусство и наука выбора сайта распространения

- Шесть способов сокращения выбросов при хранении и распределении

- RG Group договаривается о сотрудничестве в области распространения и интеграции с мобильными роботами AutoGuide