Arm предлагает IP-адрес нейронной обработки для процессоров приложений

Компания Arm создала новую версию своего IP-адреса microNPU (нейронной обработки), которая подходит для использования вместе с ядрами ЦП Cortex-A в процессорах приложений. Ведущий лицензиат NXP планирует использовать этот IP-адрес в следующем семействе прикладных процессоров, которые могут обрабатывать приложения AI, такие как оценка позы, распознавание нескольких лиц и обнаружение объектов в видео, а также распознавание речи помимо базового определения ключевых слов.

Ethos-U65

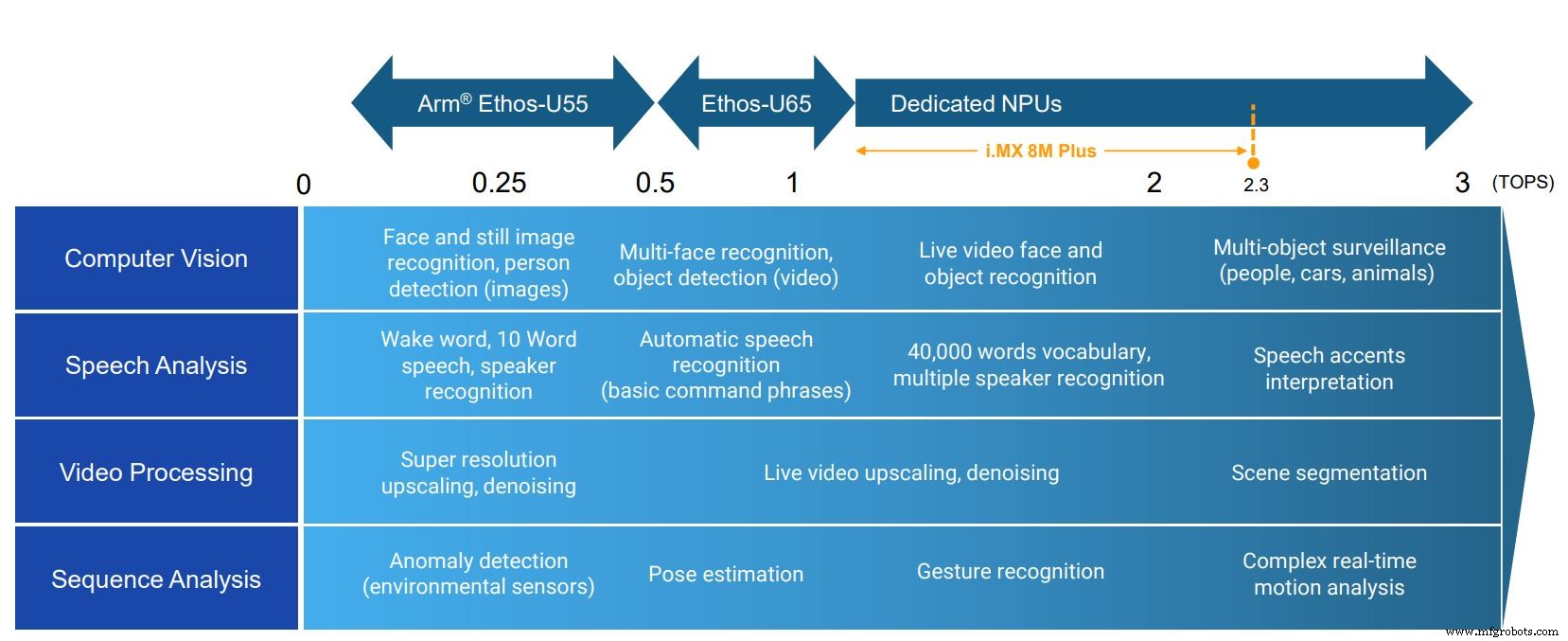

Существующий продукт Arm microNPU, Ethos-U55, выпущенный в феврале 2020 года, нацелен на продукты класса микроконтроллеров наряду с ядрами Cortex-M. Он обеспечивает ускорение до 0,5 TOPS (на основе меньшей геометрии, такой как 16 или 7 нм, работающая на частоте 1 ГГц), от 3 до 256 единиц с умножением и накоплением (MAC). В портфолио Arm также есть Ethos-N77, N57 и N37, которые предлагают 4, 2 и 1 TOPS соответственно.

Ethos-U65 разработан для поддержания энергоэффективности Ethos-U55 при одновременном удвоении доступных MAC - до 512 параллельных MAC на 1 ГГц - в общей сложности 1 TOPS. Эта комбинация мощности / производительности специально предназначена для использования вместе с ядрами Cortex-A в устройствах класса прикладных процессоров. По словам Arm, встроенная поддержка операторов машинного обучения в линейке Ethos-U также была обновлена и расширена.

Ведущий лицензиат

Ведущий технологический партнер (и ведущий лицензиат) NXP тесно сотрудничал с Arm над определением аспектов Ethos-U65 на системном уровне и заявила, что интегрирует Ethos-U65 IP в свое следующее поколение процессоров приложений i.MX.

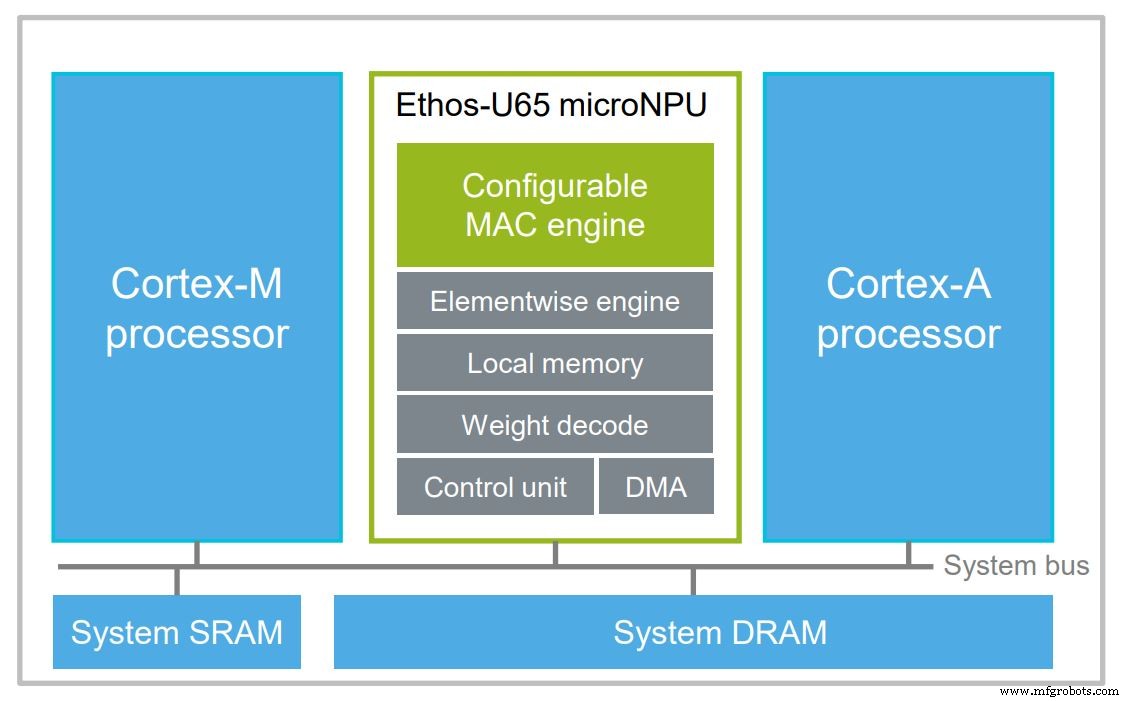

Архитектура, которую NXP разработала для процессора приложений с microNPU, использует ядра Cortex-A и Cortex-M (Изображение:NXP)

Архитектура, которую NXP имеет в виду для процессора приложений искусственного интеллекта, предполагает, что микропроцессор Ethos-U65 будет располагаться рядом с ядрами Cortex-M и Cortex-A, пояснил Бен Эккерманн, главный инженер подразделения аппаратного обеспечения искусственного интеллекта и машинного обучения, NXP. Cortex-A запускает приложение, обрабатывая драйверы (скажем) для микрофона или камеры и представляя рабочую нагрузку NPU. MicroNPU и Cortex-M вычисляют рабочую нагрузку машинного обучения и возвращают ответ в Cortex-A.

«Так же, как Ethos-U55, [Ethos-U65] полагается на то, что процессор Cortex-M находится где-то поблизости в системе, на случай, если есть операторы машинного обучения из нейронной сети, которые не имеет смысла полностью выгружать в аппаратном обеспечении, - сказал Эккерманн. «Есть много операторов машинного обучения, которые редко вызываются и могут не оправдывать свою аппаратную реализацию».

По словам Эккермана, гибкость, предлагаемая Cortex-M в этой конфигурации, также позволяет в определенной степени ориентироваться на будущее.

U65 получил более широкие внутренние системные шины, чем U55, и был адаптирован для работы с дополнительной буферизацией и задержкой, связанной с DRAM (обычно в системах, использующих процессоры приложений, тогда как системы Cortex-M обычно используют SRAM).

Заполнение портфолио

NXP пополняет свой портфель SoC с поддержкой AI.

Ранее анонсированные компанией процессоры приложений i.MX 8M + имеют блок ускорителя NPU AI наряду с двумя или четырьмя ядрами Cortex-A53. IP NPU, входящий в эти продукты, не от Arm. Это дизайн Verisilicon, который предлагает 2,3 TOPS, что достаточно для сегментации сцены, видео в реальном времени, распознавания лиц и объектов или интерпретации акцентов речи. В нижней части спектра микроконтроллеры NXP с NPU Arm Ethos-U55 могут обрабатывать обнаружение человека, определение слова пробуждения и шумоподавление видео.

Продукты с поддержкой Ethos-U65 будут находиться между этими двумя категориями продуктов, обрабатывая приложения AI, такие как распознавание нескольких лиц, более сложное распознавание речи или оценка позы. Поэтому любые новые продукты в этой категории не будут дублировать i.MX 8M +, сказал Эккерманн.

Объем вычислений, необходимых для различных приложений AI (ось x) и соответствующего NPU (Изображение:NXP)

>> Эта статья была первоначально опубликована на наш дочерний сайт EE Times.

Встроенный

- Arm позволяет настраивать инструкции для ядер Cortex-M

- Cervoz:ультратонкое хранилище NVMe для встраиваемых промышленных приложений

- CEVA:AI-процессор второго поколения для глубоких рабочих нагрузок нейронных сетей

- Многоядерный процессор объединяет блок нейронной обработки

- Специализированные процессоры ускоряют рабочие нагрузки ИИ конечных точек

- Индуктивный датчик положения для промышленных двигателей обеспечивает высокую скорость и точность

- Горизонт Манхэттена:компактный ARM COM с NXP i.MX 8MM

- Логическая технология:плата NXP iMX8M COM для четырехъядерного процессора ARM

- LCE предлагает надежный курс для менеджеров

- Контейнерные сборки для руки на x86