Схема затвора CMOS

До этого момента наш анализ транзисторных логических схем ограничивался TTL парадигма проектирования, при которой используются биполярные транзисторы, и общая стратегия «плавающих» входов эквивалентна «высокому» (подключенному к V cc ) входов - и, соответственно, допуск выходных каскадов с «открытым коллектором» - сохраняется. Однако это не единственный способ построить логические ворота.

Полевые транзисторы

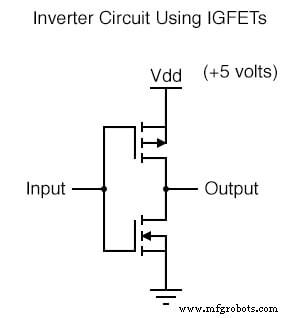

Полевые транзисторы, особенно с изолированным затвором, могут быть использованы при разработке схем затвора. Будучи устройствами с управлением по напряжению, а не по току, IGFET, как правило, позволяют создавать очень простые схемы. Возьмем, к примеру, следующую схему инвертора, построенную с использованием P- и N-канальных IGFET:

Обратите внимание на «V dd ”На положительной клемме источника питания. Этот ярлык соответствует тому же соглашению, что и «V cc . ”В цепях TTL:это постоянное напряжение, приложенное к стоку полевого транзистора относительно земли.

Полевые транзисторы в схемах затворов

Низкий ввод

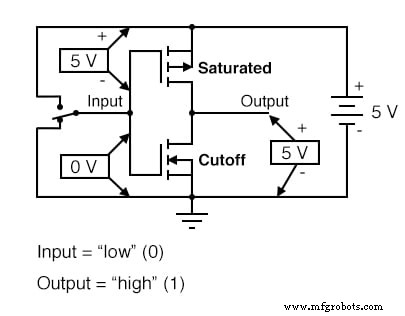

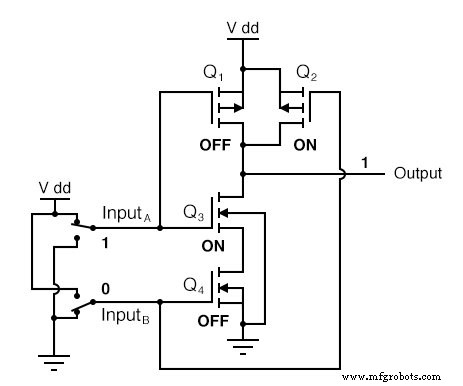

Давайте подключим эту схему затвора к источнику питания и входному переключателю и исследуем ее работу. Обратите внимание, что эти IGFET-транзисторы относятся к E-типу (режим улучшения) и поэтому обычно выключены . устройств.

Требуется приложенное напряжение между затвором и стоком (фактически, между затвором и подложкой) правильной полярности для их смещения на .

Верхний транзистор представляет собой P-канальный IGFET. Когда канал (подложка) сделан более положительным, чем затвор (отрицательный затвор по отношению к подложке), канал усиливается, и между истоком и стоком разрешается ток.

Итак, на иллюстрации выше верхний транзистор включен. Нижний транзистор, имеющий нулевое напряжение между затвором и подложкой (истоком), находится в нормальном режиме: выключен .

Таким образом, действие этих двух транзисторов таково, что выходной вывод схемы затвора имеет прочное соединение с V dd и очень высокое сопротивление заземления. Это делает выход «высоким» (1) для «низкого» (0) состояния входа.

Высокий ввод

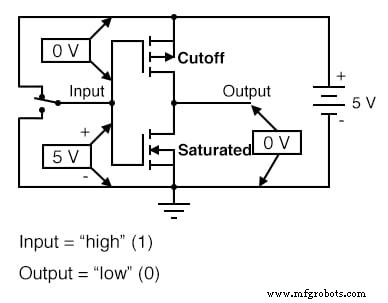

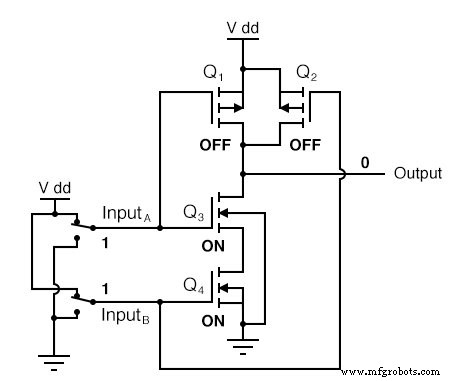

Затем мы переместим переключатель ввода в другое положение и посмотрим, что произойдет:

Теперь нижний транзистор (N-канал) насыщен, потому что он имеет достаточное напряжение правильной полярности, приложенное между затвором и подложкой (каналом), чтобы включить его (положительный на затворе, отрицательный на канале). Верхний транзистор, к которому между затвором и подложкой приложено нулевое напряжение, находится в нормальном режиме: выключен .

Таким образом, выходной сигнал этой схемы затвора теперь «низкий» (0). Ясно, что эта схема демонстрирует поведение инвертора или НЕ затвора.

Дополнительные металлооксидные полупроводники (CMOS)

Использование полевых транзисторов вместо биполярных транзисторов значительно упростило конструкцию затвора инвертора. Обратите внимание, что выход этого затвора никогда не «плавает», как в случае с простейшей схемой TTL:он имеет естественную конфигурацию «тотем-полюс», способную как получать, так и понижать ток нагрузки.

Ключом к элегантному дизайну этой схемы ворот является дополнительный использование как P-, так и N-канальных IGFET. Поскольку IGFET более известны как MOSFET ( M etal- O xide- S электронный провод F ield E ffect T транзистор), и в этой схеме используются как P-, так и N-канальные транзисторы вместе, общая классификация схем затвора, подобная этой, - CMOS : C дополнительный M etal O xide S электронный провод.

CMOS Gates:проблемы и решения

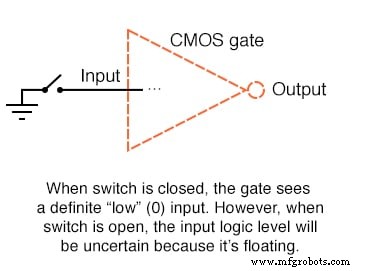

КМОП-схемы не страдают от неотъемлемой нелинейности полевых транзисторов, потому что как цифровые схемы их транзисторы всегда работают либо в насыщенном или обрезка режимах и никогда в активном режим. Однако их входы чувствительны к высоким напряжениям, генерируемым источниками электростатического (статического электричества), и даже могут быть активированы в «высокое» (1) или «низкое» (0) состояния источниками паразитного напряжения, если они оставлены плавающими.

По этой причине не рекомендуется разрешать входу логического элемента CMOS плавать ни при каких обстоятельствах. Обратите внимание, что это сильно отличается от поведения логического элемента TTL, где плавающий вход безопасно интерпретировался как «высокий» (1) логический уровень.

Проблемы CMOS с плавающими входами

Это может вызвать проблему, если вход логического элемента КМОП управляется переключателем на один ход, когда в одном состоянии вход жестко подключен к V dd или земля, а другое состояние имеет вход плавающий (ни к чему не подключен):

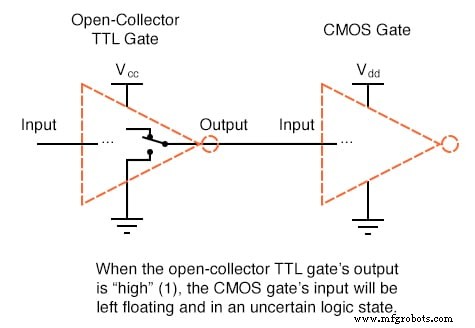

Кроме того, эта проблема возникает, если вход затвора CMOS управляется открытым коллектором . ТТЛ ворота. Поскольку выход такого TTL-затвора плавает, когда он становится «высоким» (1), вход CMOS-затвора останется в неопределенном состоянии:

Решение для плавающих входов

Подтягивающие резисторы

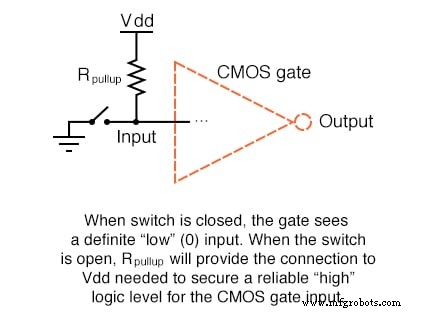

К счастью, есть простое решение этой дилеммы, которое часто используется в логических схемах КМОП. Всякий раз, когда однонаправленный переключатель (или любой другой выход ворот, неспособный использовать оба источник и потребляющий ток) используется для управления входом CMOS, резистор подключен к V dd или земля может использоваться для обеспечения стабильного логического уровня для состояния, в котором выход управляющего устройства является плавающим.

Номинал этого резистора не критичен:обычно достаточно 10 кОм. При использовании для обеспечения «высокого» (1) логического уровня в случае плавающего источника сигнала этот резистор известен как подтягивающий резистор . :

Понижающие резисторы

Когда такой резистор используется для обеспечения «низкого» (0) логического уровня в случае плавающего источника сигнала, он известен как понижающий резистор . . Опять же, значение сопротивления понижающего сопротивления не критично:

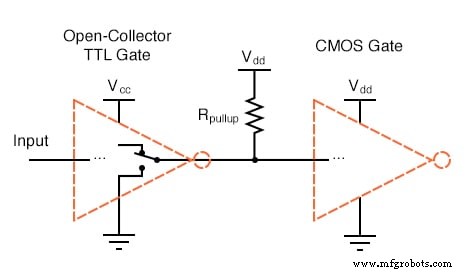

Поскольку выходы TTL с открытым коллектором всегда опускаются, а не истока, ток, подтягивается вверх резисторы необходимы при подключении такого выхода к входу затвора CMOS:

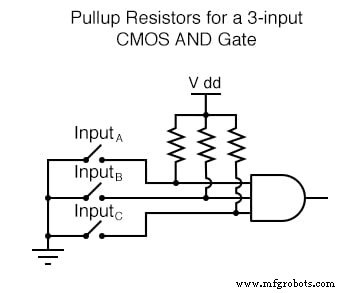

Множественные подтягивающие и понижающие резисторы

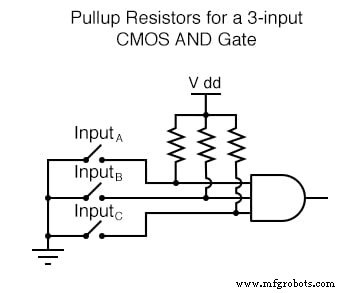

Хотя все вентили CMOS, использованные в предыдущих примерах, были инверторами (с одним входом), тот же принцип подтягивающих и понижающих резисторов применяется к вентилям CMOS с несколькими входами. Конечно, для каждого входа затвора потребуется отдельный подтягивающий или понижающий резистор:

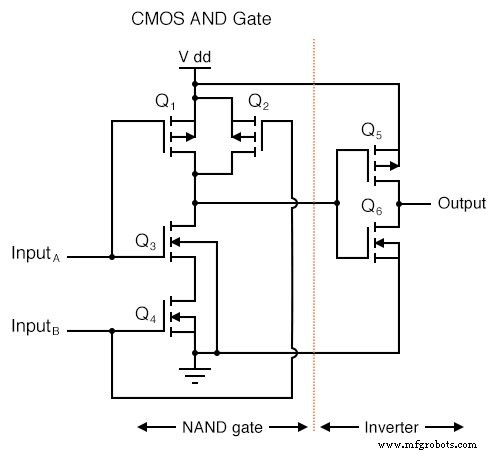

Это подводит нас к следующему вопросу:как разработать вентили CMOS с несколькими входами, такие как AND, NAND, OR и NOR? Неудивительно, что ответ на этот вопрос демонстрирует простоту конструкции, во многом напоминающую конструкцию КМОП-инвертора по сравнению с его эквивалентом TTL.

CMOS NAND Gates

Например, вот схематическая диаграмма для ворот CMOS NAND:

Обратите внимание, как транзисторы Q 1 и Q 3 напоминают последовательно соединенную комплементарную пару из схемы инвертора. Оба управляются одним и тем же входным сигналом (вход A), верхний транзистор отключается, а нижний транзистор включается, когда на входе «высокий» уровень (1), и наоборот.

Обратите внимание также, как транзисторы Q 2 и Q 4 аналогичным образом управляются одним и тем же входным сигналом (вход B), и как они также будут демонстрировать одинаковое поведение включения / выключения для тех же логических уровней входа. Верхние транзисторы обеих пар (Q 1 и Q 2 ) имеют параллельные выводы истока и стока, а нижние транзисторы (Q 3 и Q 4 ) соединены последовательно.

Это означает, что вывод будет «высоким» (1), если либо верхний транзистор насыщается и переходит в состояние «низкий» (0), только если оба нижние транзисторы насыщаются.

Поведение схемы CMOS для всех логических входов

Следующая последовательность иллюстраций показывает поведение этого логического элемента И-НЕ для всех четырех возможных уровней входной логики (00, 01, 10 и 11):

CMOS И вентиль

Как и в случае с логическим элементом И-НЕ ТТЛ, схему затвора И-НЕ КМОП можно использовать в качестве отправной точки для создания логического элемента И. Все, что нужно добавить, это еще один каскад транзисторов для инвертирования выходного сигнала:

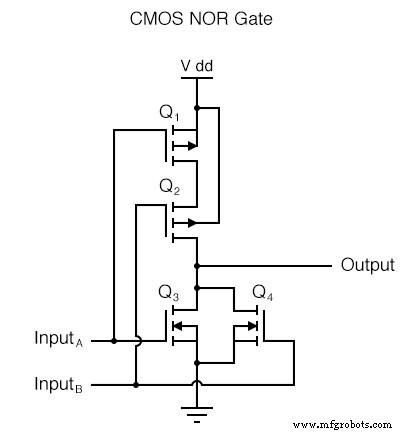

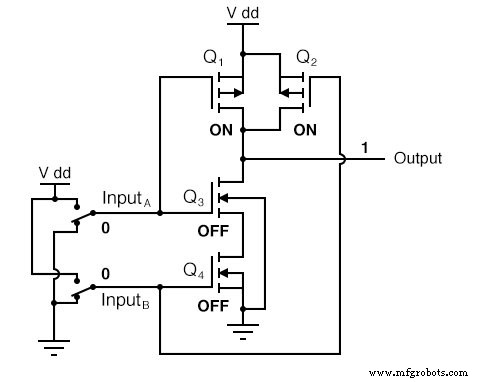

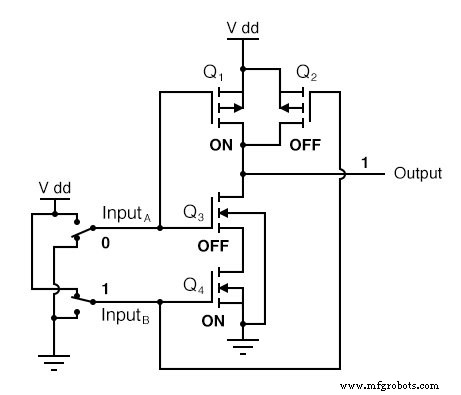

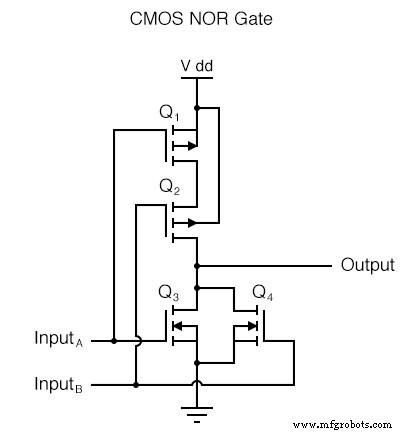

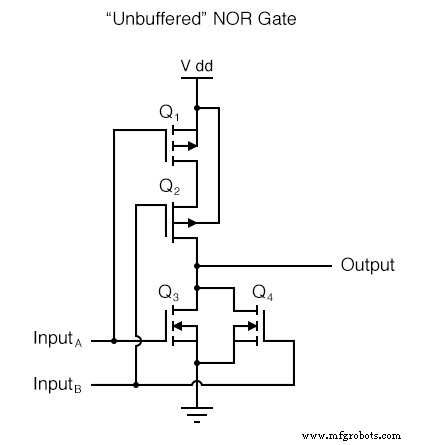

CMOS NOR Gates

Схема затвора КМОП ИЛИ-НЕ использует четыре полевых МОП-транзистора, как и затвор И-НЕ, за исключением того, что его транзисторы расположены по-другому. Вместо двух параллельных источников (верхние) транзисторы, подключенные к V dd и два последовательно соединенных тонущего (нижний) транзисторы, подключенные к земле, затвор ИЛИ-НЕ использует два последовательно соединенных транзистора-источника и два параллельно подключенных транзистора-потребителя, например:

Как и в случае с затвором И-НЕ, транзисторы Q 1 и Q 3 работают как дополнительная пара, как и транзисторы Q 2 и Q 4 . Каждая пара управляется одним входным сигналом. Если либо введите A или вход B - высокий (1), по крайней мере, один из нижних транзисторов (Q 3 или Q 4 ) будет насыщенным, что сделает выходной сигнал «низким» (0).

Только в случае обоих входы, находящиеся на «низком уровне» (0), оба нижних транзистора будут в режиме отсечки, а оба верхних транзистора будут насыщены, что является условиями, необходимыми для перехода выхода на «высокий уровень» (1). Это поведение, конечно же, определяет логическую функцию ИЛИ-НЕ.

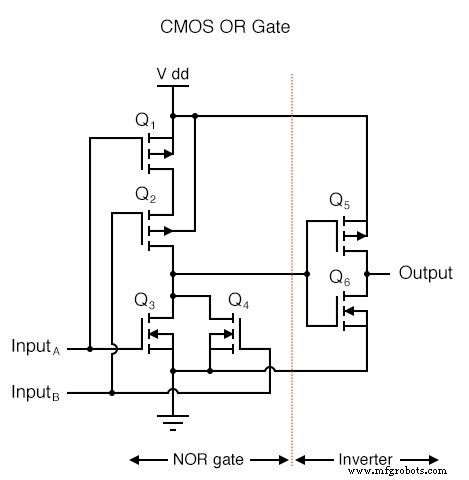

CMOS OR Gates

Функция ИЛИ может быть создана из основного логического элемента ИЛИ-ИЛИ с добавлением инверторного каскада на выходе:

TTL против CMOS:преимущества и недостатки

Поскольку кажется, что любой вентиль, который можно построить с использованием технологии TTL, может быть продублирован в CMOS, почему эти два «семейства» логических схем все еще сосуществуют? Ответ заключается в том, что и TTL, и CMOS имеют свои уникальные преимущества.

В первую очередь в списке сравнений между TTL и CMOS стоит вопрос энергопотребления. В этом показателе производительности CMOS является бесспорным победителем. Поскольку дополнительные пары P- и N-канальных полевых МОП-транзисторов схемы затвора КМОП (в идеале) никогда не проводят одновременно, ток, потребляемый схемой от V dd , практически отсутствует. источник питания, за исключением того, какой ток необходим для подачи тока в нагрузку. TTL, с другой стороны, не может работать без постоянного тока из-за требований смещения биполярных транзисторов, из которых он сделан.

Однако есть нюанс к этому преимуществу. В то время как рассеиваемая мощность затвора TTL остается довольно постоянной независимо от его рабочего состояния (состояний), затвор CMOS рассеивает больше энергии по мере увеличения частоты его входного сигнала (ов). Если вентиль CMOS работает в статическом (неизменном) состоянии, он рассеивает нулевую мощность (в идеале).

Однако схемы затвора КМОП потребляют переходный ток во время каждого переключения выходного состояния с «низкого» на «высокое» и наоборот. Таким образом, чем чаще вентиль CMOS переключает режимы, тем чаще он будет потреблять ток от V dd питания, следовательно, большее рассеивание мощности на более высоких частотах.

Преимущества CMOS

КМОП-затвор также потребляет гораздо меньше тока с выхода управляющего затвора, чем затвор ТТЛ, потому что полевые МОП-транзисторы являются устройствами с управлением по напряжению, а не по току. Это означает, что один вентиль может управлять гораздо большим количеством входов CMOS, чем входов TTL. Мера того, сколько входов затвора может управлять одним выходом затвора, называется разветвлением . .

Еще одно преимущество, которым обладают конструкции затвора CMOS по сравнению с TTL, - это гораздо более широкий допустимый диапазон напряжений источника питания. В то время как ворота TTL ограничены источником питания (V cc ) напряжением от 4,75 до 5,25 вольт, вентили CMOS обычно могут работать при любом напряжении от 3 до 15 вольт!

Причина этого несоответствия в напряжениях источника питания - соответствующие требования смещения MOSFET по сравнению с транзисторами с биполярным переходом. МОП-транзисторы управляются исключительно напряжением на затворе (по отношению к подложке), в то время как полевые транзисторы BJT управляются по току . устройств.

Сопротивление цепи затвора TTL точно рассчитано для правильных токов смещения с учетом регулируемого источника питания 5 В. Любые значительные колебания в этом напряжении источника питания приведут к неправильным токам смещения транзистора, что в свою очередь приведет к ненадежной (непредсказуемой) работе.

Единственное влияние, которое изменения напряжения источника питания оказывают на затвор КМОП, - это определение напряжения «высокого» (1) состояния. Для затвора CMOS, работающего при напряжении источника питания 15 В (V dd ), входной сигнал должен быть близким к 15 В, чтобы считаться «высоким» (1). Пороговое значение напряжения для «низкого» (0) сигнала остается прежним:около 0 вольт.

Недостатки CMOS

Одним из явных недостатков CMOS является низкая скорость по сравнению с TTL. Входные емкости затвора CMOS намного, намного больше, чем у сопоставимого затвора TTL - из-за использования полевых МОП-транзисторов, а не BJT, - и поэтому затвор CMOS будет медленнее реагировать на переход сигнала (от низкого к высокому или наоборот), чем TTL-вентиль, при прочих равных.

Постоянная времени RC, образованная сопротивлением цепи и входной емкостью затвора, имеет тенденцию препятствовать быстрому нарастанию и спаду цифрового логического уровня, тем самым ухудшая высокочастотные характеристики.

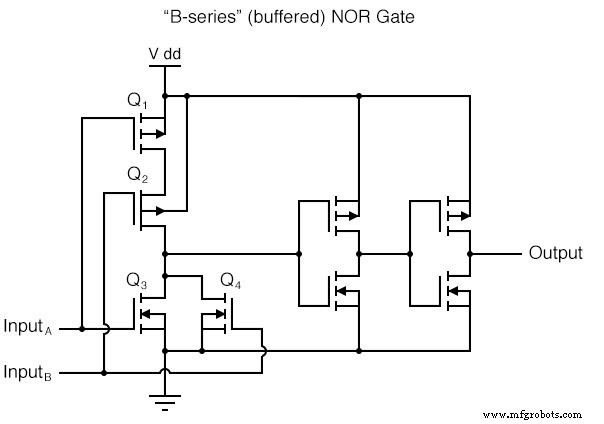

Стратегии борьбы с недостатками

Стратегия минимизации этого неотъемлемого недостатка схемы затвора КМОП заключается в «буферизации» выходного сигнала с помощью дополнительных транзисторных каскадов для увеличения общего коэффициента усиления устройства по напряжению. Это обеспечивает более быстрое изменение выходного напряжения (от высокого к низкому или от низкого к высокому) для входного напряжения, медленно переходящего из одного логического состояния в другое.

Рассмотрим этот пример «небуферизованного» логического элемента ИЛИ-НЕ по сравнению с «буферизованным» или B-серии , Ворота NOR:

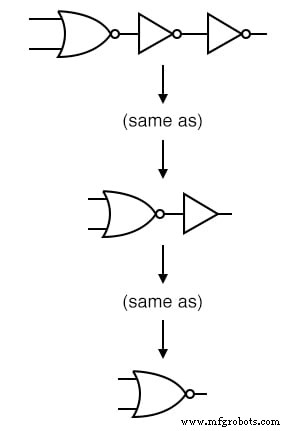

По сути, усовершенствованная конструкция серии B добавляет два инвертора к выходу простой схемы ИЛИ-ИЛИ. Это бесполезно с точки зрения цифровой логики, поскольку два каскадных инвертора просто отменяют:

Однако добавление этих каскадов инвертора в схему действительно служит цели увеличения общего усиления напряжения, делая выход более чувствительным к изменениям входного состояния, работая над преодолением присущей медлительности, вызванной входной емкостью затвора КМОП.

ОБЗОР:

- Логические вентили КМОП сделаны из транзисторов IGFET (MOSFET), а не из транзисторов с биполярным переходом.

- Входы затвора CMOS чувствительны к статическому электричеству. Они могут быть повреждены высоким напряжением и могут принимать любой логический уровень, если оставлены плавающими.

- Подтягивание и раскрывающееся меню резисторы используются для предотвращения плавающего входа затвора CMOS, если он приводится в действие источником сигнала, способным только обеспечивать или принимать ток.

- КМОП-затворы рассеивают гораздо меньше энергии, чем эквивалентные затворы ТТЛ, но их рассеиваемая мощность увеличивается с увеличением частоты сигнала, тогда как рассеиваемая мощность затвора ТТЛ примерно постоянна в широком диапазоне рабочих условий.

- Входы затвора КМОП потребляют гораздо меньше тока, чем входы ТТЛ, поскольку полевые МОП-транзисторы управляются напряжением, а не током.

- CMOS-вентили могут работать в гораздо более широком диапазоне напряжений источника питания, чем TTL:обычно от 3 до 15 вольт против 4,75 до 5,25 вольт для TTL.

- CMOS-вентили, как правило, имеют гораздо более низкую максимальную рабочую частоту, чем TTL-вентили, из-за входной емкости, вызванной вентилями MOSFET.

- Серия B КМОП вентили имеют «буферизованные» выходы для увеличения усиления напряжения от входа к выходу, что приводит к более быстрой реакции выхода на изменения входного сигнала. Это помогает преодолеть присущую КМОП-логическим элементам медлительность из-за входной емкости полевого МОП-транзистора и постоянной времени RC, возникающей при этом.

СВЯЗАННЫЕ РАБОЧИЕ ТАБЛИЦЫ:

-

Таблица полевых транзисторов с изолированным затвором

-

Таблица CMOS Logic Gates

Промышленные технологии

- Как построить текущую схему зеркала

- Базовая функция затвора

- Защелка NOR Gate S-R

- Транзисторы, биполярные

- Транзисторы, переходный полевой транзистор (JFET)

- Транзисторы, полевой эффект с изолированным затвором (IGFET или MOSFET)

- Транзисторы, гибридные

- Интегральные схемы

- Введение в полевые транзисторы с изолированным затвором

- Моделирование уровня ворот