Программные инструменты переносят код GPU на FPGA для приложений AI

Запуск программного обеспечения AI Mipsology работает с Xilinx, чтобы позволить FPGA заменять графические процессоры в приложениях AI-ускорителей, используя только одну дополнительную команду. Программное обеспечение Mipsology с нулевыми усилиями, Zebra, преобразует код графического процессора для работы на вычислительной машине Mipsology AI на ПЛИС без каких-либо изменений кода или переобучения.

Xilinx объявила сегодня, что поставляет Zebra последнюю сборку своих карт Alveo U50 для центров обработки данных. Zebra уже поддерживает ускорение вывода на других платах Xilinx, включая Alveo U200 и Alveo U250.

Последняя сборка платы ускорителя для центра обработки данных Alveo U50 от Xilinx теперь поставляется с программным обеспечением Mipsology Zebra для преобразования кода AI GPU для работы на FPGA (Изображение:Xilinx)

«Уровень ускорения, который Zebra привносит в наши карты Alveo, заставляет стыдиться ускорителей ЦП и ГП», - сказала Рамин Роан, вице-президент Xilinx по маркетингу. «В сочетании с Zebra, Alveo U50 удовлетворяет потребности рабочих нагрузок ИИ в гибкости и производительности и предлагает преимущества высокой пропускной способности и низкой задержки для любого развертывания».

Plug-and-play

Исторически сложилось так, что программирование FPGA для неспециалистов было заведомо сложным, но Mipsology хочет превратить FPGA в решение plug-and-play, такое же простое в использовании, как CPU или GPU. Идея состоит в том, чтобы максимально упростить переход с других типов ускорения на FPGA.

«Лучший способ увидеть [Mipsology] - это то, что мы создаем программное обеспечение, которое работает поверх FPGA, чтобы сделать их прозрачными так же, как Nvidia сделала Cuda CuDNN, чтобы сделать GPU полностью прозрачным для пользователей AI», - сказал генеральный директор Mipsology Людовик Ларзул. , в интервью EE Times .

Что особенно важно, это может быть сделано неспециалистами, без глубоких знаний в области искусственного интеллекта или FPGA, поскольку для перехода не требуется переобучение модели.

«Простота использования очень важна, потому что, когда вы смотрите на человеческие проекты ИИ, у них часто нет доступа к команде ИИ, которая разрабатывает нейронную сеть», - сказал Ларзул. «Обычно, если кто-то устанавливает систему роботов или систему видеонаблюдения… у них есть другие команды или другие стороны, которые разрабатывают нейронные сети и обучают их. И как только они получат [обученную модель], они не захотят ее менять, потому что у них нет опыта ».

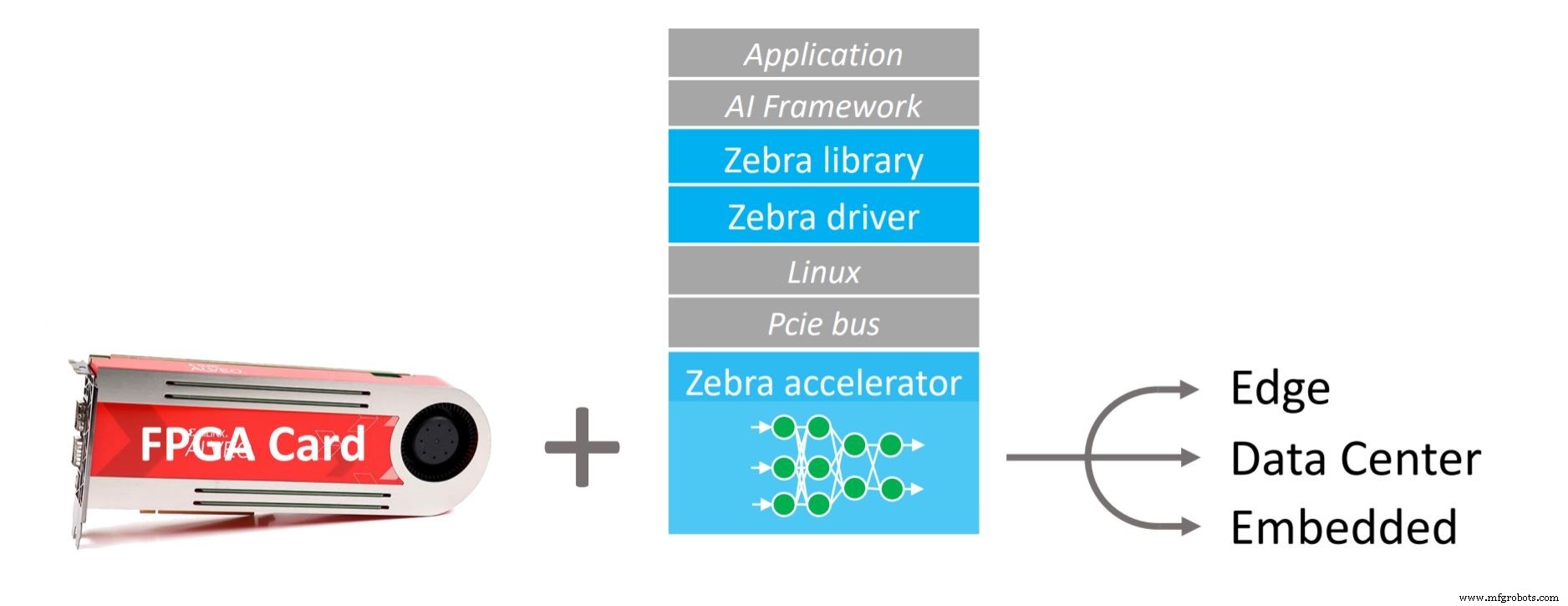

Стек Зебры. Технология применима в центрах обработки данных, периферийных и встроенных приложениях (Изображение:Mipsology)

По сравнению с Vitis

Зачем Xilinx поддерживать стороннее программное обеспечение, если у него уже есть комплексное решение, призванное сделать FPGA доступными как для специалистов по данным, так и для разработчиков программного обеспечения (а именно, Vitis)?

«Идея в одном предложении:у нас дела идут лучше», - сказал Ларзул. «Еще одно предложение:наши работы».

Mipsology не использует какие-либо части Vitis и не связывается с ним каким-либо образом, а также не использует XDNN, ускоритель нейронной сети Xilinx. У Mipsology есть собственный вычислительный движок в Zebra, который поддерживает существующие модели сверточной нейронной сети (CNN) клиентов, в отличие от XDNN, который, по словам Ларзула, поддерживает множество демонстраций, но менее подходит для специализированных нейронных сетей. По его словам, из-за этого запуск и запуск пользовательских сетей с XDNN был «болезненным». Хотя XDNN может конкурировать в приложениях, где нет угрозы со стороны графических процессоров, Zebra предназначена для того, чтобы позволить ПЛИС опередить графические процессоры за счет производительности, стоимости и простоты использования.

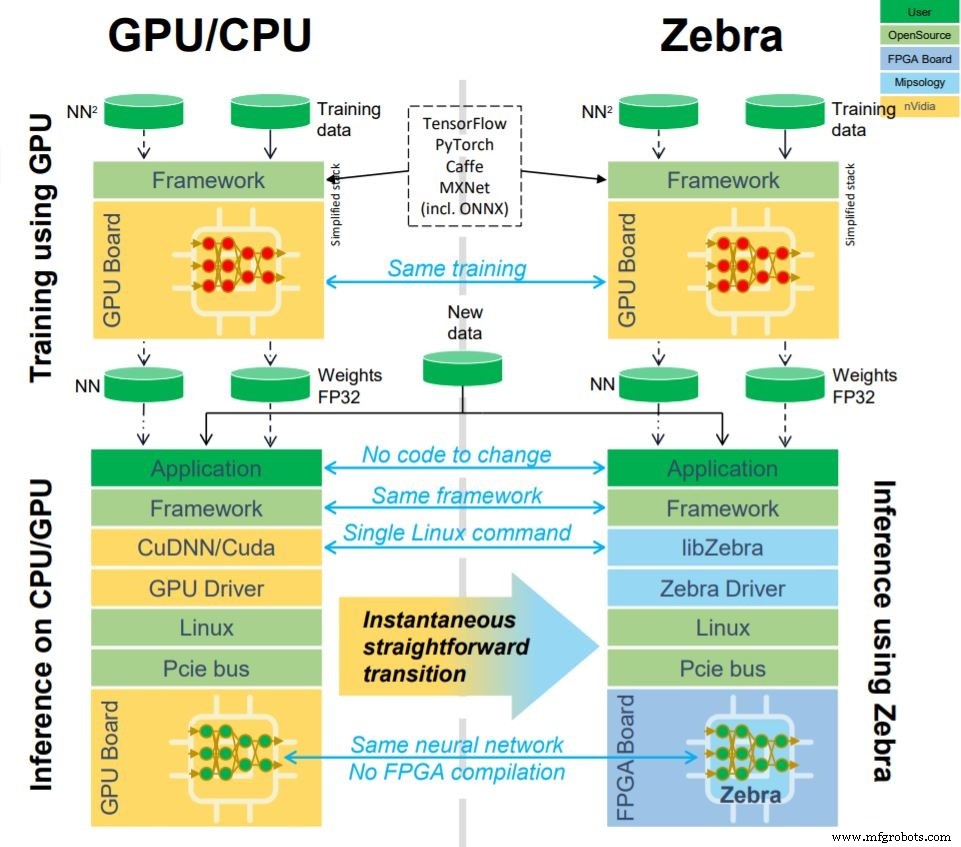

Подробнее о стеке Zebra. Цель состоит в том, чтобы сделать FPGA более простым переключением с графических процессоров или процессоров на ускорение ИИ, максимально скрывая аппаратное обеспечение (Изображение:Mipsology)

По словам Ларзула, большинство заказчиков отказываются от решений на базе графических процессоров из-за стоимости.

«Они хотят снизить стоимость оборудования, но не хотят переделывать нейронную сеть», - сказал он. «Существуют единовременные расходы [которых можно избежать], потому что мы можем прозрачно заменять графические процессоры, и при этом не требуется повторного обучения или модификации нейронной сети».

По словам Ларзула, ПЛИС также предлагают надежность, отчасти потому, что они менее агрессивны по отношению к кремниевой недвижимости и часто работают холоднее, чем другие типы ускорителей, включая графические процессоры. Это особенно важно в центре обработки данных, где затраты на долгосрочное обслуживание значительны.

«Общая стоимость владения - это не просто цена платы», - сказал Ларзул. «Кроме того, необходимо убедиться, что система работает и работает».

Zebra также стремится заставить ПЛИС соревноваться в производительности. По словам Ларзула, хотя FPGA обычно предлагают меньше TOPS (тера операций в секунду), чем другие ускорители, они могут использовать эти TOPS более эффективно благодаря тщательно разработанному вычислительному механизму Zebra.

Людовик Ларзул (Изображение:Mipsology)

«Это то, что большинство стартапов ASIC, ускоряющих ИИ, забыли - они делают очень большой кусок кремния, пытаясь упаковать больше TOPS, но они не думали о том, как вы сопоставите свою сеть с этим, чтобы быть эффективными. », - сказал он, отметив, что движок Zebra на базе FPGA способен обрабатывать больше изображений в секунду, чем графический процессор с 6-кратным количеством TOPS.

Как этого добиться? Хотя Ларзул не сообщил точных деталей, он сказал, что они не полагаются на обрезку, поскольку снижение точности слишком велико, чтобы быть приемлемым без переобучения. Они не используют экстремальное квантование (ниже 8 бит) по той же причине.

Движок Zebra ускоряет CNN, которые сегодня в основном используются приложениями для обработки изображений и видео, но Zebra также может быть применена к BERT (модели обработки естественного языка Google), в которой используются аналогичные математические концепции. Будущие итерации Zebra могут охватывать другие типы нейронных сетей, включая LSTM (долгую краткосрочную память) и RNN (рекуррентные нейронные сети), но этого труднее достичь, поскольку RNN математически более разнообразны.

Команда EVE

Компания Mipsology была основана в 2015 году, около 30 человек работали над исследованиями и разработками во Франции, а небольшая команда в Калифорнии в основном занималась развитием бизнеса. Компания получила финансирование на общую сумму 7 млн долларов, из которых 2 млн долларов были присуждены на конкурсе инноваций, проведенном правительством Франции в 2019 году.

Основная команда Mipsology работает в EVE - компании-эмуляторах ASIC, которую Synopsys приобрела в 2012 году для своих продуктов с аппаратной поддержкой ZeBu (Zero Bug), которые в то время были конкурентом платформы проверки Cadence Palladium. По словам Ларзула, технология EVE использовалась почти всеми крупными компаниями, производящими ASIC, для проверки ASIC на этапе проектирования; в этой технологии использовались тысячи ПЛИС, соединенных вместе для воспроизведения поведения ASIC.

Mipsology имеет 12 заявленных патентов и тесно сотрудничает с Xilinx, а также совместим с картами ускорителей сторонних производителей, такими как карты малого форм-фактора Western Digital (SFF U.2) и карты Advantech, такие как Vega-4001.

>> Эта статья была первоначально опубликована на наш дочерний сайт EE Times.

Встроенный

- ST:оценочный комплект безопасных элементов с готовым к использованию программным обеспечением для приложени…

- PPA для приложений электронной мобильности

- Идеальное применение для пневматических приводов

- 4 типа инструментов для майнинга

- Типичные области применения суппортных тормозов

- Военные применения бронзовых сплавов

- Применения для алюминиевой бронзы C63200

- Для чего используется монель?

- Режущие инструменты для прецизионной обработки

- Важность взаимодействия в 3D-приложениях