Дебют нейроморфных ИИ-чипов для пиков нейронных сетей

Innatera, голландский стартап, создающий нейроморфные ускорители ИИ для пиков нейронных сетей , выпустила свои первые микросхемы, измерила их производительность и раскрыла детали их архитектуры.

Innatera, голландский стартап, создающий нейроморфные ускорители ИИ для наращивания нейронных сетей, выпустил свои первые микросхемы, измерил их производительность и раскрыл детали их архитектуры.

Компания также объявила, что соучредитель Cadence и Synopsys Альберто Сангиованни-Винчентелли присоединился к компании в качестве председателя совета директоров. Ветеран отрасли в настоящее время является профессором Калифорнийского университета в Беркли.

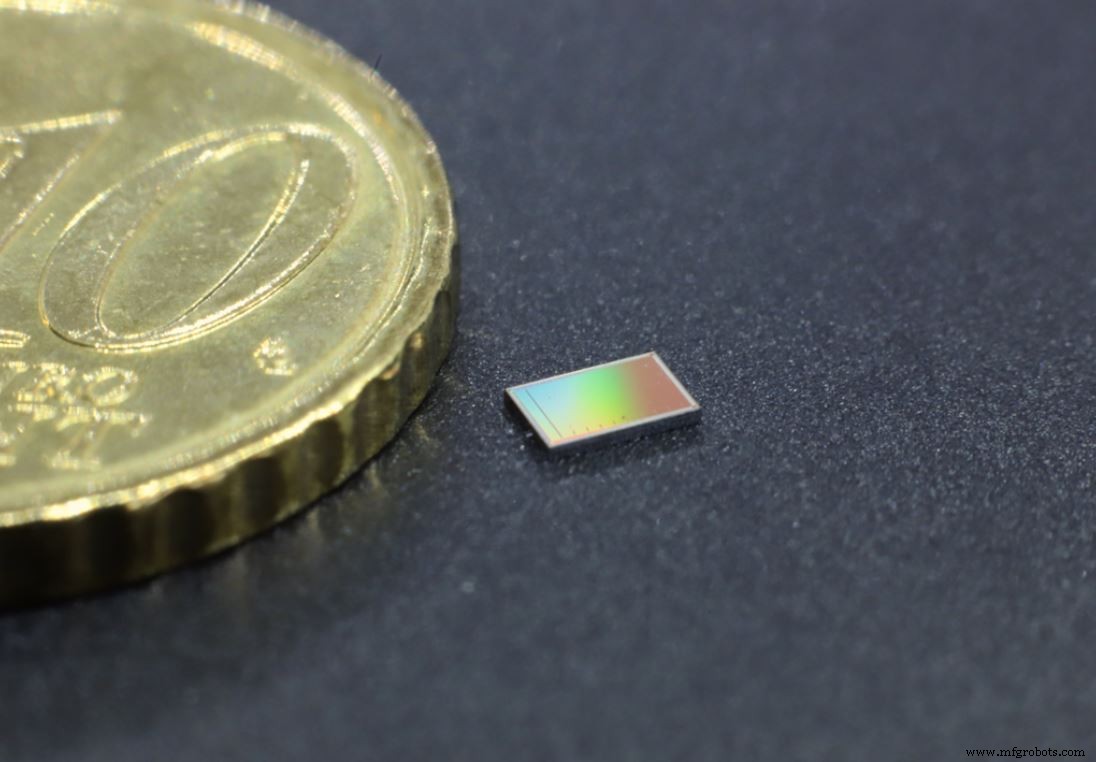

Чип Innatera разработан для ускорения различных SNN для приложений аудио, здравоохранения и радаров (Изображение:Innatera)

Чип Innatera разработан для ускорения всплесков нейронных сетей (SNN), типа нейроморфного алгоритма искусственного интеллекта, основанного на биологии мозга, который использует синхронизацию всплесков электрического сигнала для выполнения задач распознавания образов. SNN полностью отличаются по структуре от основных алгоритмов искусственного интеллекта и, следовательно, требуют специального оборудования для ускорения, но обычно они обеспечивают значительные преимущества в энергопотреблении и задержке для приложений на границе датчиков.

Большинство других компаний, работающих над улучшением алгоритмов и оборудования нейронных сетей (например, Prophesee), нацелены на изображения и видеопотоки. Innatera решила сосредоточиться на звуке (распознавание звука и речи), здоровье (мониторинг жизненно важных функций) и радаре (для случаев использования потребителями / IoT, таких как датчики падения пожилых людей, обеспечивающие конфиденциальность).

Марко Джейкобс (Изображение:Innatera)

«Эти датчики имеют данные временного ряда, а не изображения, которые очень параллельны», - сказал Марко Джейкобс, вице-президент Innatera по маркетингу и развитию бизнеса, в интервью EE Times . «Наш массив особенно хорош при обработке данных временных рядов… это хорошая технология. Кроме того, с точки зрения рынка, мы видим много интересных приложений в этой области и не так много решений, которые ее решают ».

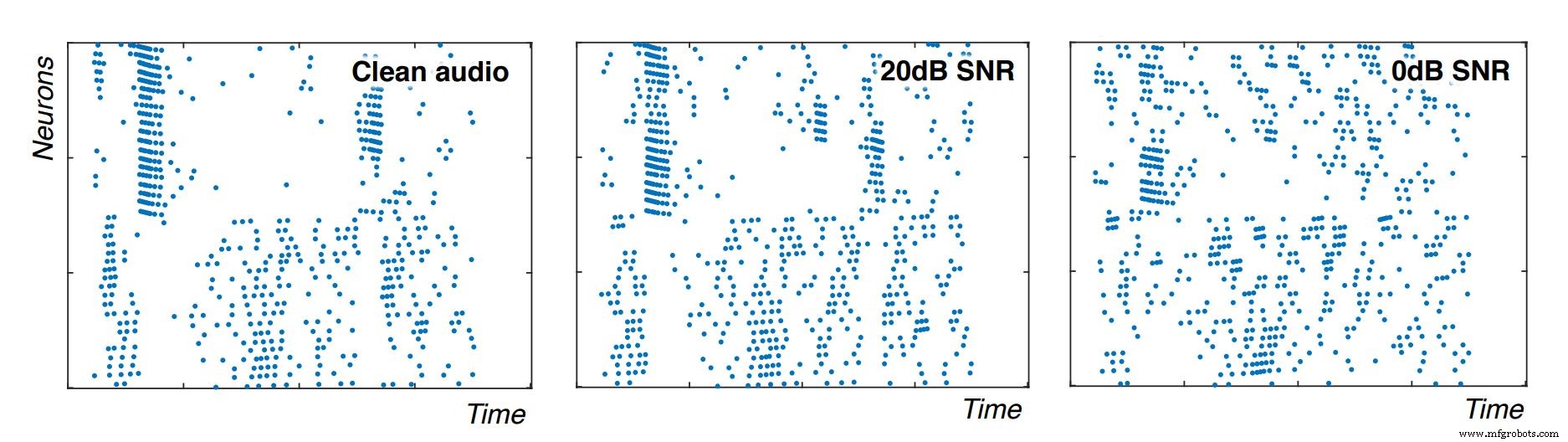

Еще одна общая черта этих трех приложений заключается в том, что, поскольку обработка требуется в узле датчика, диапазон мощности очень ограничен. В тестах Innatera каждый импульс (каждый нейрон, срабатывающий в ответ на входные данные) требовал менее пикоджоулей энергии - фактически, менее 200 фемтоджоулей в TSMC 28 нм, подтвердил Innatera. Это приближается к количеству энергии, используемой биологическими нейронами и синапсами. По словам генерального директора Innatera Сумита Кумара, типичному приложению для определения ключевых слов в звуке требуется менее 500 всплесков на один вывод, что приводит к «глубокому рассеянию мощности менее милливаттного уровня». В этом случае кластеры нейронов, срабатывающих вместе, представляют разные фонемы речи.

Кластеры срабатывания нейронов (здесь группы точек) представляют собой обнаружение фонем в речи. Поскольку входные данные содержат больше шума, в основном присутствуют те же кластеры, хотя их труднее обнаружить (Изображение:Innatera)

Архитектура обработки

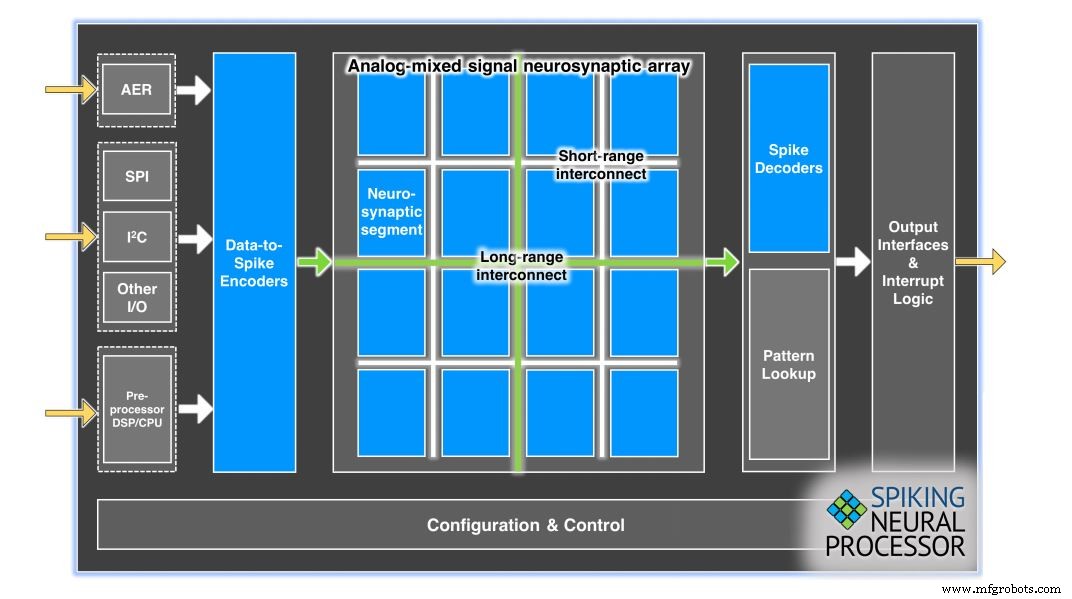

Нейронный процессор Innatera использует параллельный набор нейронов и синапсов для ускорения непрерывных SNN с помощью мелкозернистой временной динамики. Устройство представляет собой ускоритель аналоговых / смешанных сигналов, предназначенный для использования способности SNN включать понятие времени в процесс обработки данных.

Нейронный процессор Innatera включает в себя массивно-параллельный нейросинаптический массив, а также кодеры и декодеры импульсов (Изображение:Innatera)

Одним из ключевых аспектов вычислительной инфраструктуры Innatera является ее программируемость, что важно по двум причинам.

Во-первых, программирование различных SNN на микросхеме. Нейроны должны быть соединены гибким образом - мозг использует очень сложные топологии нейронных сетей для эффективной работы, что требует сложных соединений между нейронами, которые необходимо воссоздавать в кремнии.

Сумит Кумар (Изображение:Innatera)

Во-вторых, для оптимизации производительности. Вместо того, чтобы представлять информацию в виде битов в словах, в SNN информация представлена в виде точно рассчитанных по времени всплесков. Чтобы получить представление о данных, необходимо управлять временем всплесков на очень мелком уровне. Следовательно, нейроны и связи между ними (синапсы) должны демонстрировать сложное временное поведение. Это поведение можно настроить с помощью Innatera SDK для оптимизации производительности.

Innatera описывает свой чип как аналогово-смешанный сигнал или «аналоговый сигнал с цифровой поддержкой». Нейроны и синапсы реализованы в аналоговом кремнии для поддержания сверхнизкого энергопотребления. Аналоговая электроника также позволяет создавать сети с непрерывным временем (цифровая электроника потребует дискретизации). Это важно для SNN, потому что их природа означает, что они изначально имеют представление о времени и должны иметь возможность удерживать определенные состояния в течение определенного периода времени.

«Сделать это намного проще в аналоговой области - вам не нужно переносить сложность сохранения состояния в топологию сети», - сказал Кумар. «Наши вычислительные элементы естественным образом сохраняют эту информацию о состоянии. Это причина, по которой мы делаем что-то в аналоговой области ».

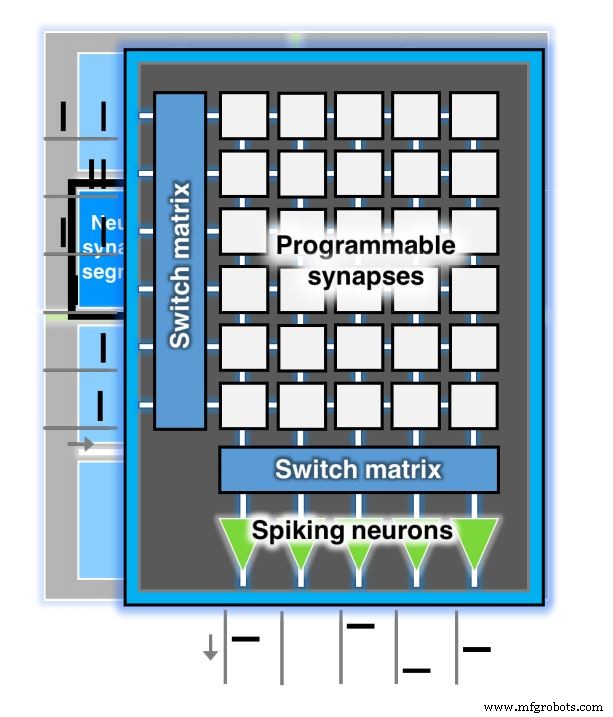

Вычислительный сегмент в массиве Innatera, в котором нейроны тщательно согласованы. Программируемые синапсы организованы в многоуровневую перекрестную структуру. (Черные линии / тире здесь представляют всплески на входе и выходе) (Изображение:Innatera)

Незначительные несоответствия в производстве между вычислительными элементами на кристалле и между разными чипами могут быть проблемой для точной реализации нейронных сетей в аналоговой области. Решение Innatera состоит в том, чтобы сгруппировать нейроны в так называемые сегменты, которые тщательно спроектированы с учетом длины пути и количества нейронов.

Сегментная конструкция «по существу позволяет нам использовать лучшее из аналоговых схем, сводя к минимуму эти неидеальности, которые обычно встречаются в аналоговых схемах», - сказал Кумар. «Все это было сделано для того, чтобы нейроны внутри сегмента демонстрировали детерминированное поведение и функционировали так же, как их непосредственные соседи».

Несоответствие между различными микросхемами может вызвать проблемы, когда одна и та же обученная сеть развертывается на устройствах в полевых условиях. Innatera решает эту проблему с помощью программного обеспечения.

«Несоответствие и вариативность решаются глубоко внутри SDK», - сказал Кумар. «Если вы опытный пользователь, мы можем рассказать вам кое-что из этого, но типичному программисту не нужно об этом беспокоиться».

Для конкретного приложения

Innatera, дочерняя компания Делфтского технологического университета, уже работала с коммерческими клиентами над своими алгоритмами SNN, прежде чем перейти на оборудование и собрать начальный раунд в размере 5 миллионов евро (около 6 миллионов долларов) к концу 2020 года.

«Мы работаем с рядом клиентов с того момента, как мы фактически основали компанию, и эти обязательства все еще продолжаются - они значительно повзрослели», - сказал Кумар. «Мы надеемся, что сможем показать больше демонстраций вместе с некоторыми из этих клиентов в конце этого года».

Кумар сказал, что компания по-прежнему специализируется на вычислительных решениях, то есть будет поставлять готовые решения, включающие как аппаратное обеспечение, так и алгоритмы SNN для конкретных приложений.

Первый чип Innatera подходит для аудио, медицинских и радиолокационных приложений. Дорожная карта компании может включать дополнительные оптимизированные чипы для каждого из приложений.

«Мы спроектировали устройство таким образом, чтобы мы могли ускорять широкий спектр нейронных сетей с пиками», - сказал Кумар. «[Наш чип] может реализовать эти сети в доменах приложений. Но по мере того, как мы углубимся в предметные области, может потребоваться оптимизация конструкции оборудования, и это то, что мы рассмотрим в будущем. В настоящее время оборудование не слишком специализировано для какого-либо определенного класса приложений или какого-либо стиля нейронных сетей с пиками, цель состоит в том, чтобы поддерживать их множество, как правило, внутри архитектуры ».

Образцы первого чипа будут доступны до конца 2021 года.

>> Эта статья изначально была опубликована на нашем дочернем сайте EE Times.

Связанное содержание:

- ИИ-чип предназначен для периферийных устройств с низким энергопотреблением.

- Цепочка инструментов и сенсорная плата улучшают экосистему ИИ-чипов.

- Новые модули ускорения ИИ повышают производительность периферийных устройств.

- ИИ на пороге:на что обращать внимание в 2021 году

- Как реализовать искусственный интеллект вещей (AIoT) на микроконтроллерах

Чтобы получить больше информации о Embedded, подпишитесь на еженедельную рассылку Embedded по электронной почте.

Встроенный

- Совместное моделирование для проектов на основе Zynq

- Renesas:автомобильные чипы, принятые Nissan для своего нового Skyline ProPILOT 2.0

- CEVA:AI-процессор второго поколения для глубоких рабочих нагрузок нейронных сетей

- Обоснование использования нейроморфных чипов для вычислений ИИ

- Радиолокационный чип с низким энергопотреблением использует нейронные сети с пиками

- Lanner:граничный шлюз с поддержкой LTE, сертифицированный для IoT и SD-WAN в сотовых сетях

- IBM на SPIE:семь достижений в области создания микросхем, превышающих 7 нм

- NPE - дебют в США для робототехнического центра Campetella

- 3G мертв:что дальше для дизайнеров продуктов?

- LoRaWAN временно заменит сети 5G для Интернета вещей